一.Steppingstone

我们知道nand没有独立地址线,cpu无法直接访问nand上的指令,所以nand不能片上执行。那么为何程序还能支持nand启动的呢?

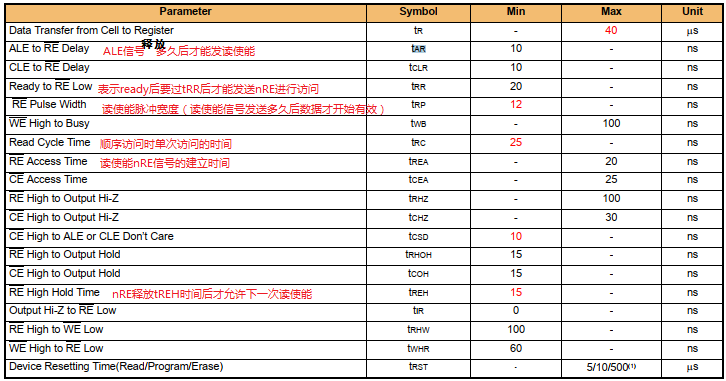

为了支持NAND启动,S3C2440A配备了一个称为“ Steppingstone”的内部SRAM缓冲区,容量为4K。 开机时,Nandflash中的前4K数据将被加载到Steppingstone中,而引导代码将被加载到SRAM中将被执行,如下图所示:

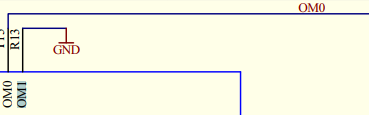

我们知道s3c2440支持2种boot方式,nand或者nor,那么需要配置OM引脚来设置引导方式,如下图:

内存控制器的地址映射表如下:

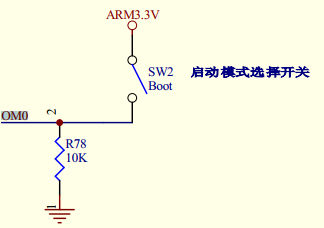

我们得知OM1接地,OM0接了一个开关SW2,那么我们的OM0的电平状态由SW2开关决定:

当SW2闭合,OM0=1, OM[1:0]=01, 0地址对应nor,那么从nor启动。

当SW2断开,OM0=0, OM[1:0]=00, 0地址对应bootSRAM(4K),那么0地址对应该SRAM, 那么从nand启动。

二.引脚配置

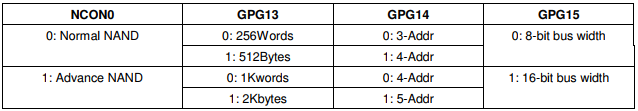

当上电启动时,NAND Flash 控制器将通过下面的引脚配置来获取连接的 NAND Flash 的信息。

NCON:NAND Flash 存储器选择(普通/先进)

0:普通 NAND Flash(256 字或 512 字节页大小,3 或 4 个地址周期)

1:先进 NAND Flash(1K 字或 2K 字节页大小,4 或 5 个地址周期)

GPG13:NAND Flash 存储器page size选择

0:页=256 字(NCON=0)或页=1K 字(NCON=1)

1:页=512 字节(NCON=0)或页=2K 字节(NCON=1)

GPG14:NAND Flash 存储器地址周期选择

0:3 个地址周期(NCON=0)或 4 个地址周期(NCON=1)

1:4 个地址周期(NCON=0)或 5 个地址周期(NCON=1)

GPG15:NAND Flash 存储器总线宽度选择

0:8 位宽度

1:16 位宽度

如下表所示更直观:

三.nand控制器时序配置(nand访问原理)

nandflash访问时需要遵循一定的时序才能完成命令、地址、数据的发送。nandflash有8bit位宽数据总线,那么没有地址线它是怎么和cpu通信的呢?

1.nandflash是DATA0~DATA7上既传输数据,又传输地址,又传输命令;

①当ALE为高电平时传输的是地址;

②当CLE为高电平时传输的是命令;

③当ALE,CLE都为低电平表示传输的是数据

2. 先发送片选CS和WE/RE信号

3. 再发送CLE

4. 再发送ALE

5. 最后发送数据

下面分别介绍命令、地址、数据的发送过程。

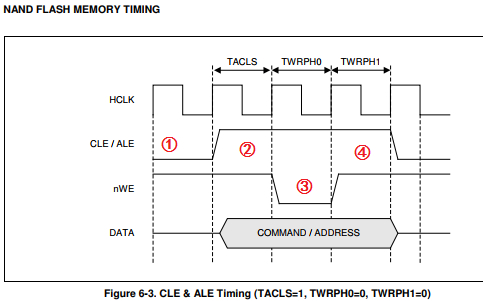

1.命令/地址锁存时序

1)首先看时钟,nand控制器的时钟源采用的是HCLK, 也就是AHB高速总线模式,可以参考s3c2440裸机-时钟编程(一、2440时钟体系介绍)那么HCLK=100Mhz, T=1/HCLK=10ns。

2)从上图可知命令、地址锁存的时序是一样的,复用一个时序图,当到达①的位置时,CLE/ALE=0;

3)当到达位置②时,CLE/ALE=1,表示命令/地址信号拉高,命令/地址开始使能,然后往数据总线DATA上放入命令或地址;

4)经过TACLS时间,到达位置③时,拉低nWE引脚,这时数据总线DATA上的命令/地址开始被锁存,锁存需要一定的时间,所以经过TWRPH0时间后,数据总线DATA上的命令/地址锁存完成;

5)到达位置④,此时释放nWE信号,nWE=1,这时还需要经过TWRPH1时间后,释放CLE/ALE,此时一个完整的命令/地址锁存过程完成。

上面分析了命令/地址的锁存时序过程,下面详细解释下上面几个时间参数的含义:

TACLS:CLE/ALE使能信号发送多久后才可以发送nWE信号 TWRPH0:nWE信号发送多久后数据(commamd/addr)才会被锁存成功 TWRPH1:nWE信号释放多久后才能释放CLE/ALE

那么这些时间参数要怎么配置呢?

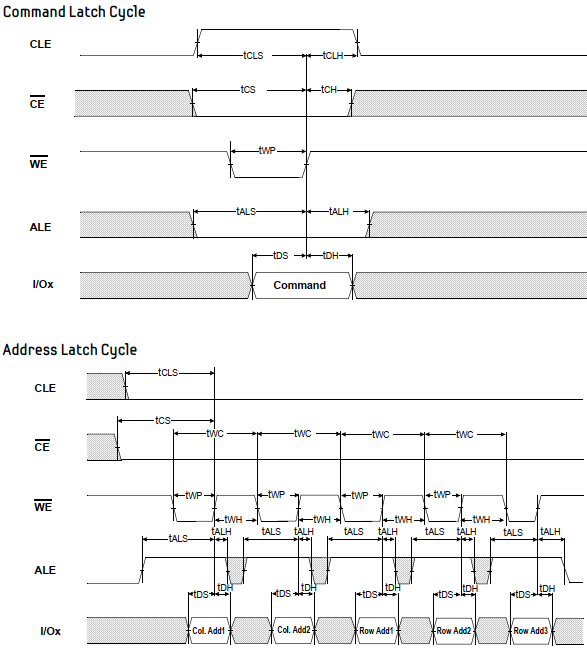

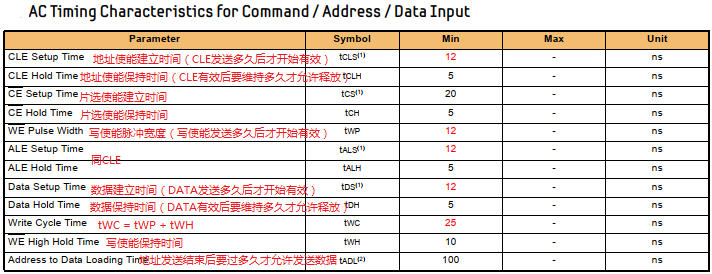

这个需要根据我们实际使用的具体nandflash型号和性能来配置我们的nand控制器。我们以K9F2G08U0C这款nandflash为例进行讲解,手册上命令和地址锁存周期如下:

和nand控制器的命令/地址锁存时序图对比发现:

TACLS = max(tCLS,tALS) - tWP;TWRPH0 = tWP;TWRPH0 = max(tCLH,tALH);

我们知道2440 nand控制器把命令、地址锁存时序复用成了一个时序图,其实命令和地址锁存时序参数基本一致,只不过发命令只需要一个周期就OK了,发地址需要5个时钟周期,为什么?

你想,命令多简单,无非就是读写擦,像我们这款nand数据位宽8bit,一个周期绰绰有余。但地址就不一样了,比如此款nandflash容量256M = 2^28,那么需要28根数据线来传输才能一个周期传输完,但这款nandflash的数据总线位宽只有8bit, 只有8根数据线,所以需要把地址拆分成多次发送,先发送col地址,再发送row地址,此款nandflash是用了5个周期发送地址。

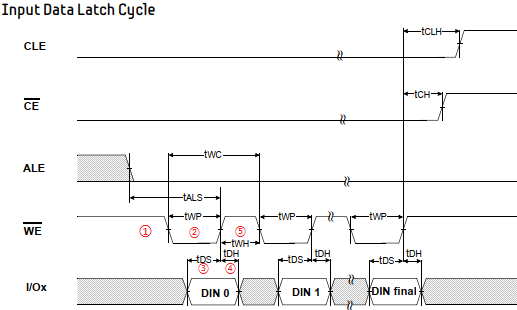

2.数据锁存时序(写数据)

从前面的命令地址锁存时序图中我们得知,CLE信号拉高,ALE信号拉低时,表示发送的命令;当CLE信号拉低,ALE信号拉高时,表示发送的地址;那么当CLE、ALE都拉低时,表示发送的数据,如下图,nCE, CLE, ALE都拉低了,表示传输的是数据。

1)当到达①时,nWE还是高电平,写使能没有开启;

2)当到达②,③时,那么经过了tWP时间(TDS时间),数据开始被锁存;

3)到达④,经过tDH时间,数据锁存完成;

4)到达⑤,也就是数据开始锁存后再过了tWH时间后释放nWE信号;

5)重复②③④⑤过程。

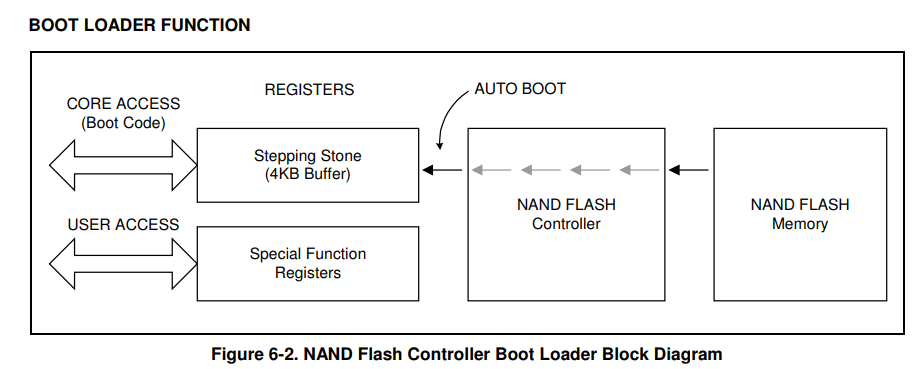

根据上面这三个图(手册上的命令、地址、数据锁存时序图),下面详细解释各个时间参数的含义:

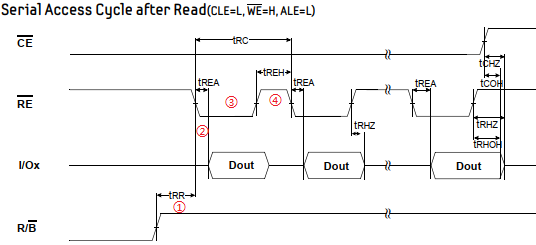

3.顺序访问周期(读数据)

1)①处,表示要过tRR后才能发送读使能信号nRE进行访问(上一次的访问结束后,需要等待ready状态稳定后才可以进行下一次访问);

2)当到达②,需要经过rREA时间后nRE信号才有效(待nRE稳定);

3)当到达③,DATA总线上的读取被读取;

4)当到达④,nRE释放tREH时间后才允许下一次读使能

我们看到连续顺序访问时,单次访问的时间为tRC,那么这些时间参数的值也可以从K9F2G08U0C datasheet中找到:为25ns