1.ARM的体系与架构

1.1.ARM体系的CPU有以下其中工作模式:

用户模式 (usr)

快速中断模式 (fiq)

中断模式 (irq)

管理模式 (svc)

数据访问终止模式 (abt)

系统模式 (sys)

未定义指令终止模式 (und)

1.2.ARM寄存器:

31个通用寄存器 : R0~R7(未备份寄存器) , R8~R14(备份寄存器) , R15( 程序计数器PC )

6个状态寄存器 : CPSR( 当前程序状态寄存器) , SPSR(备份程序状态寄存器)

2.ARM状态下当异常发生时, 处理器将切换进相应的模式:

2.1. 当异常发生时, 处理器将自动完成以下事情 :

在异常工作模式的连接寄存器R14中保存前一个工作模式的下一条指令(即将执行)的地址,

对于ARM状态, 这个值是当前PC值加4或者加8

将CPSR的值复制到异常模式的SPSR

将CPSR的工作模式位设为这个异常对应的工作模式

令PC值等于这个异常模式在异常向量表中的地址 , 即跳转到异常向量表中执行对应的指令

2.2. 当从异常模式返回到之前的工作模式时, 则需软件完成以下工作 :

进入异常时, R14保存了前一个工作模式的下一个指令地址 ,所以要将他减去一个适当的值

将SPSR的值复制回CPSR

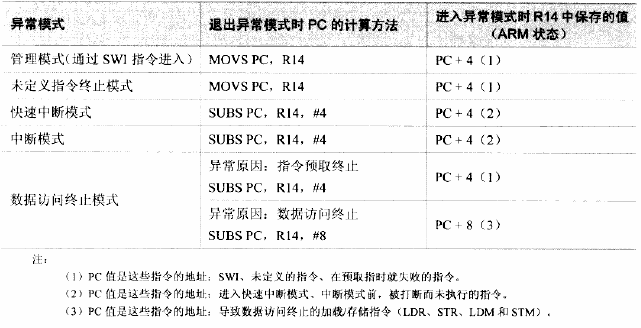

2.3. 关于R14在发生异常时保存的地址参考表:

3. 使用中断的步骤 :

3.1. 设置好中断模式和快速中断模式下的栈 , 它们分别使用自己的栈

3.2. 准备好中断处理函数 :

异常向量地址 : irq(0x00000018) , fiq(0x0000001c)

中断服务程序(isr) : 对于irq,通过判断INTPND或者INTOFFSET来确定中断源, fiq只有一个中断

清除中断 : 如果不清除中断会让CPU误以为中断又一次发生了

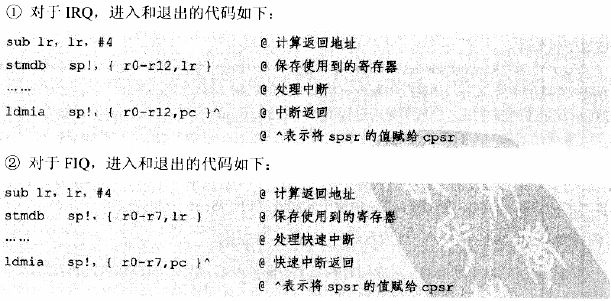

3.3. 进入、退出中断或快速中断时, 需要保存、回复中断的运行环境

3.4. 设置中断涉及到的寄存器 .

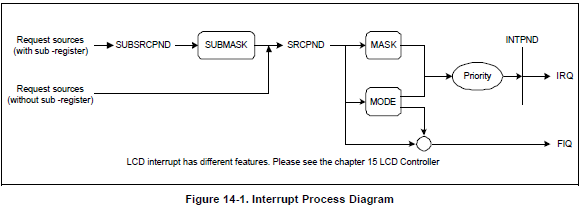

3.4.1. 外部中断被分为被SUBSRCPND/SUBMASK寄存器控制的中断,不被

SUBSRCPND/SUBMASK寄存器控制的中断.

3.4.2. 外部中断必须经过SRCPND( SOURCE PENDING)寄存器的控制

3.4.3. 外部中断最终经过INTMASK(中断屏蔽)与INTMODE(中断模式)寄存器

的控制

3.4.4. 外部中断经过PRIORITY(优先级寄存器)的仲裁决定优先级

3.4.5. 通过INTPND寄存器来确认中断的发生以及清除中断 ,同一时间内只有一位

被置一

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服