硬件工程师实际设计时面临的问题、考虑的因素比这里列出的多得多。罗马不是一天建成的,所以需要日积月累的。

异常情况的思考

1、电流倒灌

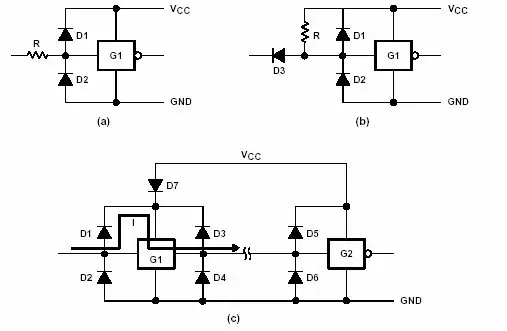

集成电路的典型模型如下:

1、 D1在大多数CMOS集成电路中起着防静电功能.同时辅助起着输入端限幅作用。但是在ABT,LVT,LVC和AHC/AHCT类集成电路中无此二极管。

2、D2是半导体集成所产生的寄生二极管(存在于所有数字集成电路),其辅助功能为对线路反射的下冲信号进行限幅,提供一些放电保护功能。

3、D3用于保护CMOS电路在放电时的干扰。在大多数双极性器件中也存在此二极管,但为寄生二极管。在集电极开路和三态输出的双极性器件中无此二极管。

4、D4在所有集成电路中均存在此二极管。它是器件的集电极或漏极的二极管。在双极性器件中还附加了一个肖特基二极管对线路反射的下冲信号进行限幅。在CMOS电路中附加了二极管以增加防静电功能。

电流倒灌产生的原因:

当使用CMOS型器件作为接口芯片在如下图所示的电路中使用时,如果Vcc2断电,Vcc1继续供给G1,G1的高电平输出电流将通过D1向Vcc2上的电容充电(该充电电流将使D1迅速过载并使其损坏。CMOS器件中D1只能承受20mA的电流)并在Vcc2上建立一电压,该电压使使用Vcc2供电的其它电路工作不正常,特别使可编程器件。

解决措施:

如图(a):在信号线上加一个几欧姆的限流电阻,可防止过流损坏二极管D1,但不能解决灌流在Vcc上建立电压;

如图(b):在信号线上加二极管D3及上拉电阻R,D3用于阻断灌流通路,R解决前级输出高电平时使G1的输入保持高电平。此方法即可解决灌流损坏二极管D1的问题,又可解决灌流在Vcc上建立电压。缺点是二极管D3的加入降低了G1的低电平噪声容限;

如图(c):在G1的电源上增加二极管D7。缺点是前级输出高电平时,G1通过D1获得电压并从输出高电平给后级电路。同时降低了G1的供电电压,使其在正常使用时高电平输出电压降低。

最有效的解决方法是使用双极型的器件(如LS器件,ABT器件)作为接口,由于双极型器件没有保护二极管D1存在,故不存在上述灌流通路。需要注意的是这时接口的输入、输出信号线上不能加上拉电阻(双极型器件输入悬空当高电平对待)。

2、 热插拔设计

Ø 热插拔对电源的影响

电路板上电或热插拔时会从电源拉出很大的启动电流并导致电源电压的波动,此现象控制不当将影响系统中其它电路的正常使用,甚至导致整个系统的损坏。

热插拔电路的最低要求是提供浪涌电流限制,防止在大的容性负载加电时整个系统损坏。限流功能还有助于减小供电电源的尺寸,并防止在连接器接触时产生电弧。其它热插拔特性还包括:低等效串联电阻、断路器、状态指示、双插入点检测和电源就绪指示。

目前我公司的产品除个别处理机对电源采取上电限流措施外,其余电路板使用PTC对负载过流进行限制,但没有上电限流措施。

最简单的限流元件是保险丝,它可以单独使用或与其它保护元件配合使用,由于保险丝可以有效地防止过流的冲击,它们在系统中既是必须的(如UL 标准的规定),也是系统遇到灾难性故障时的最终防线。标准保险丝的主要缺陷是只能一次性使用,另外一种可替代的小型器件是多重保险丝,这种保险丝的物理尺寸可以根据流过其自身电流所产生的热量而膨胀或缩短,多重保险丝的工作电压范围受温度的限制,但它能够自复位,这是相对于标准保险丝的最大优点。

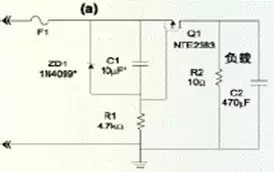

普通热插拔电路由电容、齐纳管和FET 构成,如下图所示。通过对连接在Q1 栅、源极之间的电容C1 充电达到限制浪涌电流的目的。如果上电期间C1 放电,Q1 的栅极与源极相当于短路,Q1 将维持开路。C1 充电时,Vgs增大,Q1 缓慢开启。C1 的大小和Q1 的Vgs指标确定了Q1 的开启时间和负载电容C2 的充电时间。齐纳管ZD1 用于防止栅-源电压超出其最大额定值。

Ø 接口IC的热插拔

电路板上电或热插拔时如果处理不当,会通过信号线对系统中的其它电路板的正常使用造成影响,也可能造成接口IC的软损伤或硬损坏。所以在系统及电路板设计时应尽量满足以下要求:

电路板在热插拔时必须保证地端子首先连接,这是电路板正常工作的基础。在多电源系统,特别是有负电源同时使用的系统中,如果热插拔时不能保证电路板的地端子首先连接,则应尽量不在电路板的负电源上使用大容量的电容,因为在此情况下可能使电路板的地电位偏离到负电位,使接口IC的输入、输出管脚对地电压超过其耐受范围,造成接口IC管脚的损坏。

1、使用输入或输出端不带对电源保护二极管的IC;

2、使用具有上电三态功能的IC。

正确的电路板上电次序应为:

首先连接电路板的地;

其次连接电路板的电源;

连接电路板的复位端子;

最后连接电路板的信号端子;

3、 过流保护

过流保护技术在电源设计中使用较普遍,在电路板设计中可以借鉴。由于器件工作不正常或故障损坏等原因可能造成电路板电源过流,对此如果不加以限制可能给系统带来灾难性后果。

在电路板的电源入口处串联小阻值的PTC元件可对电源进行有效保护,当电路板产生过流时,流过PTC的电流增大,使PTC温度升高,同时其阻值增大,限制电流的进一步增加,使进入电路板内的电流限制在一个较小的范围内,对电路板可有效起到保护作用,同时不至于影响其它电路板的正常工作。使用PTC的另一个优点是可重复性,当过流条件不存在后,PTC的温度下降,阻值回到常态,不影响其正常使用。

选择PTC时需要注意其耐压、不动作电流及静态电阻和动作时间。

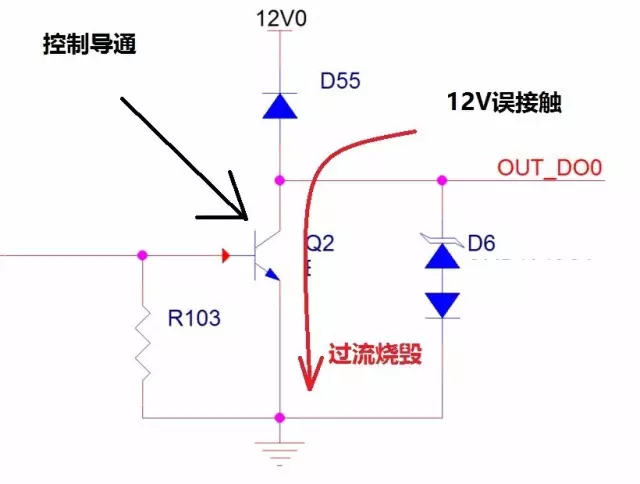

案例:我们OC的输出,控制电磁阀。电磁阀一端接12V,一端接OC输出。但是在安装过程中,时常出现:由于施工不小心,OC直接与12V短路,导致三极管、或者MOS管,直接失效,导致现场大量三极管烧毁。

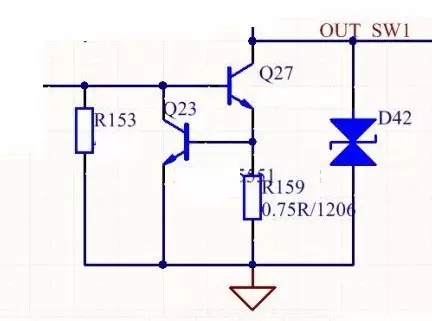

经过优化,可以通过下面电路,预防过流,导致三极管损毁。

高速信号设计的思考

4、信号完整性

电信号(电流、电压信号)在沿导线传输的过程中,由于分布电感、电容和电阻的存在,导线上各点的电信号并不能马上建立,而是有一定的滞后,离信号源越远,电压波和电流波到达的时间越晚。当导线的阻抗有变化(如背板线与电路板内的信号线、接插件等)或负载阻抗与线路阻抗不匹配时,将对电信号产生反射和折射。

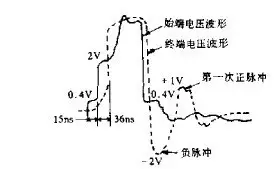

如下图所示,由于反射波的存在,始端输入信号并不是理想的阶跃电压,而是具有一定前沿时间的脉冲信号。

上图中信号的宽度大于信号的传输延迟(36nS),若信号宽度小于信号的传输延迟,信号将不能传输到终点,系统将失控。

最大匹配线长度计算:

方法1:

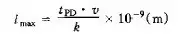

定义:信号在传输线上的反射波的振荡过程如果在芯片的传输延迟时间内,反射波将不影响芯片的工作,将信号在传输时间内所传播的距离称作最大匹配线长度,当传输线超过匹配长度时,称为长线传输,此时需要考虑采取措施抑制反射波干扰。

lmax的长度表示为:

式中:tPD――数字电路的传输延迟时间(ns)

V――电磁波速度,(1.4~2)×108m/s

K――经验常数,取k=4~5

例如,取k=4,v=2×108m/s,求得下面几组最大匹配线长度:

|

数字电路的传输延迟时间tPD(ns) |

最大匹配线长度lmax(m) |

|

50 |

2.5 |

|

40 |

2.0 |

|

30 |

1.5 |

|

25 |

1.25 |

|

20 |

1 |

|

15 |

75cm |

|

10 |

50cm |

|

5 |

25cm |

|

1 |

5cm |

对于TTL系列电路而言,其动作时间为5~10ns,CMOS系列电路的动作时间为25~50ns,HC系列电路的动作时间与TTL系列相仿。系统中往往是多种系列器件混合使用,故应以TTL系列器件对应的lmax为准。所以传输线长度lmax可取25cm。也就是说,当传输线长度超过25cm时,应采取抑制反射波干扰措施。

方法2:

定义:如果信号在传输线上往返一次的时间比信号的上升时间短,则认为该传输线不匹配也不会对信号产生影响。

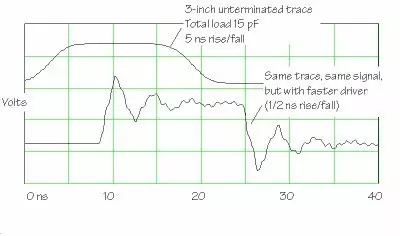

如下图所示,就同一条线路而言,具有不同上升时间(下降时间)的数字电路驱动相同的负载(3英寸长的无匹配信号线,负载电容15pF),其输出信号的波形大不相同。上一个波形表示1986年生产的驱动器的(上升/下降时间为5ns)输出波形,波形很好,可以使用;下一个波形表示1996年生产的驱动器(上升/下降时间为1/2ns)的输出波形,波形很差,不能使用。

《High Speed Digital Design》一书中推荐的最大传输线计算公式如下

lmax=(V×tr/6)×10-9(m)

式中:V:电磁波传播速度(3×108m/s);

tr:信号上升时间,即从10%上升到90%的时间(ns);

注:该计算公式与数字电路的传输延迟时间无关。并且将信号在传输线上往返一次的时间限制在信号上升时间的1/3内。

例如:设一器件的tr为10ns,则当其驱动的信号线长度大于50cm时就需要当长线传输来对待;而对一个tr为1ns的器件,则当其驱动的信号线长度大于5cm时就需要当长线传输来对待。

需要注意的是:两种长线的计算方式都与信号的频率无关

信号在传输线上的反射情况分析:

根据电压反射系数的定义有

Fv=(Z2-Z1)/(Z2+Z1)

当传输线特性阻抗Z1与负载阻抗Z2相等(匹配)时,电压反射系数为零,即此时不会发生反射;

当Z2<Z1时,电压反射系数为负值,即反射电压为负,随着反射的进行,电压迅速达到平衡状态。特殊情况Z2=0,反射系数Fv=-1,电压反射一次后终端电压即达到零状态。由此可见,降低负载电阻由助于消弱反射干扰;

当Z2>Z1时,电压反射系数为正值,即反射电压为正。特殊情况Z2=∞,即负载处于开路,反射系数Fv=1,这样,反射过程将是一个持续的振荡过程。由此可见,当负载电阻很大时,对抑制反射干扰十分不利。

CMOS系列或HC系列器件的输入阻抗很高,在使用中除容易引起静电干扰外,还容易传输反射波干扰,因此在长线传输使用时需要注意采取相应措施如输入引脚对电源或地接入负载电阻以降低输入阻抗;或者直接采用长线驱动型器件。

常用的抑制或削弱反射波干扰的方法有:

1、阻抗匹配:

根据反射理论,当传输线的特性阻抗与负载电阻相等时,反射将不会发生。

即阻抗不匹配是造成信号在传输线上反射的原因。实际的电路实现中阻抗不匹配是绝对的,而匹配是相对的。