了解输出电压范围的特性和限制。

本文引用地址:,或“”,是大量模拟设计的基础。正如我们在上一篇文章中了解到的那样,所有实际的运算放大器都对输入信号的允许电压范围(输入)和输出信号的可用电压范围(输出)进行了限制。之前,我们讨论了输入摆幅规格,包括如何解释它们以及如果超出它们会发生什么。在本文中,我们将关注输出电压范围。

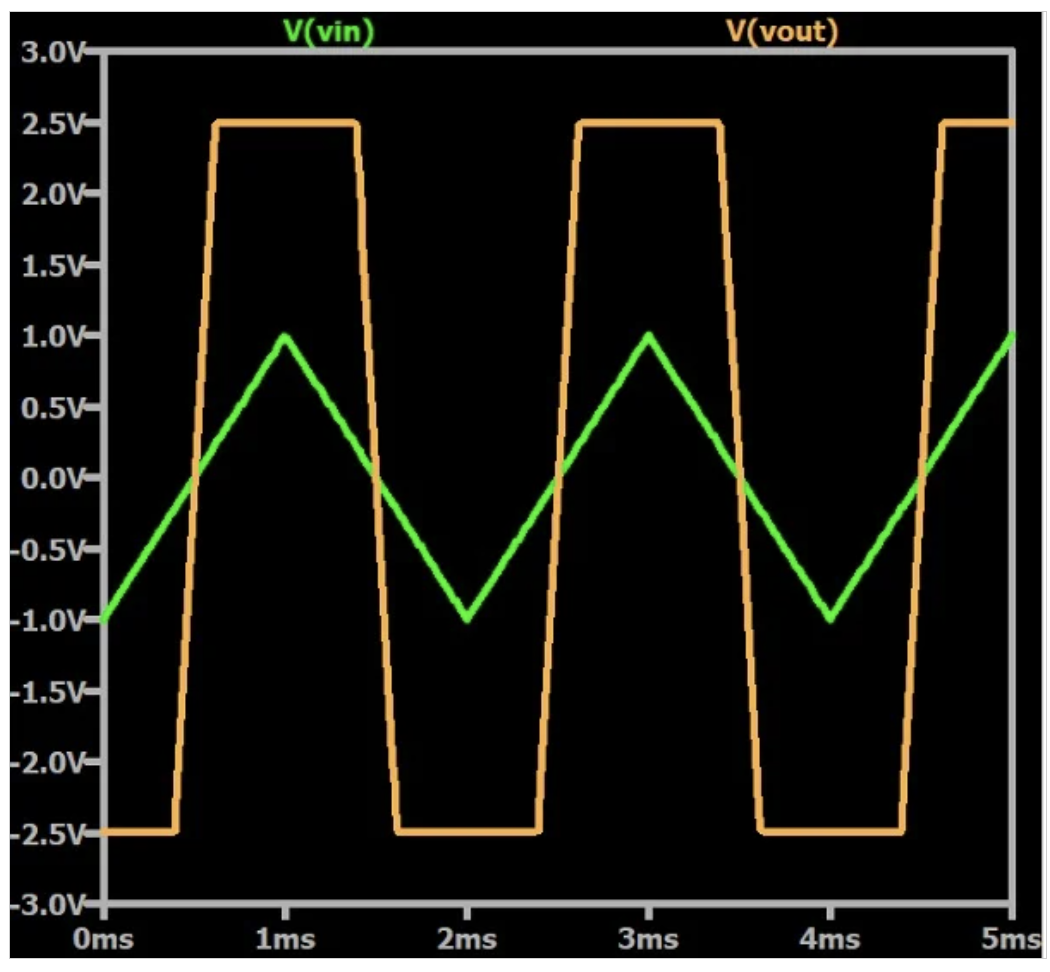

输出电压规格表示输出信号达到其饱和极限的点,这意味着电压不能更接近电源轨。然后,信号被称为“削波”。信号削波的示例如图1所示,图1描述了当由2.5伏和–2.5伏供电时LT1880运算放大器的模拟输出饱和度。

运算放大器输出饱和产生削波信号。

•图1。运算放大器输出饱和度产生一个削波信号。图片由提供

饱和导致输入波形和输出波形之间完全失去对应关系。然而,即使在达到饱和点之前,输出振荡性能也会降低。当输出信号接近数据表中规定的极限时,要求非常低失真的应用可能会受到细微非线性的负面影响。如果不能使用模拟或实验室测试来验证失真性能是否可接受,那么假设输出信号需要与饱和度极限保持几百毫伏的距离是一个好主意。

与输入电压范围一样,输出电压范围取决于运算放大器的电源电压,并与较高电压(V+)和较低电压(V-)的电源轨相关。在下一部分中,我们将仔细研究这些规范。

阅读数据表

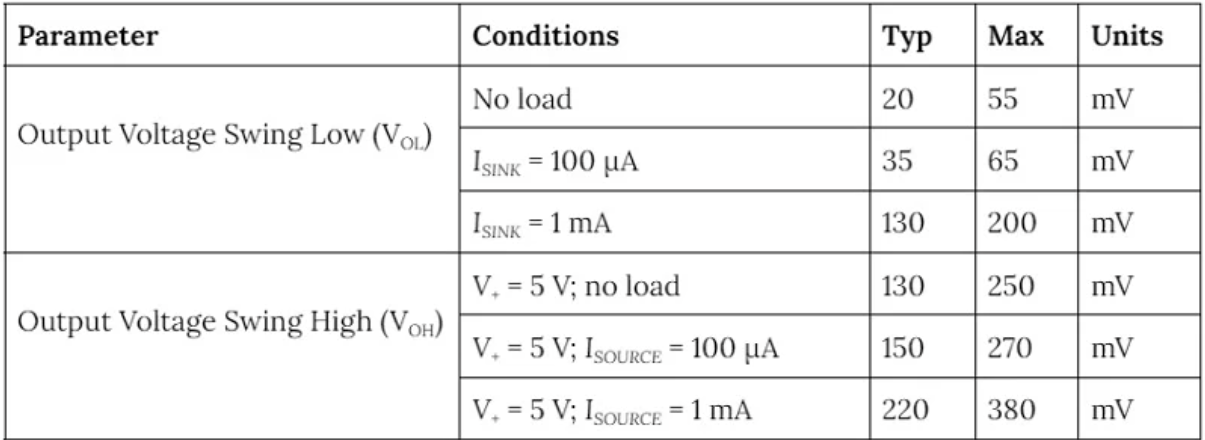

表1给出了模拟设备LT1880的输出摆幅规格,与我们上面模拟的性能相同。Analog Devices将这种运算放大器描述为提供轨对轨输出摆幅。

•表1。LT的输出振荡。数据由Analog Devices提供

模拟设备LT1880运算放大器的输出规格。

阅读本表时,请牢记以下内容:

VOL值表示相对于V型供电轨的摆幅(0V)。VOH同样与V+相关。

“典型”和“最大”栏不描述典型和最大输出电压,而是描述输出电压偏差。

仅给出偏差量,不给出方向。

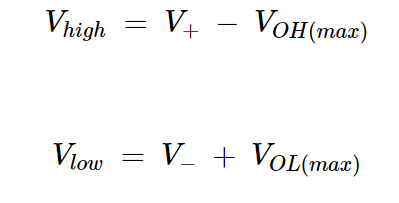

以下两个方程式分别表示规定输出电压范围的上限和下限:

这些方程式提醒我们,制造商使用“轨对轨”这一术语时有点过于宽松。即使在没有负载电流的情况下,输出也不能一直振荡到任何一个电压轨,并且随着输出电流的增加,间隙大幅扩大。在本文的后面,我们将详细讨论输出电流对可用输出摆幅的影响。现在,让我们来看数据表的不同部分。

输出摆幅图

在描述输出摆幅限制时,数据表规格表仅使用少数负载电流条件实例。通过检查数据表中的性能图,我们可以更完整地了解运算放大器的输出振荡能力。

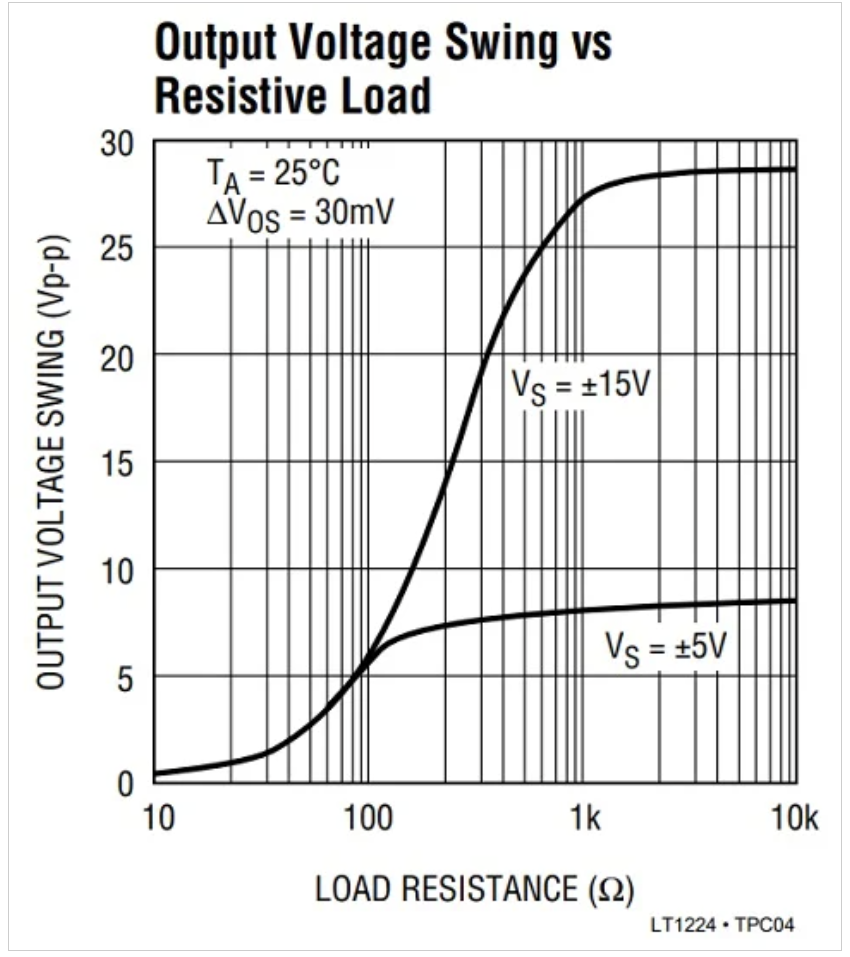

这些信息的准确报告方式在装置之间有所不同。例如,图2和图3分别描绘了来自模拟设备的两个不同运算放大器LT1224和LT6023的输出摆幅特性。

LT1224的输出电压摆幅与负载电阻。

•图2。LT1224的输出电压摆幅与负载电阻。图像由Analog Devices提供

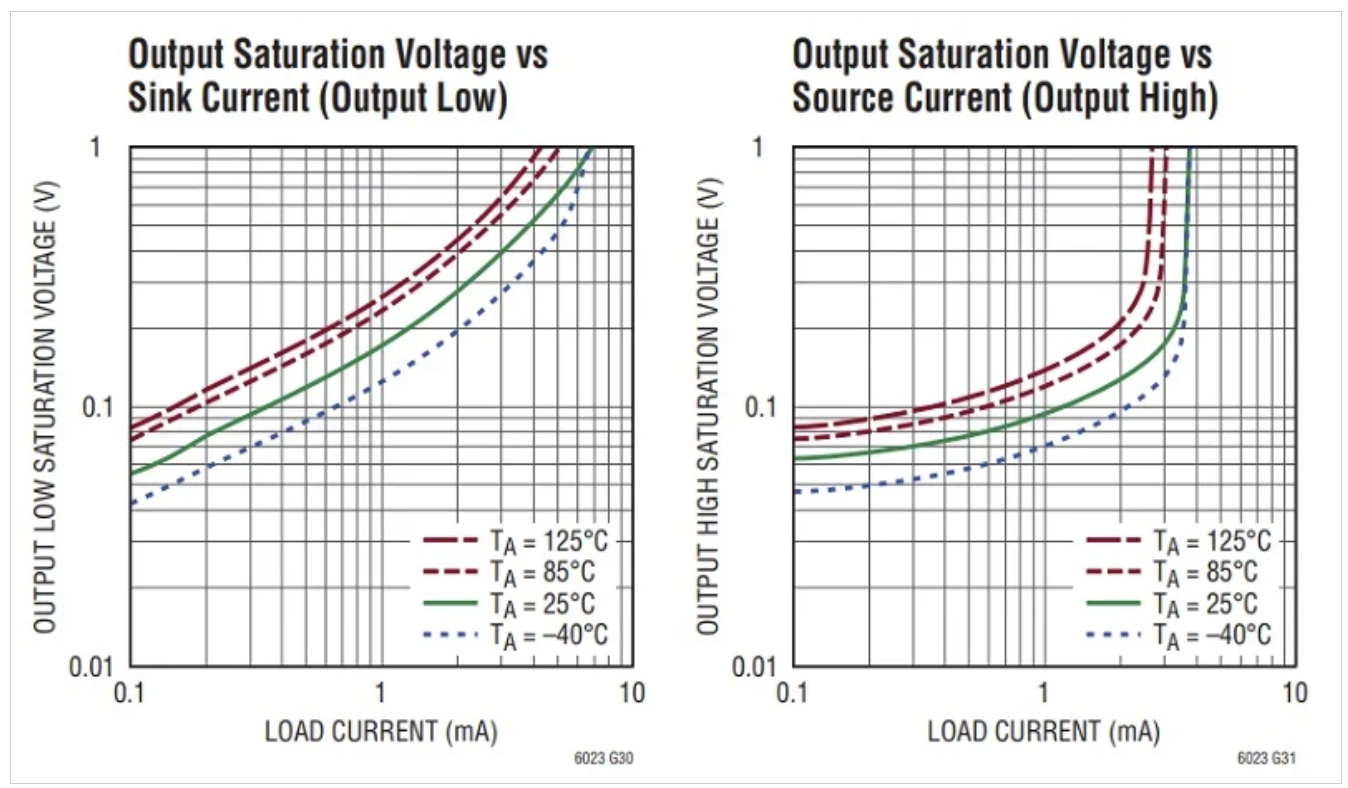

LT6023的输出饱和电压与负载电流。

•图3。LT6023的输出饱和电压与负载电流。图像由Analog Devices提供

LT1224的数据表报告了相对于负载电阻的峰-峰值电压振荡。相反,LT6023的数据表报告了“饱和电压”,这似乎是饱和极限和电源电压之间的差异,代替了电压振荡。它也使用电流而不是电阻作为自变量。

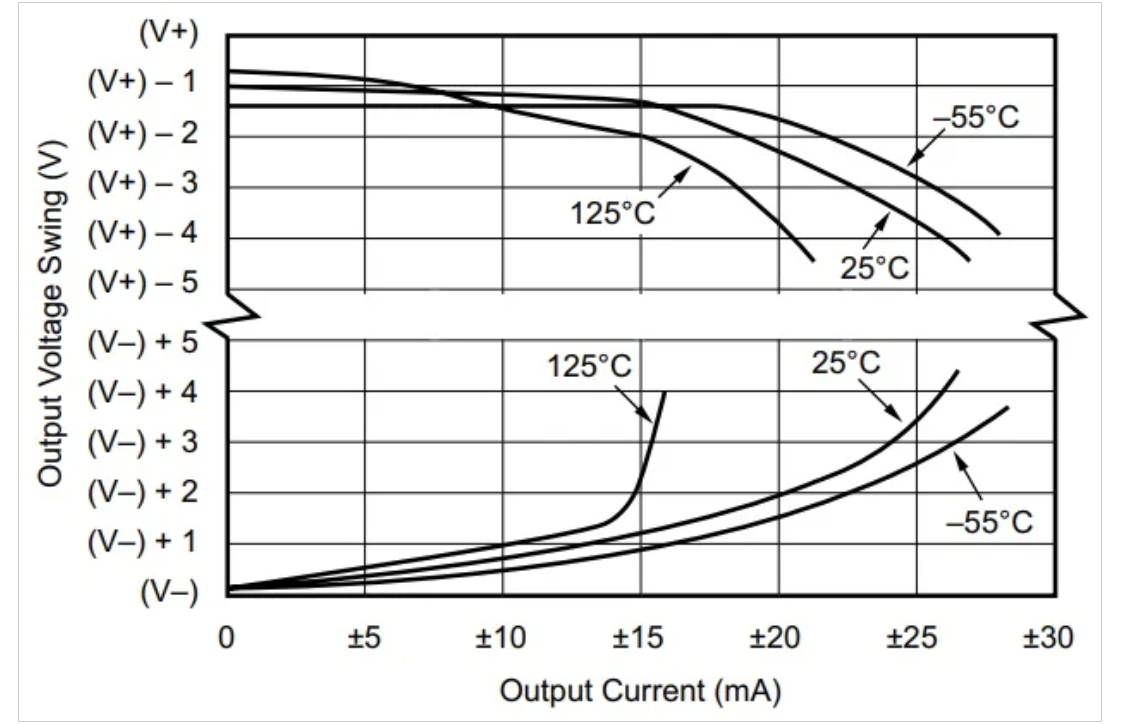

图4取自得克萨斯仪器公司OPA277数据表,使用不同的视觉格式绘制电压摆幅与电流的关系。我个人认为它清晰简洁。

OPA277的输出电压振荡与输出电流。

•图4。OPA277的输出电压振荡与输出电流。图片由Texas Instruments提供

输出摆幅与负载电流

正如我们在数据表摘录中所研究的那样,输出波形可用的电压范围并不是一个在所有操作条件下都有效的单一规范。相反,它受到运算放大器产生或下沉的电流量的显著影响。随着更多的电流流过输出端子,连接在运算放大器的功率节点及其输出节点之间的半导体组件上的电压降得更多。

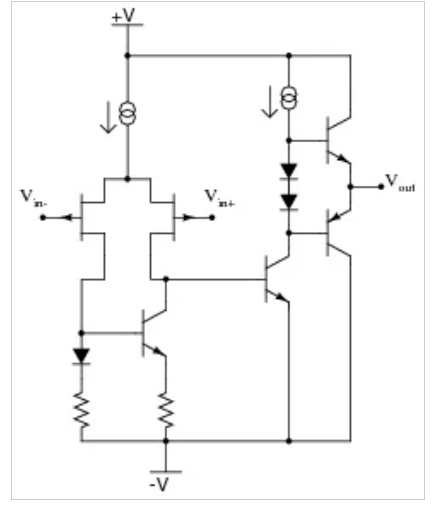

负载阻抗和输出范围之间的关系根据用于输出级的半导体技术而不同。例如,图5显示了用于TL08x集成电路中的运算放大器的简化示意图。输入级采用场晶体管;。

TL08x集成电路内部使用的运算放大器的简化示意图。

•图5。TL运算的简化示意图。图片由Tony R.Kuphalt提供

双极输出级通常需要至少200 mV的双极结型晶体管的近似饱和电压——在输出电压和供电轨之间。CMOS输出级可以提供低得多的漏极到源极电压,但是其负载电流依赖性更严重。这是因为,NMOS或PMOS晶体管的沟道起到了电阻器的作用,随着负载电流的增加而降低越来越多的电压。双极晶体管的饱和电压不是由电阻工作模式产生的,所以它相对于输出电流是相对稳定的。

总结

运算放大器是多功能组件,通常可以在不需要复杂模拟或通过长途跋涉的查阅数据手册即可实现。然而,有时运算放大器的非理想行为会显著影响性能。因此,我们需要在设计过程中研究和解决这些问题。我希望本系列能够帮助您了解一些管理运算放大器输入和输出信号的要点。

相关文章

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服