硬件辅助验证产品解读之FPGA原型验证系统VS硬件仿真器

本文将会对FPGA原型验证系统和Emulator硬件仿真器进行全面的分析和比较。

先简要的回顾一下FPGA原型验证系统的应用场景,并与Emulator硬件仿真器应用场景作对比:

FPGA原型验证系统

本文将会对FPGA原型验证系统和Emulator硬件仿真器进行全面的分析和比较。

先简要的回顾一下FPGA原型验证系统的应用场景,并与Emulator硬件仿真器应用场景作对比:

FPGA原型验证系统

FPGA原型验证系统的主要应用场景是“芯片设计过程中搭建软硬件一体的系统验证环境”:一是芯片流片回来前为软件团队提供调试驱动软件的平台,加速芯片上市时间;二是作为芯片仿真验证的一个补充,因为在FPGA内部可以生成真实电路,并且可以对接真实的硬件子卡,相较仿真使用的软件模型有一定差别,因此可以发现更多隐蔽的bug ;此外FPGA相对软件仿真以及Emulator而言,速度更快,比较适合一些耗时较多的场景case。故在芯片设计规模越来越大的情况下,使用多颗FPGA芯片互联能够快速实现高性能的全系统验证原型,并满足该场景下的调试需求。

Emulator 硬件仿真器

Emulator的主要应用场景是 “芯片设计过程中对完整封闭的设计进行加速仿真并调试”,它与FPGA原型验证系统的主要定位差异在于:能对全芯片进行和芯片时序行为一致的硬件仿真,包括全芯片信号的提取,对全芯片的功能、性能、功耗进行系统级的验证与调试。这一点差别导致了两者系统设计上的巨大差异。用户无需花费大量的时间去考虑如何设计、如何分割、如何布局布线等问题,从而在易用性方面大大增强。基于FPGA原型验证系统平台和 Emulator硬件仿真平台二者的设计目标和应用场景差异,下面我们分别来介绍一下这两种产品的关键点。

FPGA原型验证系统

随着目前集成电路的不断发展,设计规模的大型化,单颗FPGA板在容量上就显得捉襟见肘,已经无法满足设计需求。以目前国内头部的CPU、GPU设计公司的设计规模,单颗IC芯片的设计体量,需要占用到几十颗Xilinx VU440级别FPGA的情况,已屡见不鲜。在这种背景之下,FPGA系统供应厂商开始着手研究多颗FPGA的系统互联解决方案。其中就包括在单块的PCB板上装配多颗FPGA及多个FPGA系统之间的互联。经过不断探索,FPGA原型验证平台产品应运而生。之所以称之为“平台”或“系统”,就一定会包含对应的软件和硬件。首先在硬件结构上多颗FPGA互联结构的引入就要求结构上比单板形式的FPGA开发板要复杂的多,其次FPGA芯片厂商提供的软件工具无法支持多片的FPGA分割,需要配套专业的FPGA原型分割相关软件工具。一套优秀的FPGA原型验证系统,应该具有以下产品特性:

基于模块化的设计,可灵活扩充与裁剪的验证平台规模

在保证一定的高速仿真性能的前提下,提供设计完整性

提供从软件早期开发到系统级验证的解决方案

提供从综合、自动模块分割、布局布线、FPGA bit产生、下载、在线/离线Debug的整套流程

提供丰富的调测手段,帮助用户快速定位问题,易于设计的快速Bring Up

提供丰富的接口子板和外部真实设备相连

提供软件接口与外部工具构成复杂的调试解决方案

提供丰富的IO接口,以及高速Serdes接口用于partition互连以及外设子卡的互连

FPGA原型验证系统速度快,但它的缺点也是显而易见的,主要体现在调试的便利性上继承了FPGA自身的一些缺点,比如需借助FPGA内嵌逻辑分析仪来抓取信号排查问题,布局布线耗时冗长,效率不是太高。

硬件仿真器Emulator

在目前SoC规模越来越大型化的情况下,有的设计甚至达到数百亿ASIC等效门规模,巨大的设计规模导致软件仿真时间上的消耗变得越来越无法忍受。FPGA原型平台在验证规模到达一定级别,FPGA数量太多的情况下,也会带来新的分割问题并且会失去原有的性能优势。硬件仿真器的优势主要在于它独有的、超大规模的硬件结构,尽可能地保证了RTL设计的完整性。从硬件实现上看,一般有基于FPGA和CPU两种架构,对于基于FPGA架构的类型来说(如Synopsys的Zebu系列),可以理解为有很多块FPGA单板,大量的单板与电源、控制等再互相连接起来,形成一个“庞然大物”,优点是仿真性能高,使用商用FPGA可以降低开发成本;对于基于CPU架构的类型来说(如Cadence的Palladium系列),通常会将集成了数以万计的高速CPU核的ASIC芯片焊接在一块巨大的单板上,配以控制、冷却等模块构成一个完整系统。优点在于编译时间短,调试能力强;缺点就是功耗高,需要特别冷却系统和运营成本高,稳定性比较难控制,性能一般也比基于FPGA的硬件仿真系统低些。一般一套Emulator的体积大约从一个冰柜到一台大双开门冰箱的大小,而大型Emulator的重量也可以用“吨”来计算了。本文主要介绍基于FPGA的硬件仿真器。基于FPGA的原型平台和硬件仿真器,两者的架构和软件上虽有一定的相似之处,但定位不同,Emulator的定位和设计都是指向大容量和全系统仿真级调试,因此软硬件设计上有不同的取舍。综合来看,硬件仿真器的特点是支持超大规模(10亿门级以上)的设计容量,全自动化的软件设置实现流程,基本无需修改硬件连接配置,以及灵活多样的全系统仿真调试能力,包括:

信号的追踪深度更深(达数十亿仿真周期)

信号的条件触发、动态探针插入、离线调试

拥有不限量的时钟域,它们可以从核心时钟资源中无限衍生

全系统范围的调试追踪

带有UVM验证方法学的协同加速仿真

软硬件的协同验证、测试接口的虚拟化支持

系统功耗与性能预估、分析

目前,主流的Emulator工作特点,基本上包括以下几种:

基于Cycle级的软硬件联合仿真

基于ICE ( In-Circuit Emulator )模式: 一种最为传统的,理论上运行速度最快的模式。这种模式下需要在硬件中集成被测试逻辑单元及测试逻辑,或者通过外设硬件输入激励;且往往需要用到Speed Adapter以实现外围高速硬件和硬件仿真器在工作频率上的桥接。由于Emulator本身的运行频率不高,那么和外部的设备,如PCIE/SATA/USB等连接时需要通过速度匹配设备,通过缓存来匹配快速端的速度进行适配

基于事务级(Transaction)的软硬件联合仿真;这种情况下,被测试的逻辑部分运行在Emulator的硬件里面;硬件通过一套完整的软件及驱动、物理通道和Host Server实现连接。这种方式下可以使用多样的SW model Library,常见的有PCIE/AMBA bus等。虽然说它的运行速度没有ICE模式快,但是在软件上的功能和方法支持非常丰富。这种方式也被认为是软件Simulator的硬件化

提供丰富多样的虚拟解决方案:包括Virtual Host(Qemu/VDK),Virtual Device(例如基于Chiplet的Die to Die 模型),Virtual memory models(各类协议的存储器模型SDRAM/Flash/SRAM/EEPROM),Transactors(AMBA/PCIe),Hybrid Mode(CPU Models+ DUT in Hardware)

多种模式的探针工作方式:静态探针、动态探针、全景探针和定制探针组等

其次,在多用户的支持方面,Emulator系统可以支持较多的用户同时在线使用,实现资源的灵活调度;而FPGA原型系统目前也有可以支持多用户的场景,但因为产品在时钟资源分配等方面存在着局限性,所以实际很少采用。

总 结

最后,我们再来看一下FPGA原型验证系统和硬件仿真器Emulator之间的对比表格:

图1:FPGA原型验证系统和硬件仿真器Emulator之间的对比

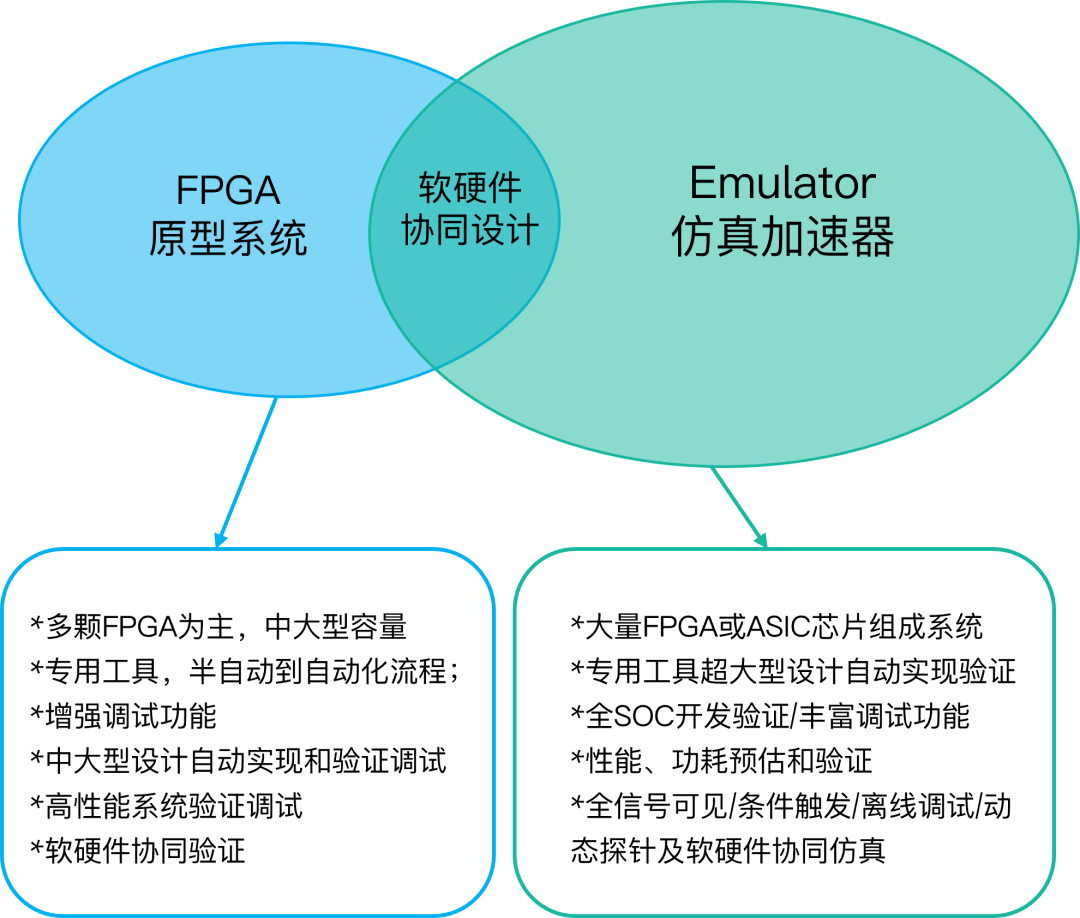

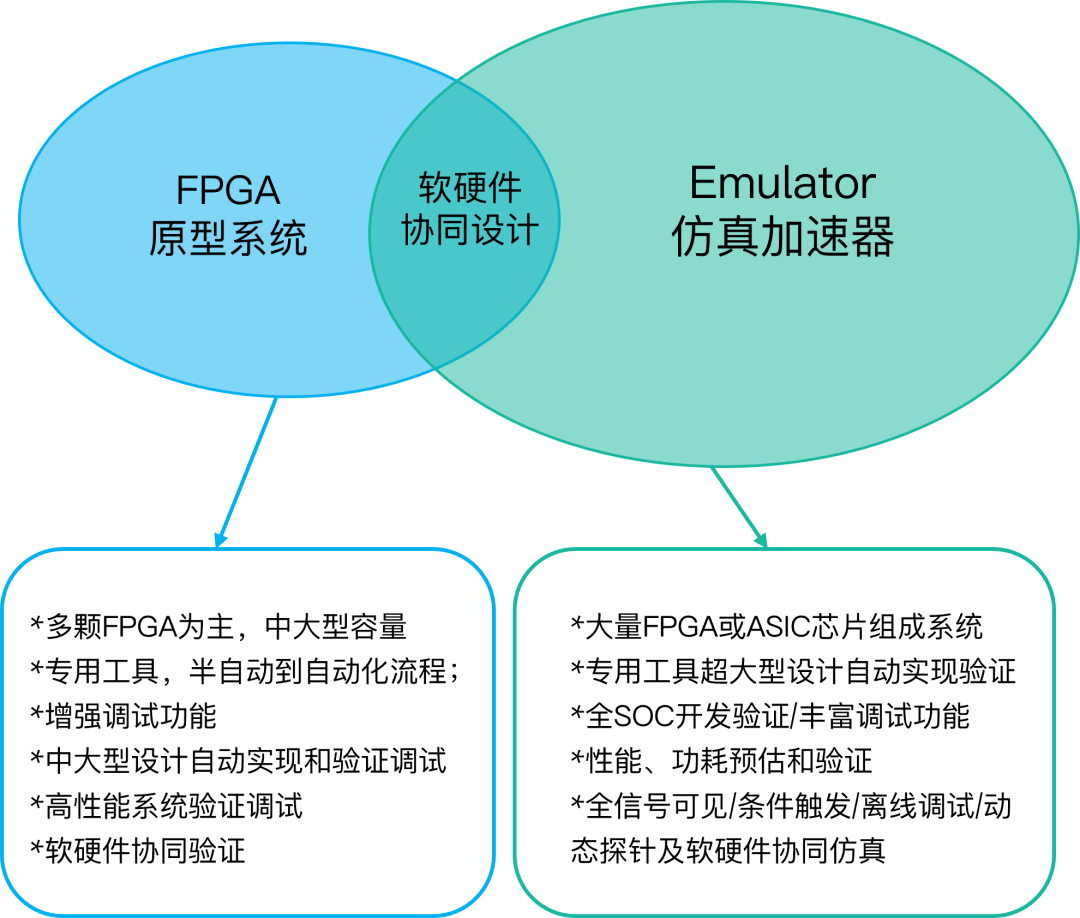

下面的图例便于读者更容易的理解它们二者之间的关系:

图2:FPGA原型验证系统和硬件仿真器Emulator之间的关系

从系统的特性上看,FPGA原型系统支持多FPGA、自动分割;性能较高的情况下运行系统软件;仿真加速器的超大容量可以放全芯片的设计,进行全芯片的系统功能/性能/功耗验证。从应用场景上看,我们看到原型系统和仿真加速器在软硬件协同设计方面,有一定的交集。

以上就是关于FPGA原型验证系统和硬件仿真器这两种不同的数字设计验证平台的对比介绍,谢谢!

FPGA原型验证系统的主要应用场景是“芯片设计过程中搭建软硬件一体的系统验证环境”:一是芯片流片回来前为软件团队提供调试驱动软件的平台,加速芯片上市时间;二是作为芯片仿真验证的一个补充,因为在FPGA内部可以生成真实电路,并且可以对接真实的硬件子卡,相较仿真使用的软件模型有一定差别,因此可以发现更多隐蔽的bug ;此外FPGA相对软件仿真以及Emulator而言,速度更快,比较适合一些耗时较多的场景case。故在芯片设计规模越来越大的情况下,使用多颗FPGA芯片互联能够快速实现高性能的全系统验证原型,并满足该场景下的调试需求。

Emulator 硬件仿真器

Emulator的主要应用场景是 “芯片设计过程中对完整封闭的设计进行加速仿真并调试”,它与FPGA原型验证系统的主要定位差异在于:能对全芯片进行和芯片时序行为一致的硬件仿真,包括全芯片信号的提取,对全芯片的功能、性能、功耗进行系统级的验证与调试。这一点差别导致了两者系统设计上的巨大差异。用户无需花费大量的时间去考虑如何设计、如何分割、如何布局布线等问题,从而在易用性方面大大增强。基于FPGA原型验证系统平台和 Emulator硬件仿真平台二者的设计目标和应用场景差异,下面我们分别来介绍一下这两种产品的关键点。

FPGA原型验证系统

随着目前集成电路的不断发展,设计规模的大型化,单颗FPGA板在容量上就显得捉襟见肘,已经无法满足设计需求。以目前国内头部的CPU、GPU设计公司的设计规模,单颗IC芯片的设计体量,需要占用到几十颗Xilinx VU440级别FPGA的情况,已屡见不鲜。在这种背景之下,FPGA系统供应厂商开始着手研究多颗FPGA的系统互联解决方案。其中就包括在单块的PCB板上装配多颗FPGA及多个FPGA系统之间的互联。经过不断探索,FPGA原型验证平台产品应运而生。之所以称之为“平台”或“系统”,就一定会包含对应的软件和硬件。首先在硬件结构上多颗FPGA互联结构的引入就要求结构上比单板形式的FPGA开发板要复杂的多,其次FPGA芯片厂商提供的软件工具无法支持多片的FPGA分割,需要配套专业的FPGA原型分割相关软件工具。一套优秀的FPGA原型验证系统,应该具有以下产品特性:

基于模块化的设计,可灵活扩充与裁剪的验证平台规模

在保证一定的高速仿真性能的前提下,提供设计完整性

提供从软件早期开发到系统级验证的解决方案

提供从综合、自动模块分割、布局布线、FPGA bit产生、下载、在线/离线Debug的整套流程

提供丰富的调测手段,帮助用户快速定位问题,易于设计的快速Bring Up

提供丰富的接口子板和外部真实设备相连

提供软件接口与外部工具构成复杂的调试解决方案

提供丰富的IO接口,以及高速Serdes接口用于partition互连以及外设子卡的互连

FPGA原型验证系统速度快,但它的缺点也是显而易见的,主要体现在调试的便利性上继承了FPGA自身的一些缺点,比如需借助FPGA内嵌逻辑分析仪来抓取信号排查问题,布局布线耗时冗长,效率不是太高。

硬件仿真器Emulator

在目前SoC规模越来越大型化的情况下,有的设计甚至达到数百亿ASIC等效门规模,巨大的设计规模导致软件仿真时间上的消耗变得越来越无法忍受。FPGA原型平台在验证规模到达一定级别,FPGA数量太多的情况下,也会带来新的分割问题并且会失去原有的性能优势。硬件仿真器的优势主要在于它独有的、超大规模的硬件结构,尽可能地保证了RTL设计的完整性。从硬件实现上看,一般有基于FPGA和CPU两种架构,对于基于FPGA架构的类型来说(如Synopsys的Zebu系列),可以理解为有很多块FPGA单板,大量的单板与电源、控制等再互相连接起来,形成一个“庞然大物”,优点是仿真性能高,使用商用FPGA可以降低开发成本;对于基于CPU架构的类型来说(如Cadence的Palladium系列),通常会将集成了数以万计的高速CPU核的ASIC芯片焊接在一块巨大的单板上,配以控制、冷却等模块构成一个完整系统。优点在于编译时间短,调试能力强;缺点就是功耗高,需要特别冷却系统和运营成本高,稳定性比较难控制,性能一般也比基于FPGA的硬件仿真系统低些。一般一套Emulator的体积大约从一个冰柜到一台大双开门冰箱的大小,而大型Emulator的重量也可以用“吨”来计算了。本文主要介绍基于FPGA的硬件仿真器。基于FPGA的原型平台和硬件仿真器,两者的架构和软件上虽有一定的相似之处,但定位不同,Emulator的定位和设计都是指向大容量和全系统仿真级调试,因此软硬件设计上有不同的取舍。综合来看,硬件仿真器的特点是支持超大规模(10亿门级以上)的设计容量,全自动化的软件设置实现流程,基本无需修改硬件连接配置,以及灵活多样的全系统仿真调试能力,包括:

信号的追踪深度更深(达数十亿仿真周期)

信号的条件触发、动态探针插入、离线调试

拥有不限量的时钟域,它们可以从核心时钟资源中无限衍生

全系统范围的调试追踪

带有UVM验证方法学的协同加速仿真

软硬件的协同验证、测试接口的虚拟化支持

系统功耗与性能预估、分析

目前,主流的Emulator工作特点,基本上包括以下几种:

基于Cycle级的软硬件联合仿真

基于ICE ( In-Circuit Emulator )模式: 一种最为传统的,理论上运行速度最快的模式。这种模式下需要在硬件中集成被测试逻辑单元及测试逻辑,或者通过外设硬件输入激励;且往往需要用到Speed Adapter以实现外围高速硬件和硬件仿真器在工作频率上的桥接。由于Emulator本身的运行频率不高,那么和外部的设备,如PCIE/SATA/USB等连接时需要通过速度匹配设备,通过缓存来匹配快速端的速度进行适配

基于事务级(Transaction)的软硬件联合仿真;这种情况下,被测试的逻辑部分运行在Emulator的硬件里面;硬件通过一套完整的软件及驱动、物理通道和Host Server实现连接。这种方式下可以使用多样的SW model Library,常见的有PCIE/AMBA bus等。虽然说它的运行速度没有ICE模式快,但是在软件上的功能和方法支持非常丰富。这种方式也被认为是软件Simulator的硬件化

提供丰富多样的虚拟解决方案:包括Virtual Host(Qemu/VDK),Virtual Device(例如基于Chiplet的Die to Die 模型),Virtual memory models(各类协议的存储器模型SDRAM/Flash/SRAM/EEPROM),Transactors(AMBA/PCIe),Hybrid Mode(CPU Models+ DUT in Hardware)

多种模式的探针工作方式:静态探针、动态探针、全景探针和定制探针组等

其次,在多用户的支持方面,Emulator系统可以支持较多的用户同时在线使用,实现资源的灵活调度;而FPGA原型系统目前也有可以支持多用户的场景,但因为产品在时钟资源分配等方面存在着局限性,所以实际很少采用。

总 结

最后,我们再来看一下FPGA原型验证系统和硬件仿真器Emulator之间的对比表格:

图1:FPGA原型验证系统和硬件仿真器Emulator之间的对比

下面的图例便于读者更容易的理解它们二者之间的关系:

图2:FPGA原型验证系统和硬件仿真器Emulator之间的关系

从系统的特性上看,FPGA原型系统支持多FPGA、自动分割;性能较高的情况下运行系统软件;仿真加速器的超大容量可以放全芯片的设计,进行全芯片的系统功能/性能/功耗验证。从应用场景上看,我们看到原型系统和仿真加速器在软硬件协同设计方面,有一定的交集。

以上就是关于FPGA原型验证系统和硬件仿真器这两种不同的数字设计验证平台的对比介绍,谢谢!

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。