LPC2294是PHILIPS公司推出的一款功能强大、超低功耗且具有ARM7TDMI内核的32位微控制器。它具有丰富的片上资源,完全可以满足一般的工业控制需要,同时还可以减少系统硬件设计的复杂度,提高系统的稳定性。

CAN(“Controller Area Network”)总线控制器局域网是一种能有效支持分布式控制或实时控制的串行通信网络。CAN总线以其高性能、高可靠性、廉价等特性,越来越受到人们的重视和青睐。为了有效的管理工业现场的CAN节点,充分发挥CAN总线的性能,通信卡的设计与研究十分必要。但目前市场上类似产品存在着两点不足。

首先是一般工业现场中可能拥有不止1条CAN总线,而目前设计的通信卡上的CAN的接口太少,因而会给设备的集中管理带来困难。

二是目前两条CAN网段问的通信主要通过一对一CAN总线网桥来实现,但这种方式解决不了工业现场中同时在几条CAN网段问传输数据的需求,也容易导致组网混乱。

为此,本设计选用的ARM控制器LPC2294内部集成有四路CAN控制器,完全符合CAN规范CAN2.0B标准和ISO11989-1标准。全局验收过滤器可识别几乎所有总线的11位和29位Rx标识符。作为本设计的核心部件,LPC2294的使用能够很好地解决上述2个问题,它不仅能担起主控制器的工作,同时还可作为CAN网络的数据传输控制器,来与网络中的节点实现数据交换。

1 、硬件设计方案

目前计算机的发展,除了少数专门的工控机还在使用ISA总线以外,PC机上使用最为普遍的就是PCI总线了。PCI总线是Intel公司推出的一种高性能32/64位PC机局部总线,可能同时支持多组外围没备而不受制于处理器,其数据吞吐量很大(33 MHz总线频率、32位传输时,其峰值可高达132 MB/s),PCI总线依靠其优越的性能必将取代ISA总线。因此,本文基于PCI总线来设计一个带有4个CAN总线网段的智能通信卡。图1是该通信卡的整体硬件结构图。

1.1 PCI总线接口的实现

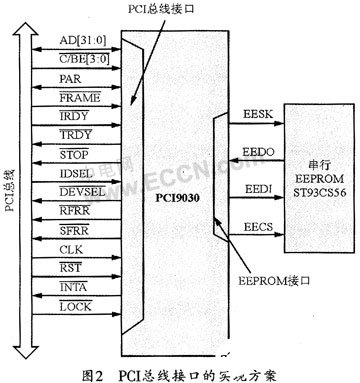

PCI总线具有非常严格的规范,也具有良好的兼容性。但是PCI总线协议也比较复杂。本设计选用专用的PCI总线接口芯片PCI9030来实现网关的PCI总线接口。PCI9030是PLX公司开发的低价格PCI总线从模式接口芯片。该芯片功耗低,符合PCI2.2规范,用户设计时只需考虑局部总线一侧的逻辑控制电路和用于配置的外部EEP-ROM,而不必考虑PCI协议的具体实现方法,这样就大大简化了设计难度,缩短了开发周期。

PCI9030要求有一块EEPROM作为初始化存储器。在系统加载时,PCI9030先从该EEPROM中加载初始数据,进行初始设置,因此,EEP-ROM中的信息是否正确决定了PCI卡的加载和运行是否正常。本设计选用ST93CS56作为PCI9030的初始化存储器,其结构方案如图2所示。

1.2 CAN总线接口的实现

该通信卡中CAN总线接口部分实现有以下两种常用的方法:

(1) 独立CAN总线控制芯片实现

即采用飞利浦公司的SJA1000独立CAN控制器来实现CAN协议。这种方法的优点是能实现较复杂的功能,灵活性也不错,但由于它是独立的控制器,设计通信卡拥有4个CAN网段就需要4片SJA1000,这样会造成资源冗余,系统会比较庞大,而且稳定性也会受影响,设计难度也较大。

(2) 带CAN接口的微控制器实现

该方法具有代表性的有飞利浦公司的ARM芯片LPC2294,它集成有4路片上CAN总线控制器,能很方便地实现多路CAN总线接口,减小系统规模,提高系统稳定性。

比较上述两种方法,在传统的SJA1000中,接收过滤只能满足一些规律性较高的ID筛选过滤,或对个数较少的ID (一般小于10~15个)进行任意筛选过滤,而难以实现更复杂的任意ID进行筛选过滤,这无疑增加了系统软件设计及运行负担。

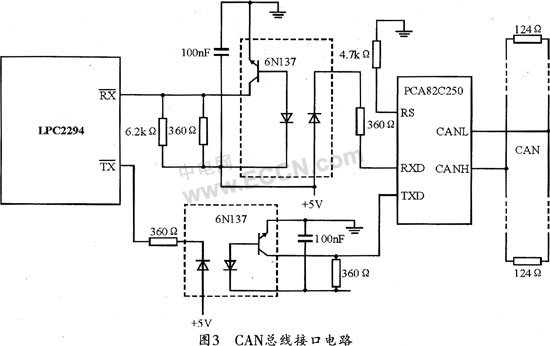

而第二种设计方法相对较为简便。由于LPC2294微控制器中为所有CAN控制器提供了全局的接收标识符查询功能,因而能容易地设计较复杂的ID接收过滤,其工作的重点主要在ARM芯片的软件设计上。本文采用第二种方法来实现CAN总线接口,并采用PCA82C250作为CAN总线驱动器,同时将6N137连入CAN控制器和CAN驱动器之间以降低CAN总线对网关卡的电磁干扰。图3所示是LPC2294中一个CAN接口的连接图,其它接口与之类似。

1.3 微控制器与PCI9030之间的硬件接口设计

微控制器与PCI9030之间的硬件设计是该通信卡的核心控制部分。本设计采用ALTERA公司的FPGA EPlC6来实现微控制器与PCI9030之间的接口。EPlC6是ALTERA公司的一款FPGA芯片,它内部集成了20块128×36 bits的RAM模块,可以方便地将它编程为所需要的“双口RAM”,然后将上行数据(CAN节点发往PC机的数据)和下行数据(PC机发往CAN节点的数据)通过该“双口RAM”缓存转发。由于EPlC6拥有丰富的I/O口,故可灵活选择数据格式(32位/16位/8位)以及传输方法,本文采用16位复用传输模式。

EPlC6还要编程实现PCI9030与ARM之间的逻辑控制时序转换。由于PCI9030与ARM的控制信号不完全一致,所以需要进行逻辑控制时序转换。同时,本文PCI9030的局部总线一侧采用的是地址/数据复用模式,而ARM控制器采用的是非复用模式,因此也需要EPlC6进行模式转换:在PCI9030的地址周期内可利用LALE将16位地址锁存到EPlC6内部寄存器,等到PCI9030的数据周期来临时,再与数据一起送到ARM的地址口与数据口上,以方便ARM取用。

2 、软件设计

2.1 通信卡软件设计

通信卡上的软件主要指的是ARM控制器上的软件程序。本文选用ARM控制器LPC2294来实现智能数据传输路径选择。LPC2294是通信卡的控制核心。它集成有4路CAN控制器,每个CAN控制器都与独立CAN控制器SJA1000有着相似的寄存器结构,它只是对器件寄存器访问由原来的8bit字节访问转变为了32 bit的双字访问。LPC2294可实现CAN网段与上位机之间的数据传输控制(包括上行数据传输和下行数据传输)以及不同CAN网段间的数据传输控制(平行数据传输)。

LPC2294为所有CAN控制器提供了全局接收标识符查询功能。它包含一个512×32 (2 k字节)的RAM,可通过软件处理在RAM中存放1~5个标识符表格。整个接收滤波RAM可容纳1024个标准标识符或512个扩展标识符,或两种类型的混合标识符。由于允许的表格范围有2 k字节,故能容易地满足复杂的ID接收过滤要求。LPC2294在FullCAN模式下能自动接收并选定网段的标准帧,但本文不采用FullCAN模式。

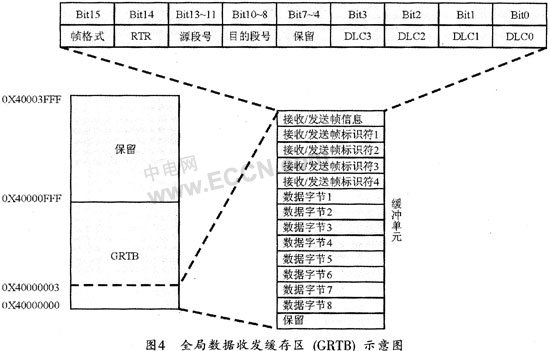

若在EPlC6的“双口RAM”中设置一个状态与控制寄存器组(SOR),那么,上位机便可通过访问该寄存器组查询通信卡的运行状态。为了有效管理数据传输,防止传输过程中的数据丢失,本设计在ARM内部的静态RAM区开辟了一个全局数据收发缓存区(GRTB),其示意图如图4所示。

图4中,对于标准帧来说,它只有11位标识符,因此,图中的标识符字节3和4保留不用。而帧格式用来区别此帧是标准帧(0)还是扩展帧(1)。当RTR为1时,表示此帧是远程帧。图中的源段号和目的段号用于表明此帧来自哪个网段以及将要送往哪个网段(此处将上位机也作为其中一段来处理)。DLC表明传输的数据字节数目。

2.2 通信卡的运行流程

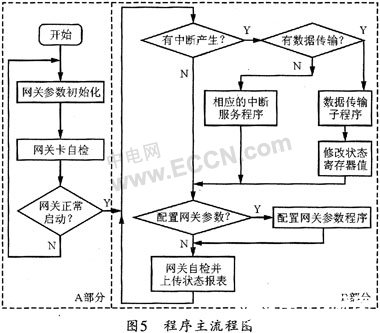

系统上电复位后,系统将首先运行初始化程序。LPC2294的初始化主要是初始化全局接收和发送缓冲区以及清除状态寄存器中的值等;PCI9030的初始化主要是从EEPROM中加载初始数据以进行初始设置,CAN初始化包括设置模式、总线时序、中断使能、标识符表格,这些设置均可通过给CAN芯片的内部寄存器赋值来实现。初始化成功之后,通信卡将进行自检,并在确定启动正常之后进入工作状态。这一部分的程序流程图如图5的A部分所示。

系统进入工作状态后(图5中的B部分)将等待中断产生,如有,则进人相应的中断服务程序。如果是数据传输,则转入数据传输子程序,数据传输子程序主要包括3个部分:

(1) 下行数据传输

下行数据传输指的是上位机向CAN网段发送数据。即上位机把数据写入到“双口RAM”中以等待LPC2294将数据取走。LPC2294将上位机发来的数据暂时存放在全局数据收发缓存区(GRTB)中,然后检查匹配的目的段是否有空闲的发送区(CANSR中的TBS位为1),若有则将数据分别写入每个网段的发送区并发送。如果匹配网段的3个发送缓冲器全为忙,则循环等待,直到有一个以上的发送缓冲器为空再进行发送。

(2) 上行数据传输

上行数据传输指的是CAN网段向上位机发送数据。当程序检测到某个网段X的CAN中断/捕获寄存器(CANICR)中的接收中断位(RI)置位后,它将进入接收中断服务程序。此时程序将到标识符表格中查找匹配的标识符,CAN控制器会在接收时自动搜索接收滤波器的RAM中的表格并进行匹配,只要找到匹配值则产生接收中断并通知用户保留信息,否则自动放弃这一帧信息而不产生接收中断,如果它只找到一个匹配值(源网段中),则说明此数据是只传输给上位机的,此时程序会将接收到的数据信息按上面介绍的格式保存到全局数据收发缓冲区(GRTB),以等待LPC2294将其发送给EPlC6的“双口RAM”,以便上位机读取。

(3) 平行数据传输

当出现接收中断时,程序也会到标识符表格中查找匹配的标识符,如果找到一个以上的匹配值,则说明还有其他网段需要这些数据。此时程序会将接收到的数据信息读入到全局数据收发缓冲区(GRTB)中去,然后把数据发往匹配网段。

在调用相应的数据传输子程序后,程序将置标志位并返回。如果是其它一些中断,则转入相应的中断服务程序。若没有中断产生,则检查PC机是否有参数配置需要,最后进行系统自检。本系统会在系统闲暇时进行自检并上传状态报表,这样可以使用户随时了解通信卡的工作情况,对于提高系统的工作可靠性以及出现故障时的查错效率具有重要的意义。

2.3 上位机程序设计

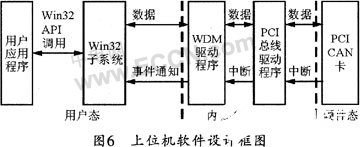

本设计中,上位机软件设计程序主要包括通信卡底层驱动程序和用户服务程序。其设计框图图6所示。

通信卡底层驱动程序的功能主要是配置CAN总线接口、收发CAN总线上的数据、对CAN总线进行实时监测、执行用户程序的收发命令等。CAN总线和PCI总线错误均采用中断处理,并通过事件(Event)内核对象直接通知给用户程序。

PCI的用户服务程序则通过PCI通信程序与系统PCIDI (PCI device interface)进行通信,并由系统完成PCI协议的处理与数据传输。用户可以在设计好的上位机界面上方便的设定节点参数,查询节点状态信息。

3 、结束语

本文设计的CAN/PCI智能通信卡采用功能强大的ARM芯片LPC2294作为核心控制芯片,因此,该通信卡能够同时处理4路CAN总线向上位机的数据传输。对于CAN网段之间的通信需求,本通信卡也能够很好地满足,并可使工业现场的CAN网络组网更为简单。