继4月5日公开“一种芯片堆叠封装及终端设备”专利后,华为技术有限公司近日又公开了2项芯片相关的发明专利。

△Source:国家知识产权局网站截图

△Source:国家知识产权局网站截图

5月6日,国家知识产权局官网公开了华为申请的2项芯片相关专利——“一种多芯片堆叠封装及制作方法”和“芯片堆叠封装结构及其封装方法、电子设备”,申请公布号分别为CN114450785A和CN114450786A。

“一种多芯片堆叠封装及制作方法”

该专利涉及芯片技术领域,不仅能够解决多芯片的应力集中问题,还能够以进行更多层芯片的堆叠。

△Source:国家知识产权局网站截图

△Source:国家知识产权局网站截图

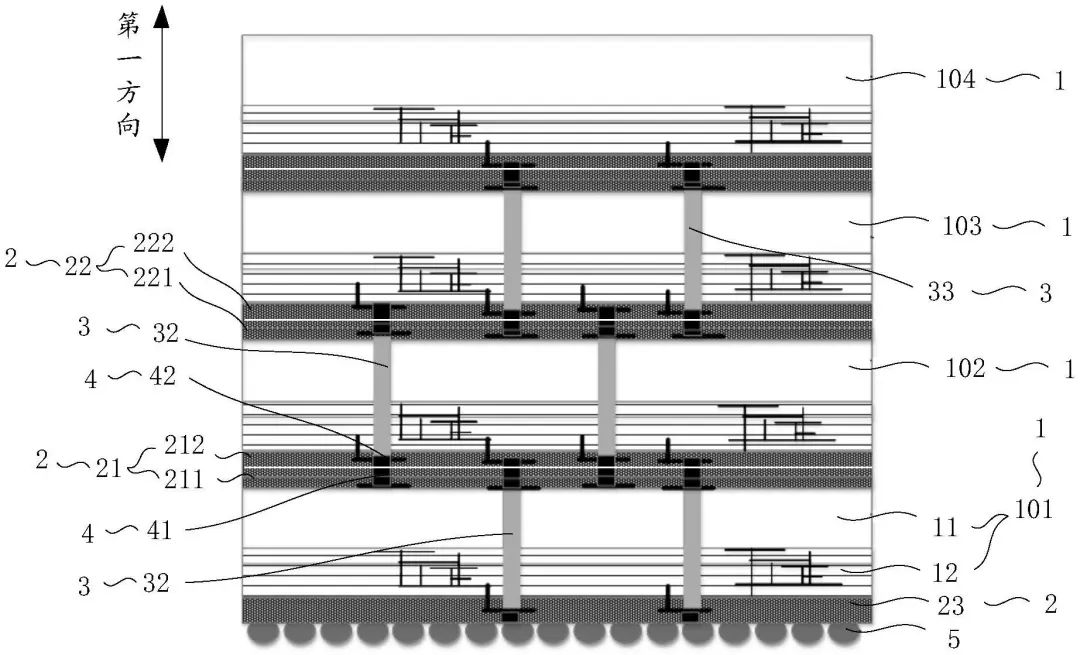

该多芯片堆叠封装包括:

沿第一方向堆叠设置的第一芯片(101)和第二芯片(102),其中所述第一芯片(101)内沿所述第一方向开设有第一导电通孔(31),所述第二芯片(102)内沿所述第一方向开设有第二导电通孔(32);

设置于所述第一芯片(101)和所述第二芯片(102)之间的第一再布线层(21),且所述第一再布线层(21)的两侧分别与所述第一芯片(101)的表面和所述第二芯片(102)的表面固定,其中所述第一导电通孔(31)和所述第二导电通孔(32)通过所述第一再布线层(21)导通,所述第一导电通孔(31)和所述第二导电通孔(32)错开设置。所述多芯片堆叠封装及制作方法用于芯片的制造。

“芯片堆叠封装结构及其封装方法、电子设备”

该专利为一种芯片堆叠封装结构(100)及其封装方法、电子设备(1),涉及电子技术领域,用于解决如何将多个副芯片堆叠单元(30)可靠的键合在同一主芯片堆叠单元(10)上的问题。

△Source:国家知识产权局网站截图

△Source:国家知识产权局网站截图

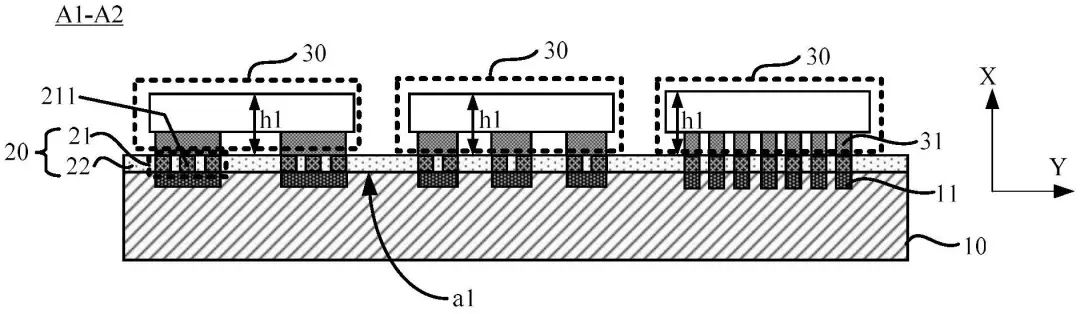

芯片堆叠封装结构(100),包括:

主芯片堆叠单元(10),具有位于第一表面上的绝缘且间隔设置的多个主管脚(11);

第一键合层(20),设置于第一表面上;第一键合层(20)包括绝缘且间隔设置的多个键合组件(21);

多个键合组件(21)中的每个包括至少一个键合部(211),任意两个键合部(211)绝缘设置,且任意两个键合部(211)的横截面积相同;

多个键合组件(21)分别与多个主管脚(11)键合;

多个副芯片堆叠单元(30),设置于第一键合层(20)远离主芯片堆叠单元(10)一侧的表面;

副芯片堆叠单元(30)具有绝缘且间隔设置的多个微凸点(31);

多个微凸点(31)中的每个与多个键合组件(21)中的一个键合。

堆叠技术竞争激烈 台积电/三星/英特尔等火力全开

据了解,3D堆叠技术是利用堆叠技术或通过互连和其他微加工技术在芯片或结构的Z轴方向上形成三维集成,信号连接以及晶圆级,芯片级和硅盖封装具有不同的功能,针对包装和可靠性技术的三维堆叠处理技术。

该技术用于微系统集成,是在片上系统(SOC)和多芯片模块(MCM)之后开发的先进的系统级封装制造技术。

当前,台积电、英特尔、三星等国际半导体厂商都开发了自己的3D芯片封装技术。

例如,英特尔于2018年底推出了业界首创的3D逻辑芯片封装技术——Foveros;三星在2018年推出了名为“X-Cube”的3D IC封装技术;台积电则将旗下SoIC、InFO及CoWoS等3D IC技术平台进行整合,并命名为“3D Fabric”。

今年3月初,苹果发布了迄今为止最强大的芯片——M1 Ultra,该芯片整合了两块M1 Max芯片,包含高达1140亿个晶体管,而这也再次说明了先进封装技术方向的正确性。

在芯片堆叠封装领域,面对高手林立的竞争者,华为似乎也早已加入“战局”。

缓解成本压力 华为公开芯片堆叠封装专利

信息显示,华为此次公开的2项专利申请时间均为2019年。而事实上,早在2012年,华为便向国家知识产权局申请了一项名为“芯片堆叠封装结构”的发明专利。这意味着,华为对芯片堆叠封装的研究在2012年甚至更早的时间就已开始。

△Source:国家知识产权局网站截图

△Source:国家知识产权局网站截图

今年3月底,华为首次公开确认芯片堆叠技术。

华为轮值董事长郭平在3月28日举行的华为2021年年报发布会上表示,未来华为可能会采用多核结构的芯片设计方案,以提升芯片性能,同时采用面积换性能,用堆叠换性能,使得不那么先进的工艺也能持续让华为在未来的产品里面,能够具有竞争力。

几天后(4月5日),华为正式公开了“一种芯片堆叠封装及终端设备”专利,涉及半导体技术领域,其能够在保证供电需求的同时,解决因采用硅通孔技术而导致的成本高的问题。

据悉,这种芯片堆叠工艺有望比现有的芯片堆叠方法便宜得多。该技术将帮助华为继续使用较老的成熟工艺技术开发更快的芯片。

封面图片来源:拍信网