由 作为主要协办方之一的“全国嵌入式芯片与系统设计竞赛—— FPGA ”日前落下帷幕。这是目前国内 FPGA 竞赛领域最高水平竞赛之一,旨在提高学生在数字系统设计领域尤其是可编程逻辑器件应用领域的创新实践能力,培养具有创新思维、具备解决复杂工程问题能力且富有团队合作精神的优秀人才,推进高校与企业人才培养合作共建。

本文引用地址:作为竞赛的协办方, 为竞赛提供了一系列具有挑战性和前瞻性的赛道选择,激发参赛选手的创造力和解决问题的能力。本次竞赛 FPGA 赛道吸引了来自国内 200 多所高校的近千支队伍,近三千名本科及研究生同学参与其中。此外,AMD 还为参赛队伍提供了多样化的器件,包括 Spartan 7 FPGA 系列、Zynq UltraScale+ MPSoC 系列以及最新的 Versal 自适应 SoC 系列器件,展现了 AMD FPGA 技术在大学教育和学术创新的广泛使用。

AMD 竞赛主要考察参赛作品的理论创新与应用场景创新。由 AMD FPGA 和自适应 SoC 器件提供支持的竞赛作品涵盖了模式识别、算法加速、机器控制等多个领域。一些作品在传感器融合、通信技术、图像处理等方面取得了显著成果。例如既有创造性地利用FPGA 数字信号处理的优势实现了艺术的跨界组合;又有成功落地于自动化图书馆、高性能仪器设备、高速目标识别等实际场景。

AMD 赛道作品展示(部分)

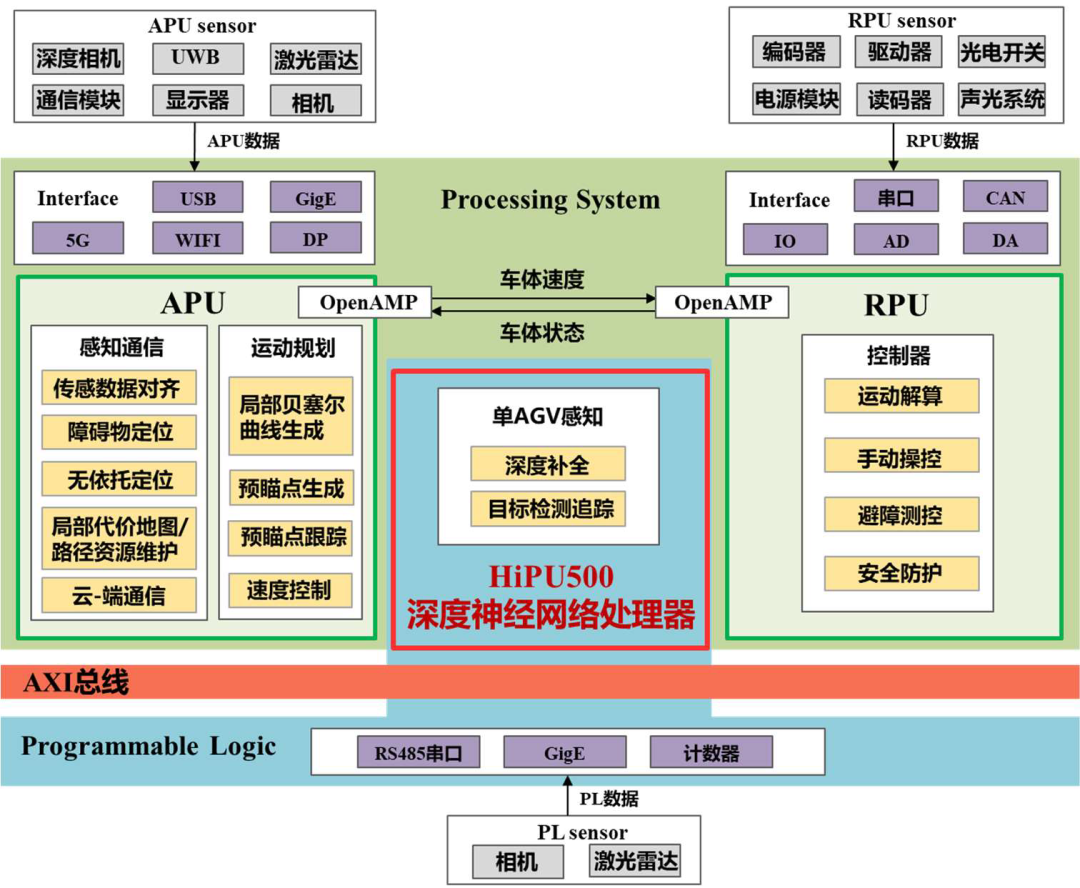

面向自主智能体感知与协作的多移动机器人控制器设

多自主移动智能体( AMR )是目前工业自动化中种类最多、应用最广的一大类自主智能体,它可以自动完成货物搬运,多 AMR 系统目前已成为企业自动化生产系统的重要组成部分。在人机共存的复杂工业场景下,目前多 AMR 系统主要面临宽阔路径下运输效率低、软件系统的通用性和适应性差、硬件系统成本高等问题。

来自西安交通大学团队设计了一种面向端云协同的多 AMR 控制器以解决上述问题控制器采用异构多核处理器实现,充分利用 Zynq MPSoC 中多核 PS、PL 等资源,合理分配计算负载,在软件和硬件两方面实现算法加速。在 PS 侧的 APU 上执行通行、规划以及定位算法,PS 侧的 RPU 主要运行底层控制和安全逻辑程序,APU 和 RPU 之间通过 OpenAMP 的框架进行通信和数据交互;在PL 侧通过 FPGA 扩展更多灵活接口以及自主研发的 HiPU 神经网络加速 IP 对目标检测以及深度补全等算法进行加速,最终在一颗 Zynq MPSoC ZU3 有限资源上完成 AMR 的智能计算。

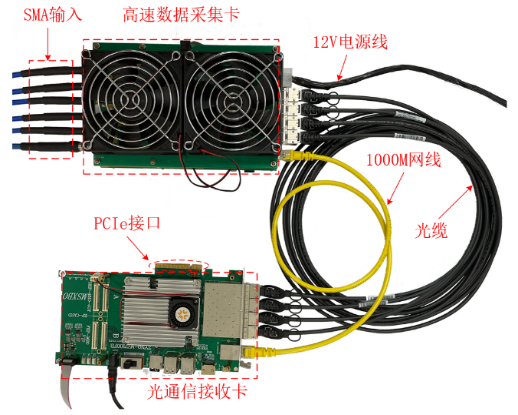

基于Zynq 7000的多波束高速数字接收机系统

针对射电观测对于获取时域数据的需求,来自三峡大学的团队利用 Zynq 7100 器件实现了一种 4 通道高速数据采集和处理系统。系统基于 GTX 完成与两片高性能 ADC 器件之间串行高速通信,具备 60dB 满量程信噪比、40Gbps 的 SFP+ 数据传输带宽,实现 300MSPS @ 16bit 的直接采样功能,并通过上位机进行时域数据的展示与存储。

基于 Zynq 的多算子融合显微镜电动聚焦系统

在常见的显微镜观测领域,往往需要通过粗、细调焦获取足够清晰的观察图像,但人工调焦的方式较为繁琐和消耗使用者精力且存在一定误差。随着科技的发展,显微镜未来势必朝着实时成像、多模态成像以及自动智能化的方向发展。而自动对焦技术作为辅助显微镜快速清晰成像的重要工具,未来势必有着广阔的应用前景。

来自华南师范大学的团队在本次竞赛中在 Zynq 7020 器件上实现了高速聚焦成像,动态无参考图像的失焦量评价、4 路图像拼接等功能。产品每秒可进行高达 48 次图像评价,同时在图像处理消影期间实现电动平台的移动,不干扰图像评价进程。

除了已经在实际工程中部署应用的作品,大赛中也涌现出很多结合参赛同学实际生活需求而完成的作品。这些成果富有创意,同时也展现了 AMD FPGA和自适应 SoC 在数字信号处理、高性能、低时延以及 AI加速方面的出色特性。

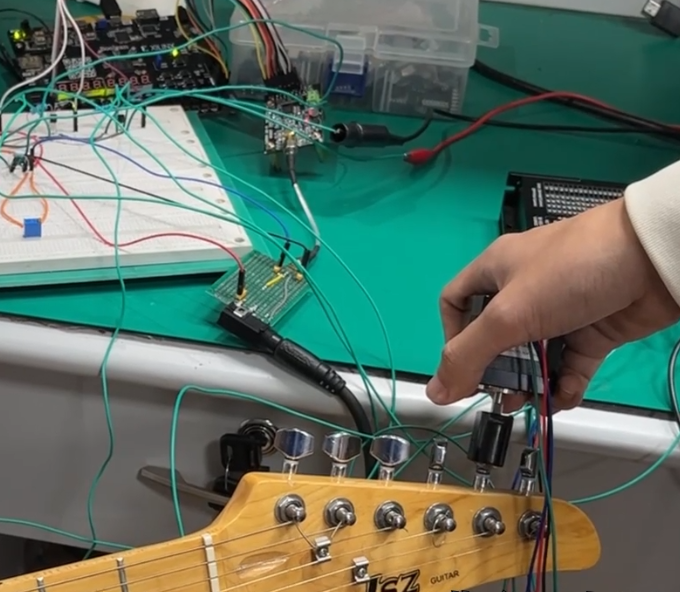

吉他自动调音器

来自西安电子科技大学的同学利用 AMD Spartan7 器件设计了一套吉他自动调音器。参赛者将采样到的吉他音量信号经过 FIR、FFT 等信号处理算法监测、频率分析、消除泛音等过程,并通过定制结构操纵琴头和琴弦处机械结构实现同步拨弦和调整旋钮,做到自动且准确地调标准音。校音精度达到 ±0.07cent(±3Hz), 平均只需 11 秒即可完成校音。

面向无人售货的高通量极速果蔬识别系统

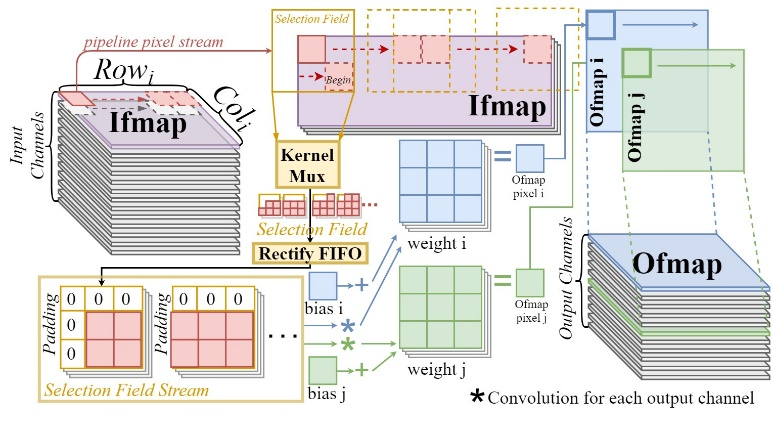

来自武汉大学的参赛者设计了一种针对性的大量果蔬识别算法被设计并将其部署在上硬件开发平台上。他们为了满足对同种水果不同品质识别的要求,在基于 FruitVeg81 数据集的自定义精细化数据集上训练,并利用剪枝、量化等网络压缩技术以优化硬件部署。同时结合 Zynq UltraScale+ MPSoC器件的优势设计了全流水加速架构,从而大幅提升网络的边缘推理速度,最终实现了在 495 帧/秒的高帧率下对 125 类不同种类或品质的水果进行识别,准确率达到 95.397%,帧率高达每秒 495.85 帧。

DTLN: 一种基于 Zynq 的双信号LSTM转换语音增强系统

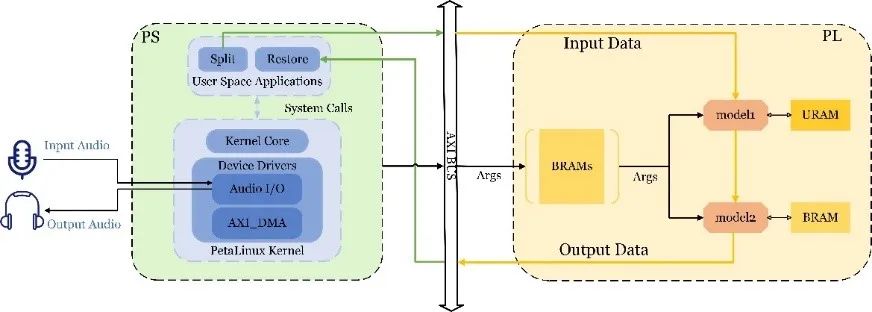

来自河海大学的参赛者使用 DTLN 神经网络降噪模型,模型以双信号转换 LSTM 为核心,可以通过学习长期依赖关系更好地捕捉语音信号中的时序信息,从而有效地降低噪音干扰。该作品在 Zynq 平台上实现了一种基于 FPGA 的协处理器设计,展现了在处理复杂环境下实时降噪任务的出色性能。

FPGA 的灵活编程性为本作品带来了显著的优势,最大化了其异构计算的加速潜力,实现了高效的实时处理。值得一提的是,参赛者在短短三个月内,从零开始利用 Vitis HLS 实现了所有信号处理、神经网络加速设计、验证和部署,并在 24bit 量化后通过Vivado、Vitis HLS 和 Petalinux 套件部署到板卡上。该系统脱离了 PYNQ 框架的限制,可以在任何版本的 Vivado 套件上部署并运行,实现音频的实时降噪处理。

在赛事过程中,AMD 还提供了领先的 FPGA 技术支持和解决方案,为参赛者提供了强大的软硬件支持。高效的开发工具和丰富的文档资源,则助力他们充分发挥创新意识,展现自我水平。此外,通过提供技术支持、分享实际经验,AMD 还与参赛者建立了密切联系。这种紧密互动的过程为年轻的科技爱好者提供了成长的机会与交流的平台。

作为大赛的发起方之一,AMD 大学计划与全国FPGA创新设计大赛已开展深度合作七年,累计支持和培养了上万名。七年的旅程,见证了 AMD FPGA 赛道从最初传统的 FPGA 平台扩展到广泛普及的 Zynq 平台这场技术与人才培育的双赢之旅。放眼未来,期待这些年轻的参赛者在科技领域茁壮成长,为百行百业的发展进步贡献自己的智慧和力量。