有人使用STM32G4系列芯片开发产品。他发现程序中如果遇到除以0的操作时,会跑进出错异常中断而影响程序运行。他想知道能否通过设置,即使发生除以0操作也不让程序跑进异常中断,并期望此时的除法运行结果【也就是商】直接等于当前变量类型所支持的最大值,比如,若被除数为16位变量,则经过该除以零操作后直接为其赋值为0xffff。【实际应用中客户的需求往往也是五彩斑斓的。^_^】

事实上是否可以如该STM32用户所愿呢?我们不妨一起看看。

首先,这个问题不属于STM32外设相关的,而是内核相关的。客户选用的是Cortex M4的内核STM32芯片,那我们就从M4内核手册中寻找相关内容。

我们通过查看ARM M4的内核手册,可以看到除以0操作会导致用法异常[UsageFault],同时它又说了,该操作和非对齐访问操作是否触发异常是可以配置的。详见下方绿色方框内文字。

那么对该用法异常的监测控制是通过哪个寄存器进行配置的呢?经浏览手册得知它是通过配置控制寄存器[SCB-》CCR]进行配置的。

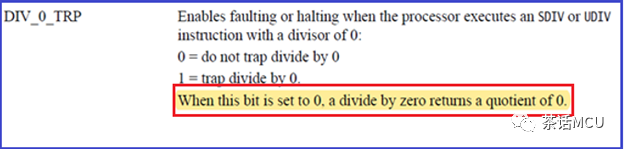

根据上面描述可知,当CCR寄存器的DIV_0_TRP位被配置0时,即使发生除以0操作也不会触发异常,只有当该位被置1前提下,当发生除以0操作时才触发异常事件并产生相应中断。

下面我们具体验证下。我找了块M4内核的STM32芯片的开发板。我们先使用ARM MDK来验证。

测试代码很简单,就是下面截图中的几行,简单的闪灯操作,里面夹了一句除法操作。SCB-》CCR被赋值0x00000210即置位了DIV_0_TRP,当被赋值0x00000200时对其进行清零。

经过测试,当我们置位上面CCR寄存器的DIV_0_TRP位,在发生除以0操作时就会进入HardFault中断,同时被除数的结果【Result】即商变为0.

而当我们对DIV_0_TRP位清零,即SCB-》CCR被赋值0x00000200时发生除以0操作不会触发Hardfault中断,但被除数除以0后其结果依然保持为0。整个程序运行起来感觉不到任何阻滞。

上面是基于ARM MDK环境测试的,我们换为IAR IDE测试看看。

我们依然先验证CCR寄存器的DIV_0_TRP位被置1的情况。经测试,结果跟ARM MDK环境下的测试结果完全一致。

当我们对CCR寄存器的DIV_0_TRP位清零时,测试结果也跟ARM MDK环境下的一致。

显然,结合Cortex M4内核手册的描述和实际验证,当发生除以0操作时是否触发异常事件是可以配置的,至于发生除以0操作后的商,它始终是0,这个结果其实在上面截图有明确提及,这里再单独截图出来。

不过,这个结果跟开篇客户所期望的不一致,这是由硬件决定的,不同的硬件在这个地方处理不尽相同。其实,其它Cortex M内核芯片这个地方约定是一样的。

聊到这里,或许有人发现了一个问题。从手册上看,这个除以0操作触发的应该是用法异常【UsageFault】,而我们在实际测试时进入的中断却是HardFault异常,这两个异常并不一样啊?

这是怎么回事呢?在此抛砖引玉吧,有兴趣的话不妨查找相关资料继续寻找相关答案。