EDA工具就这样连接两端,一端连接思路活跃的工程师,一端连接规则严谨的物理世界。所以,EDA工具提高升级也沿着两个方向走,一个方向面向工程师,即工具的易用性,简化难度,降低门槛,让更多人可以从事芯片开发;一个方向是面向物理世界的,即功能性,规则要够细,功能要够强,规模要够大,效率要够高,做好芯片工艺升级换代的支撑。

拿起石头做武器那一刻,决定了人类将成为这个星球的万物之灵,工具是人类文明高度的衡量标准,是生产力水平的代表,也是行业变革的催化剂。相机出现之前,画师既是艺术家,也是一种职业;相机出现之后,画师就只剩下艺术属性,普通人稍加训练,拍出的照片惟妙惟肖,与实景纤毫不差,面对工具加持的影像爱好者,在实景还原方面,一般画师就算有十年功力也难比过,画笔仍可以呈现艺术,但影像产业的繁荣则离不开现代工具。在工程领域也是如此,芯片设计最早都是靠工程师一笔一划用纸笔将设计在图纸上呈现出来,但集成度的提高很快让设计任务超出人力极限,各种工具应运而生,帮助工程师应对越来越复杂的产品开发,最后,EDA工具与IP成为了一个百亿美元规模的产业。

为什么EDA工具要从“Photoshop”变成“美图秀秀”?

最早的芯片产品开发者就像画师一样,从产品定义到逻辑设计,从版图到封装,从测试到应用,每一个晶体管都靠头脑和手工处理,属于高强度劳动密集型工作,对开发人员知识与经验要求极高,培养人才周期很长,不利于产业规模化发展。

随着计算机辅助设计(CAD)、设计重用和模型化开发等技术发展,芯片功能开发与具体物理实现逐渐剥离开,芯片架构师与数字电路设计工程师不再需要关注晶体管在物理实现时的很多细节,单元库、硬件描述语言和硅IP的出现,让工程师可以用抽象化的高级语言设计芯片,通过逻辑综合工具把抽象化设计转换成实际的逻辑电路连接组合,从而突破了人力极限,推动芯片沿着摩尔定律预测的方向不断提升集成度。

EDA工具就这样连接两端,一端连接思路活跃的工程师,一端连接规则严谨的物理世界。所以,EDA工具提高升级也沿着两个方向走,一个方向面向工程师,即工具的易用性,简化难度,降低门槛,让更多人可以从事芯片开发;一个方向是面向物理世界的,即功能性,规则要够细,功能要够强,规模要够大,效率要够高,做好芯片工艺升级换代的支撑。

但易上手和功能强不能兼美的情况还很普遍,对此,EDA大厂的答案很简单,不做选择,全都提供。

新思科技中国董事长兼全球资深副总裁葛群告诉探索科技(techsugar),随着数字社会全面来临,芯片应用范围不断扩展,不同设计需求将长期共存,新思为开发者提供了不同类型的集成电路设计工具,以满足更多元化的工程需求。

他用“美图秀秀”和“Photoshop”来举例。家电等终端产品所使用的芯片功能简单,性能要求也不高,普通工艺就能满足应用要求;而像CPU、GPU等追求极致性能的SoC,功能繁多,集成度要求极高,需要最先进的工艺才能实现。对于前者而言,相对简单的“美图秀秀”级别的工具便可满足其设计需求,而后者则需要更为专业的“Photoshop”级别的工具。

葛群表示,由于数字社会中芯片的需求量激增,未来使用“美图秀秀”类EDA工具进行芯片设计的场景会更多,市场潜力也会更大。因此,使芯片设计变得像用“美图秀秀”做图一样简单,而不是维持在原来只有少数人才能掌握的专业“Photoshop”,是半导体技术发展的前景及新思一直以来的期待。

降低EDA工具使用门槛大势所趋,半导体产业发展势头迅猛,人才缺口已经成为影响行业发展势头的决定性因素。

从1959年集成电路产业诞生,到1994年全球半导体产值首次突破1000亿美元,用时35年,而在突破千亿美元大关之后6年,半导体产值即破2000亿元美元,3000亿关口和4000亿关口分别用了10年和7年。根据市场研究机构IC Insights的估算,2021年全球半导体产值将突破5000亿美元,这也算4000亿到5000亿关口用时4年,而该机构预测2年之后的2023年,全球半导体产值将突破6000亿。

市场规模在膨胀,对人才的需求也水涨船高,而大芯片提高集成度的游戏还在延续,那么向EDA工具要开发效率的要求就会一直存在。因此,降低专业软件使用门槛,补齐人才缺口,用“美图秀秀”级别使用难度的软件,也能开发出功能强大的芯片,就成为EDA工具厂商的使命。

新思能提供什么样的“Photoshop”和“美图秀秀”?

在小芯片开发上,现有工具已经比较强大,纵然还不能像“美图秀秀”一样一键完成设计,但有足够丰富的工具、IP库与设计案例供开发者选择,已经大幅降低了开发难度。大芯片则要难很多,动辄集成数十亿颗晶体管,支持千百个功能,待测项成千上万,先进工艺要考虑的参数远多于成熟工艺,开发周期还是固定的18个月左右,像移动或桌面处理器这样巨大的系统工程,厂商往往要投入大几千工程师年开发资源,而至少每年升级一代主打产品已经成为头部芯片产品公司的惯例,如此浩大的工程,应该如何简化呢?

葛群介绍,新思为开发者提供了一套组合拳,利用开发左移、设计上云、人工智能与硅生命周期管理等创新理念和技术变革,芯片设计企业在工具和新式开发方法学帮助下,分解工程难度、加速设计进程、缩短开发时间,从而提高研发产出率。

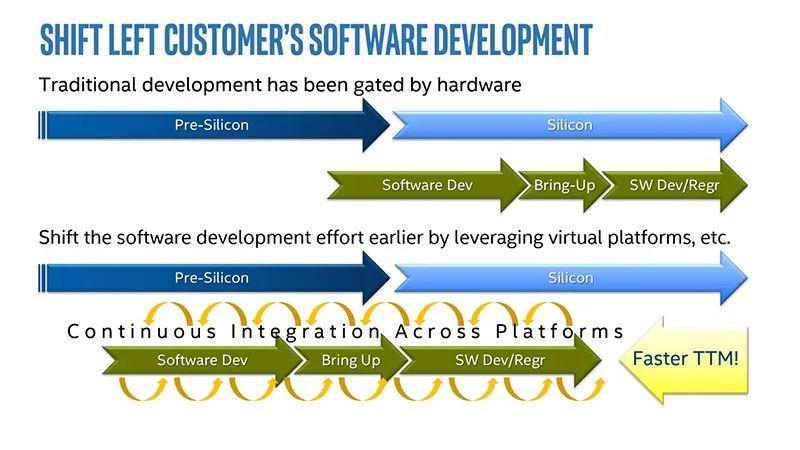

具体来看,开发左移(Shift Left)是指提前启动芯片验证和软件开发工作。传统开发流程各环节顺序展开,功能验证和软件开发只能等芯片生产好之后才能正式开始,随着芯片集成度提高,芯片验证与软件开发工作量越来越大,投入工程师资源不变时,开发时间就大大延长,极大增加了开发成本和错过新产品市场最佳投放时机的风险。

解决之道就是开发左移,利用IP复用、验证左移和Virtualizer等虚拟原型设计解决方案,软件工程师和验证工程师不需要等芯片生产出来,就可以在新思打造的虚拟原型平台上进行软件开发与功能验证。这样,开发者从最初产品定义期就开始验证项目流程管理的顺畅性、合理性,让整体步骤前移,从而加速设计进程、缩短设计时间并提高设计成功率。

人工智能在芯片设计工具、方法论和流程上应用效果如何,是EDA工具能否从“Photoshop”转向“美图秀秀”的关键。在这个领域,新思已经结出硕果。2020年初,新思推出DSO.ai技术,通过在芯片设计工作中引入人工智能,让EDA工具更智能化,更好用,并进一步提高了芯片设计的抽象层次,大幅降低芯片设计的难度和门槛,让开发者将更多精力投放在高层次模块的创新上。新思还利用人工智能技术在芯片设计的巨大求解空间里搜索优化目标,自主执行次要决策,帮助芯片设计团队以专家级水平进行操作,从而大幅提高整体生产力。

此外,新思诸多工具在推动人工智能硬件研发方面也起到了关键作用,尤其在硅工程、IP、设计与验证三个关键领域。2020年10月,新思宣布与IBM Research人工智能硬件中心的合作进入新阶段,目标是在新思的工具和工程师协助下,2029年将人工智能计算性能比当前提升1000倍。

芯片设计上云是另一个重点方向。“云上EDA”融合了EDA技术与云端运算性能和存储优势,能解决大型芯片设计面临的算力缺口问题,为开发者提供价格便宜的、实时可用的算力,研发环境部署简单快捷、高度协同,还可获得专家实时响应和支持。多年前,新思就开始与大型芯片公司合作,开展内部云上部署。例如,新思与台积电共同部署云上设计和芯片制造平台,帮助台积电成为首家实现云设计的代工厂。世界上首枚完全在云上实现的芯片,就诞生在台积电的云设计平台上。新思还与台积电在微软Azure平台上成功实现云上时序签核(signoff)新流程,加快片上系统开发效率。

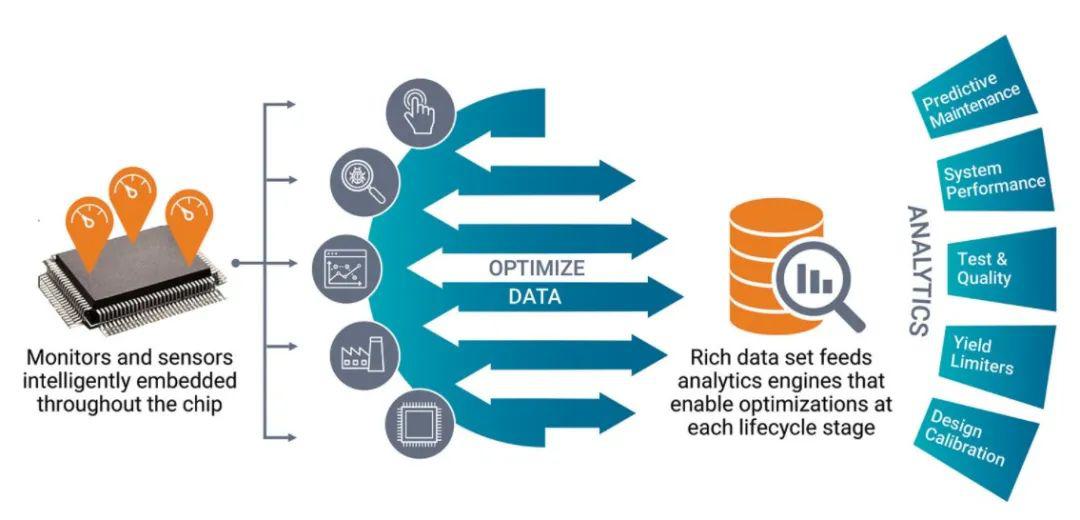

硅生命周期管理(SLM)平台则可视为芯片产品开发的大管家,该工具通过分析芯片内部的片上监控器和传感器数据,从而实现对SoC的全生命周期管理。新思的SLM平台为芯片开发及应用管理提供最丰富的数据,其数据收集范围覆盖芯片的设计校正、生产良率、测试验证、质量监控、性能评测到使用维护等环节,利用这些数据,结合新思融合设计(Fusion Design)工具,开发人员可以对芯片的性能、可靠性和安全性进行深入分析,这为SoC开发团队的设计经验积累打开全新视角,为开发者在芯片开发和系统应用中的每个阶段实现优化带来可能。

从上述产品来看,EDA公司本质上并不仅仅是软件公司,和通用软件或互联网公司差异极大。软件特色之一是迭代快,尤其互联网产品,上线之后再通过反复迭代试错来完善产品是常见的做法。EDA产品的试错空间就没那么大,大芯片开发投入大,时间窗口紧,一代产品没有赶上就步步被动,因此芯片产品公司期望在产品交付前把致命性缺陷都排除。

就这样移山填海、搭桥开路,坚持为芯片公司打造适应技术发展的软件“基建”,新思一路发展壮大,细看EDA、IP和软件完整性这三大业务,都在围绕帮客户在限定时间内开发出最低缺陷的产品做文章。

兼容并包是EDA发展之道

EDA的杠杆作用特别明显。宏观来看,EDA加上IP全球产值规模不过百亿美元,却是5000亿美元半导体行业的“苏伊士运河”,EDA和IP被“堵住”,晶圆制造公司和芯片设计公司均无法运转;微观来看,EDA与IP运用得好坏,决定着一个芯片产品公司的开发效率,还影响着产品质量和知识传承,因此优秀的芯片产品公司和EDA公司相互成就,彼此激励,一款释放生产力的新工具,往往源自于芯片产品公司在开发新产品时的定制化需求。

作为芯片产业的根技术和硬科技,EDA与IP的重要性不言而喻,未来大有可为。中国EDA产业发展磕磕绊绊,尚不能支撑当前本土芯片产业发展需求。近年来,我国对EDA产业重视程度提高很多,国内也出现了一大批EDA和IP公司,据不完全统计,近期准备上市的EDA与IP企业就有7家。

葛群建议,本土EDA厂商在谋发展时要更具耐心,持续投入积淀,然后静待时间来发酵。一款芯片的设计周期通常是一至两年,但仅一个EDA点工具的开发周期就需要三年,平台型工具更至少需要五年的开发时间。新思的发展历程就颇多借鉴之处,从点工具入场,通过长期研发投入和不断并购,历时30多年新思才构建起了如今阵列完整的EDA工具库。EDA本土化发展也不可能一蹴而就,必然是一个渐进的过程——先从单个点工具切入,再循序渐进到整个套件和平台。

葛群认为,在当前国内国际双循环相互促进的新发展格局下,新思在多数场景中都将是本土EDA厂商的合作伙伴,而非竞争对手。在本土公司尚不能构建起完整芯片开发环境前,本土供应链更可行的方式是与新思等头部企业加强合作,利用新兴的人工智能和云计算的技术,结合当前EDA头部企业的优势产品,发挥本土公司特色,为中国芯片行业发展铺平道路。

在支持本土EDA产业发展上,新思勇于尝试。2020年,新思与国产EDA公司芯华章开展合作,在南京设立云验证中心,为芯片设计企业提供验证服务。2021年,新思将12至28纳米工艺技术授权芯耀辉,芯耀辉可利用这些技术来适配国内芯片制造工艺的DesignWare 、USB、DDR、MIPI、HDMI和PCI Express等系列IP核,芯耀辉将为本土芯片制造商进行定制优化,以提高本土厂商芯片设计自动化水平,提升开发效率和验证能力。此外,芯行纪也在2021年开始为中国市场提供新思的Tweaker系列ECO(Engineering Change Orders)产品,并提供相应的技术支持。

硅IP是全行业知识与经验的结晶

葛群表示,在集成电路这样一个“合作大于竞争”的行业中,发展得好的EDA厂商,尤其体现了兼容并包的精神。

三大EDA厂商一路并购,将过去几十年工程师的奇思妙想都保留在自己的产品树中,这些产品凝结了EDA行业发展历程中所有知识结晶,只是有些被蒙上了岁月的灰尘,有些才长出来正闪闪发亮。