引言

随着现代科学技术的日益发展,颗粒尺寸及其分布在诸如石油、冶金、制药、建材等领域占据着越来越重要的地位。激光粒度仪就是用来测量微小颗粒尺寸及其分布的仪器,其基本原理是光的衍射理论。数据采集系统对激光粒度仪的光电探测器上光能信号的采集速度是激光粒度仪的性能指标之一,一般来说采集速度越快测量结果的准确性、重复性和稳定性越好[2]。随着各种新型光电探测器的不断出现,原有的数据采集系统需要重新设计升级。在新的设计方案中,数据采集系统的模拟通道容量增加到了 112路,并且系统的采集速度也有了大幅度的提高。

FPGA具有硬件资源丰富、设计灵活等特点,适用于数据通讯、数据采集和系统控制中,特别是它的并行结构和算术运算的特点,已越来越受到科技开发人员的青睐,被广泛应用到数据信号处理当中。对本系统而言, FPGA作为一种可编程、可重配置的数字集成电路,为实现系统的设计目标提供了有力的保证。

1 系统硬件设计

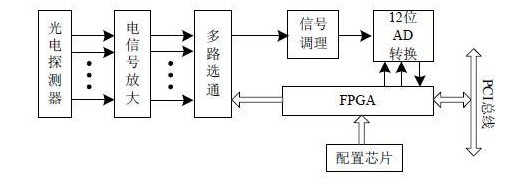

根据激光粒度仪的应用场合,本数据采集系统采用单通道采集的方案,它主要由模拟部分、数字部分和接口部分三部分组成。其中模拟部分包括光电探测器、电信号放大、多路选通、信号调理和 12位 AD转换,数字部分则完全在 FPGA内部实现,接口部分主要是计算机的 PCI总线接口。系统组成框图如图 1所示。

光电探测器电信号放大

激光粒度仪所用的光电探测器是由多个同心的光敏环组成的,每一光敏环输出的模拟电信号反映了照射到该环上的光能量大小。随着对激光粒度测量研究的不断深入,天津大学研制的 LSA系列激光粒度仪的光电探测器组件,其模拟输出已经发展到 96路之多[3]。为实现对这么多路模拟信号的采集,多路选通采用七片 16选 1模拟开关 DG406和一片 8 选 1模拟开关 MAX308组成双层级联结构,共可容纳 112路模拟信号,它的地址信号是由 FPGA提供的。AD转换芯片是数据采集系统的关键器件,采用 ADI公司的 12位逐次逼近型模数转换芯片 AD7321,在本文中该芯片使用其内部的 2.5V参考电压,模拟输入范围选择为 0~10V,它使用由 FPGA分频产生的 8.3MHz时钟信号,这样该芯片可在 2μs内完成一次模数转换。若连续两次采样间隔的时间设置为 2μs,则系统的数据平均传输速率可达到3Mbps。

2 系统软件设计

2.1 FPGA内部逻辑设计

本文采用了片上系统的设计理念,在 FPGA内部设计了所有所需的数字逻辑,可以实现数据采集控制、数据存储和 PCI接口方式的数据传输等功能。在本方案中,系统初始化后,首先上位机将采集的参数信息(模拟通道数、采样方式、AD7321工作模式等等)通过 PCI总线送给 FPGA中,FPGA再根据这些参数信息控制多路开关和 AD7321的工作,完成数据采集任务。采集过程中 FPGA将 AD转换得到的数据存入其内部的 FIFO中,当 FIFO快满时,它向上位机产生中断,上位机再通过 PCI总线读取 FIFO中的数据。

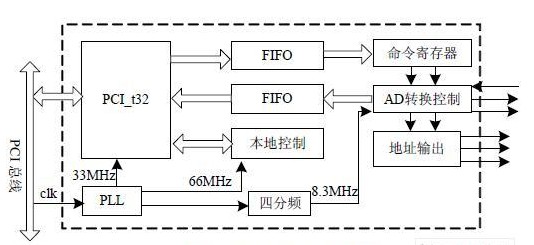

根据以上的设计思想,整个 FPGA内部逻辑的设计框图如图 2所示。本文中 FPGA选用 ALTERA公司的 EP2C5Q208C7芯片,采用自顶向下的设计方法,使用 Quartus II 7.0 等相关软件进行硬件代码的开发。下面给出各模块的设计过程。

1)PCI_t32模块。该模块是采用 ALTERA公司的 32位 PCI TARGET接口宏核逻辑,它支持 PCI配置空间读写、内存方式读写和 I/O方式读写,支持可参数化的配置寄存器,具有奇偶校验功能,能提供灵活的本地端接口,可以将复杂的、电气和时序要求高的 PCI总线逻辑转换为易于操作的本地接口逻辑[4]。

2)本地控制模块。该模块主要由一个能根据 PCI_t32的控制信号和 FIFO的状态跳转的有限状态机实现。它主要负责控制 PCI_t32和 FIFO之间的数据传送以及协调数据传输路径上其它相关模块的工作。当 FIFO快满时,该模块将产生中断信号通知上位机读取 FIFO中的数据。

3)命令寄存器模块。该模块用来保存并译码由计算机传来的 16位命令字,配置 AD转换控制模块和地址输出模块的工作方式。这 16位命令字包含要采集的模拟通道数、AD7321工作模式和是否允许硬件中断等信息。 4)AD转换控制模块。该模块可输出 AD7321所需的 SPI总线接口、片选信号和 8.3MHz时钟信号,其内部主要由一个状态机和两个 16位移位寄存器组成。其中移位寄存器可以将 AD7321送来的 16位串行数据转换为并行数据存入 FIFO中,也可以将命令寄存器模块中的配置数据串行的发送给 AD7321芯片,状态机将两次 AD转换的间隔时间设置为 2μs。

5)地址输出模块。该模块提供多路模拟开关的片选和地址信号,其内部主要由一个地址计数器组成,当 AD转换控制模块完成一路数据的采集时它会自动加 1。 6)PLL和四分频模块。 PLL是 FPGA的模拟锁相环,它工作于 Normal模式下,给其他模块提供全局时钟信号。四分频模块用来对 33MHz的时钟信号四分频,产生 AD转换控制模块所需的 8.3MHz时钟。

在设计中需要特别注意的是异步时钟域之间的数据同步问题,尤其是 AD转换控制模块和 FIFO之间的数据传递。本文中参考了通常所说的用寄存器打两次的方法,在 33MHz的时钟域中采用两个寄存器采样 AD转换控制模块的控制信号,并利用一个同或门检测两个寄存器输出是否一致,再根据同或门的输出信号就可以实现这两个模块之间的数据传递。

2.2 PCI驱动程序设计

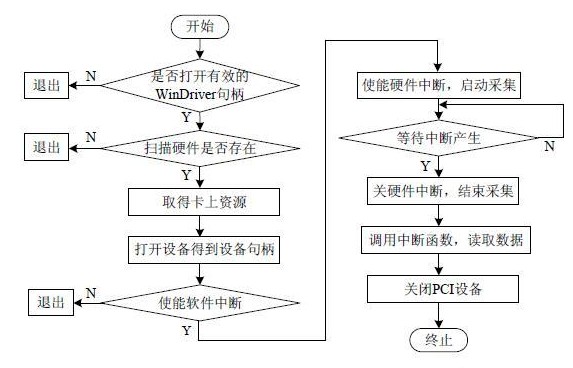

硬件系统一般都需要软件的支持才能实现系统的设计功能,驱动程序就是控制硬件设备的一组函数。本系统的驱动程序的开发使用的是 Jungo公司的 WinDriver集成开发包,它可以自动生成设备的信息定向文件.INF和系统文件 WINPNP.SYS。利用 WinDriver 9.01开发设备驱动程序时,驱动程序中的所有函数都是工作在用户态下的,因此不需要熟悉操作系统的内核。本文在 Visual C++ 6.0的平台下,通过一个动态链接库 wdapi901.dll调用 WinDriver提供的 API函数来编写设备的驱动程序,实现了用户程序对硬件的操作。其软件流程图如图 3所示。

3实验结果与分析

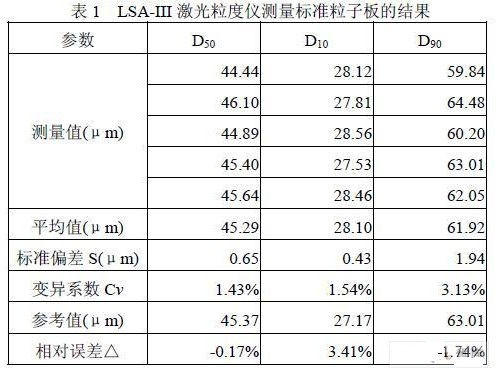

由天津大学研制的 LSA-III型激光粒度仪可测粒径范围为 6μm-2000μm,其光电探测器由 32个同心光敏环和 1个位于中心的光敏点组成。由于本系统可以软件选择模拟通道数,因此只要将计算机发送到命令寄存器模块中的命令的模拟通道数改为 33就可以应用到该仪器上。在 LSA-III型激光粒度仪上使用焦距为 300mm的傅立叶物镜对标准粒子板进行测试,利用 R-R分布模型处理得到的数据,对标准粒子板测量 5次的试验结果如表 1所示。其中 D50表示小于该直径的粒子体积占粒子总体积的 50%,D10和 D90的意义与此类似 [5]。变异系数 Cv和相对误差△是 ISO13320标准的指标,其中 Cv用来衡量测量的重复性,△用来衡量测量的准确性。

由表 1数据可知, D50的变异系数和相对误差均在1.5%以内, D10和 D90的变异系数和相对误差均在3.5%以内,符合 ISO13320标准对重复性和准确性的规定。试验表明该系统在对颗粒粒径的测量中表现稳定,结果准确,完全满足了激光粒度测试系统的要求。

4结语

本文创新点:本文以 FPGA为核心为 LSA系列激光粒度仪量身定制的数据采集系统,实现了 PCI总线方式的数据采集与传输。系统可在 0-112路范围内软件选择模拟通道的采集路数和 AD7321芯片的工作方式,这使得系统具有了一定的通用性,适应了目前光电探测器越来越复杂的趋势。将该系统应用到 LSA-III型激光粒度仪上时,系统对光电探测器的采样速率可达到 7.5Ksps,数据平均传输速率可达到 3Mbps。另外,由于设计中贯穿了 SOC的设计理念,系统还具有集成度高、成本低、升级方便、使用灵活等优点。该项目已经在激光粒度仪中得到应用,产生的直接经济效益达 6万元。