给缓冲放大器变固定电平信号,然后再经去噪后送给带通滤波器。在压展工作模式下,滤波器输出信号应送给压展A/D转换器。

接收部分有压展和线性两个D/A转换器,分别用于转换从DIN输入的串行数据。所得的模拟信号送到隔离电容滤波器以滤除带外信号。滤波器同时提供(SinX)/X校正以使信号平滑。其输出信号将直接供给耳机放大器,该放大器的增益是可调的,并能提供低功耗的差分输出。

TLV320AC56/57内有一带隙高精度电源电路,参考电压VMID等于Vcc/2,对放大电路和话筒偏置提供相当于1/2电平的虚地,另一参考电压可为MICBIAS提供话筒的电流偏置。图2是它的功能方框图。

2 引脚功能

下面是TLV320AC56/57的引脚功能说明。其中各引脚后的括号内分别是DIP-20和PT-48脚封装的引脚号,×表示该封装无此引脚。

AGND(×/34脚):所有内部模拟电路地;

AVcc(×/4脚):所有内部模拟线中的3V供电电源;

CLK(11/19脚):时钟输入,在固定比特率的情况下,它可作为主时钟、发送和接收数据的时钟,在可变比特率条件下,CLK仅作主频时钟用;

DCLK(7/14脚):固定或变比特率选择端。DCLK与VCC相连时,选择固定比特率模式;DCLK不与VCC相连时,选择可变比特率模式,这时,DCLK是接收数据时钟;

DGND(×/27脚):所有数据线路的接地端;

DIN(8/15脚):接收数据输入端,在固定比特率模式下,接收数据时钟频率的波形负波时,接收数据输入;

DOUT(13/21脚):发送数据输出端,当发送数据时钟的正半波时发送数据;

DVCC(×/9脚):所有内部数据线路的3V电源;

EARA(2/44脚):耳机输出端,与EARB组成差分驱动输出;

EARB(3/45脚):耳机输出端,与EARA组成差分驱动输出(模拟信号输出);

EARGS(4/46脚):耳机输出增益设置输入端,一个外部电阻电压分配网络联EARA和EARB两端,其电压分配比率决定着功率放大器的增益。当EARGS与EARB相连时,增益最大;EARGS与EARA连接时,增益最小。外接RC网络可校正耳机的频率响应;

EARMUTE(10/17脚):耳机输出静音控制信号输入端,当EARMUTE为低电平时,输出放大器静止,无音频信号输出;

GND(16/×脚):内部线路接地端;

LINSEL(15/26脚):线性模式选择输入端。当它为低电平时,选择线性编/译码工作方式;当处于高电平时,选择压展编/译码模式。XX56压展码采用μ律,XX57采用A律;

MICBIAS(20/42脚):话筒偏置,对驻极体话筒,MICBIAS电压等于VMID;

MICGS(19/41脚):内部话筒放大器输出端。通常作为反馈信号用作话筒放大器的增益控制,如果需要附加音响,可在MICGS和EARGS(模拟)之间接一个电阻网络;

MICIN(18/40脚):话筒信号输入端;

MICMUTE(6/11脚):话筒输入静音控制信号输入。当此信号为低电平时,发送的数字信号均为0;

PDN(1/43脚):电源控制信号输入端,当此信号为TTL低电平时,系统将降低电源电压,以减小能量的损耗;

TSX/DCLKX(14/22脚):发送时间通道选通或发送通道的数据时钟输入端。在固定比率模式下,该引脚的一个开漏极输出并直接到地。通常也作为三态缓冲器的使能信号。在可变比特率条件下,DCLKX是数据时钟的输入端;

Vcc(5/×脚):所有内部线路的3V电源;

VMID(17/36脚):VCC/2偏置参考电压,在该端接入一个4700pF~1μF的低损高频电容到地可作滤作用。

3 工作过程

在电源正常工作时,TLV320AC56/57可在下列情况下进行初始化操作:

(1)接地;

(2)接通VCC;

(3)接通所有的时钟信号;

(4)将PDN接至TTL高电平;

(5)把同步脉冲加在FSX和FSR端。

该芯片对死机设计有很好的保护。但当电源状况不符合要求时,死机的情况仍有可能发生。辚帮助确认死机情形,在电源VCC与GND之间应反接一个二极管,它的正向压降应等于或小于0.4V(可选用1N5711或等同元件)。

在发送通道加上或打开电源开关时,DOUT和TSX在大约4个帧时间内(约500μs)保持高阻态,然后,DOUT、TSX和其它信号均有效,并在各自的时间通道中处理信号。因为自动清零线路的原因,发送端模拟电路约需60ms达到平衡。为进一步完善系统,当CLK中断时,DOUT和TSX应置于高阻态。

音频信号是模拟信号,是通过麦克风捕获到的变成为一定电平的信号。它是时间的连续函数。我们知道这个信号振幅就是音量,频率就是音调。一般来说人耳可感受的正弦波的范围是从20 Hz 的低频声音到20 000 Hz 的高频声。把这样的模拟信号转变成计算机以及网络能够接受的数字信号的第1 步是对模拟信号进行采样,使其成为时间的离散函数。

为了以后恢复模拟信号的原貌,采样频率应该不低于模拟信号最高频率的两倍(Harry Nyquist 定理)。第2步就是对采样来的离散信号进行编码即所谓的脉冲编码调制(pulse code modulation,PCM),也就是用二进制码来表示每个离散信号的幅度。硬件实现上主要是由采样保持器和模数转换器来完成的,即构成一个音频输入设备。

TLV320AC56/57系统可提供低电平工作和三种等待模式。当一个外部低电平信号加在PDN时,系统将关机。没有信号时,PDN内部上拉至高电平以使系统保持活性。在低电平模式下,系统的电源消耗仅为2mW。

将DCLKR接至数据接收时钟即选择了可变比特率工作方式,同时也选定了接收时钟频率。在这种模式下,主时钟控制开关电容滤波器,从而DIN和DOUT端的输出则分别由DCLKR和DCLKX来控制,TLV320AC56/57允许系统以低于时钟频率的任何速度传输数据,但DCLKR和DCLKX必须与CLK同步。

采集来的音频数据有着相当巨大的数据量,如果不经过压缩,保存它们需要大量的存贮空间,传输起来也比较困难,很自然,人们想到了压缩。可以说,这一环节在数字音频技术中占有特别重要的地位。目前常用的压缩方法有很多种,不同的方法具有不同的压缩比和还原音质。编码的格式和算法也各不相同,其中某些压缩算法相当复杂,普通程序不可能去实现其编解码算法。

当FSX输入高电平时,在DCLKX的正半周将由DOUT端将数据发送出去。当FSR为高电平时,在DCLKR的负半周,由DIN接收数据,在可变化特率模式下,如果DCLK有振荡信号,且FSX保持高电平,则在一帧的时间通道内,DOUT上的数据字是重复的。

为了避免因中断而引起的串音干扰,芯片使用了单独的数-模转换器、滤波器和通道参考电压,这使得两个通道可以完全独立运行。主时钟、数据时钟和时间通道的检测必须在每一开始的时候同步。

芯片内部产生的精确带隙参考电压可为发送与接收通道提供所有的参考起泡沫。在制造过程中,芯片的每一通道的增益都已得到调整。从而保证了在外部电压和温度变化时增益的稳定性。

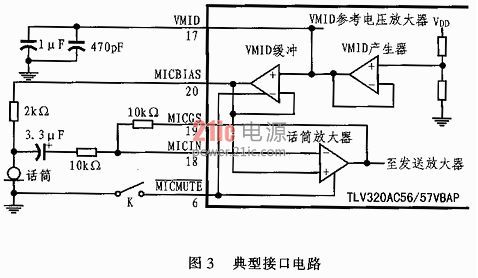

4 应用接口

TLV320AC56采用的是μ律(压展模式),相当于CCITT G.711标准。而TLV320AC57则采用A律,相当于CCITT G.711标准。在线性模式下两者相同。且输入放大器的接口与驻极体话筒完全兼容,其典型接口电路如图3所示。话筒放大器的输出MICGS通常与反馈网络相连,该信号同时加在放大器的反相输入端以稳定放大器的增益值。VMID端可用于滤波器的接入。而MICUMUTE端上的开关K可用来对话筒静音进行控制。

相关文章

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服