今天给大家分享的是施密特触发。

本文引用地址:主要是关于:

1、搭建的

2、如何设计施密特触发电路?

3、怎么改进晶体管施密特触发电路

一、有什么作用?

是一个决策电路,用于将缓慢变化的模拟信号电压转换为2 种可能的二进制状态之一,具体取决于模拟电压是高于还是低于预设阈值。

二、不能用 CMOS 来设计施密特触发器吗?

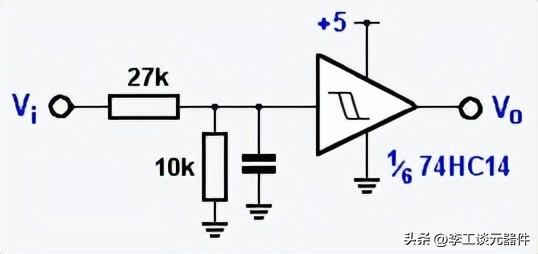

CMOS器件

CMOS 器件可以用来设计施密特触发器,但是不能选择阈值电压,只能在有限的电源电压范围内工作,例如:4HC14 在 +5v 下运行,阈值通常为 2.4v 和 1.8v。

或者你也可以使用比较器芯片,通过额外的分立电阻定义阈值。

74 CH14

如果你需要处理嘈杂或者失真的数字信号,可以使用 CMOS 器件。但如果你要求不寻常的电压或者精确的阈值,就需要设计一个特殊的电路。

三、双晶体管施密特触发器及其工作原理

假设输入电压 Vi 接近于 0,T1 没有基极电流,所以 T1 处于关闭状态。T2 通过 R1和 RA 汲取基极电流,因此 T2 处于开启状态(并且根据设计,T2 是饱和的 - 集电极-发射极电压 Vce 接近于零),因此 Vo 位于由下式形成的分压器的中点 R2 & RE,介于 +V 和地之间。

双晶体管施密特触发器

现在假设 Vi 开始增加,T1 的发射极电压由流入 T2 的电流保持固定,因此当 Vi 达到高于该值 0.6v(称为VP)时,T1 将吸收一些基极电流并开始导通。

这个时候,T1 开始使 T2 缺乏基极电流,因此 T2 开始关闭,因此其发射极电压开始下降。但这会增加 T1 的基极-发射极电压,因此 T1 会更快地开启。正反馈使电路进入 T1 开启(并且设计为饱和)而 T2 关闭的状态,Vo 现在靠近 +V。

最后,假设 Vi 开始回落到 0,T1 的发射极电压现在由其自身的发射极电流控制。当 Vi下降到高于该值约 0.6v 时(称为 Vn ),T1 将开始关闭,这允许 T2 再次开始开启,将其自己的发射极电流添加到 T1 的,从而向上推动发射极电压。这迫使 T1 更快地关闭,并且正反馈再次使电路快速进入其他状态,T1 关闭,T2 开启。

阈值和电流

这里需要强调一下重要的设计约束。假设 Vi 从零开始缓慢上升,并达到 T1 开启的阈值。该阈值 ( VP ) 由流经 Re 的 T2 的发射极电流设置。一旦 Vi 达到 VP,T2 就关闭,通过 RE 的电流现在通过 T1。

假设该电流大于来自T2 的电流。如果是这样,T1 的发射极电压会在 T1 开启时突然升高。但随后 T1 会突然发现其基极电压 ( Vi ) 现在小于其新的发射极电压,并会立即关闭。但随后它的发射极电压会再次下降,因此它会再次开启。换句话说,电路会振荡。

因此,必须确保 T1 中的电流(I1)小于 T2 中的电流(I2),否则电路将无法工作。

并且由此得出,T2 再次开启的阈值(Vn )必须低于 VP。这两个阈值之间的差异被称为电路的“滞后”,类似于变压器铁芯中发生的情况。

四、如何设计晶体管施密特触发器?

设计一个电路来数字化这种嘈杂和失真的信号,提供+5v 和+24v 的电源轨,输出信号必须与在 +5v 下运行的数字逻辑兼容。

如果可以调整输入信号以适应 +5v 电压轨,则可以使用基于 CMOS 逻辑(例如 HC14)的施密特触发器,也可以使用比较器。

但这里显而易见的方法是使用 +24v 电源轨的基于晶体管的设计,我主要会选择几个容易获得的 30v npn 开关。

1、确定阈值 VP

从波形上看,它可能应该在 12 或 13v 左右。

2、选择 在T2 中流动的电流

较低的值可以节省能源,但意味着集电极负载电阻的值较高,这可能会减慢开关边沿。

现在在 T2 选择 3 mA ,那么发射极电阻 RE : [12v / 3mA] = 4k,使用 3.9kΩ。

接下来,R2: [(24v - 12v) / 3mA] = 4k,这里使用 3.9kΩ。

电流电压计算公式

3、选择 T1 的集电极电流,从而选择较低的阈值电压VN

噪声尖峰比较麻烦,I1: [9v / 3.9kΩ] = 2.3 mA 时,将目标设置为 9 或 10v 左右,这将产生大约 4v 的滞后。

R1:[(24v - 9v) / 2.3mA] = 6.5k,使用 6.2 kΩ。

R3 限制 T1 的最大基极电流,最大基极电流可以为: [2.3mA / 30] = 77μA(因为晶体管的电流增益不会低于 30)。

R3: [(24v - 9v) / 77μA] = 194k,使用 180kΩ。(假设电路由零阻抗电压源驱动,如果不是,则可以从 R3 中减去源阻抗。)

RA & RB:RA 用于在 T1 关闭时限制 T 2的基极电流,而 RB 确保不受温度影响。

这两个电阻形成一个分压器,它必须将 T2 的基极设置为(例如)12.6v,T1 关闭,并吸收明显高于 T2 基极电流的电流,该电流不能超过 [3mA / 30] = 100μA。

选择通过 RA 和 RB 的泄放电流为 500μA 左右,使其远大于 T2 的基极电流。

那么如果 R1 为 0 ,RA+ RB :[24v / 0.5mA] = 48kΩ。

分压器中点为 12.6v,[ RB / ( RA + RB )] = [12.6v / 24v] = 0.53,这意味着 RB = 1.1 RA。

RB: [48k x 1.1/2.1] = 25k ;RA: [48k - 25k] = 23k。

但是 R1 不是零,而是 6.2kΩ,因此 RA 的实际值为 [23k - 6k] = 17k。因此,将值四舍五入,因为更多的电流无关紧要。

RA = 15kΩ 和 RB = 22kΩ。

五、晶体管施密特触发器

现在,所有的值都确定,就可以大概开始设计,电路按预期工作,在 12v 和 8v 下切换。

双晶体管施密特触发器(初始设计图)

双晶体管施密特触发器仿真模拟图

该电路的输出从大约 13v 摆动到 24v,而规范说输出电平应该是 0v 和 5v,因此 我需要添加一个由 +5v 电源轨供电的电平转换晶体管来解决这个问题。

最简单的解决方案是添加一个 pnp 逆变器,并且在 15kΩ 电阻 R6(即 RA)上包括一个电容(4.7 或 10nF),使电路开关更快、更干净——输出边沿的上升和下降时间约为 500 纳秒。

双晶体管施密特触发器最终设计如下图所示:

双晶体管施密特触发器最终设计

最终这个电路使用了 3 个晶体管和 9 个电阻,1 个电容。这13个组件占 了很大的PCB面积,可能组装成本也会比较高,应该会有更好的解决方案。

晶体管施密特触发器改进电路

1、晶体管数量不变,电阻数量减少,有效地利用 PNP晶体管的增益

最初的晶体管电路实际上只是具有正反馈的长尾对,像这样画出来,并从第三个 (pnp) 晶体管 T3 获取反馈,就得到了下图所示的电路。它的工作原理与之前的电路类似,只是现在更有效地利用了 pnp 晶体管的增益。

晶体管施密特触发器改进电路

这里使用更少的电阻 - 其中一个仅用于将输出摆幅限制在所需的 5v。

和之前一样,当输入电压 Vi 接近于零时,T1 没有基极电流,所以它处于关闭状态。T2开启(使RC短路),T3 也是如此,输出 Vo 为高电平。

随着 Vi 上升,迟早它会达到足以让T1 开始开启的值。这必须在 T1 的基极电压略高于 T2时发生。RA 和 RB 形成一个分压器,定义 T2 的基极电压,这两个电阻定义了上限阈值VP。

当 T1 打开时,它会关闭T2和T3,输出Vo下降到接近零(假设RC足够大)。

现在假设 Vi 开始下降。当 T1 的基极电压降至刚好低于T2时, T1将再次关闭。该电压由分压器RC - RA - RB固定,并且可以设置在零(如果RC =∞)和VP之间的任何位置。

上述电路的一大优点是 VP和 VN 都由分压器定义,因为它们将在基于比较器的解决方案中。

2、晶体管数量减少,将两个方案合二为一,组件减少 (9个)

最初的设计解决方案过于复杂(13 个组件),因为它分两个阶段解决了问题——首先制造施密特触发器,然后安装电平转换器。

晶体管施密特触发器改进电路

将这两个阶段合二为一并比用 pnp 类型替换 npn 晶体管更简单,该解决方案仅使用 9 个组件。

该电路(几乎)与原始电路完全相同,只是交换了 +24v 和接地。

原电路中+13v 和+24v 的输出电平现在变为+11v 和0v,规范要求 +5v 和 0v,所以我只需要大约一半的可用输出摆幅,我可以通过为 R2A和 R2B 选择合适的值来获得。

3、使用 COMS器件 74CH14 来代替

如果你看到这里的话,应该知道施密特触发电路是如何工作的,并且知道如何设计一个施密特触发器以及怎么去调整。

如果你还想简化电路的话,你可以考虑下面这种方法。当然这并不是一个容易的问题,关键还是取决于你设计的系统类型。

如果输入信号相对较大,并且你要求 VP 和VN 必须相距很远(例如,为了抑制干扰噪声)并且系统已经包含分立元件,则基于晶体管的解决方案可能是 COMS器件。

具体的可以看下面这个电路,设计示例可以通过下面这个简单的电路来解决,但是实际效果怎么样,需要看在实践中的效果。

晶体管施密特触发器改进电路