今天给大家分享的是电源设计。

本文引用地址:一、典型的同步降压控制器

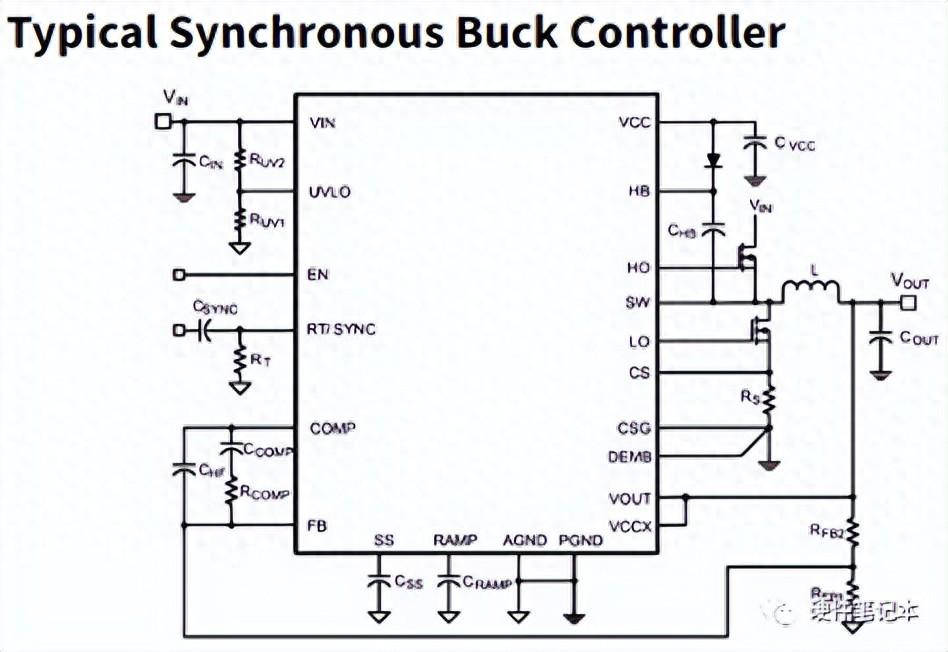

典型的同步降压控制器

上图为典型的示意图。与大很多原理图一样,显示的引脚注释并不代表实际的 IC,它是一个 TSSOP-20。所以在看Datasheet的时候,还是要多注意一点, 不能只看这一个示意图。

二、实际同步降压控制器示意图

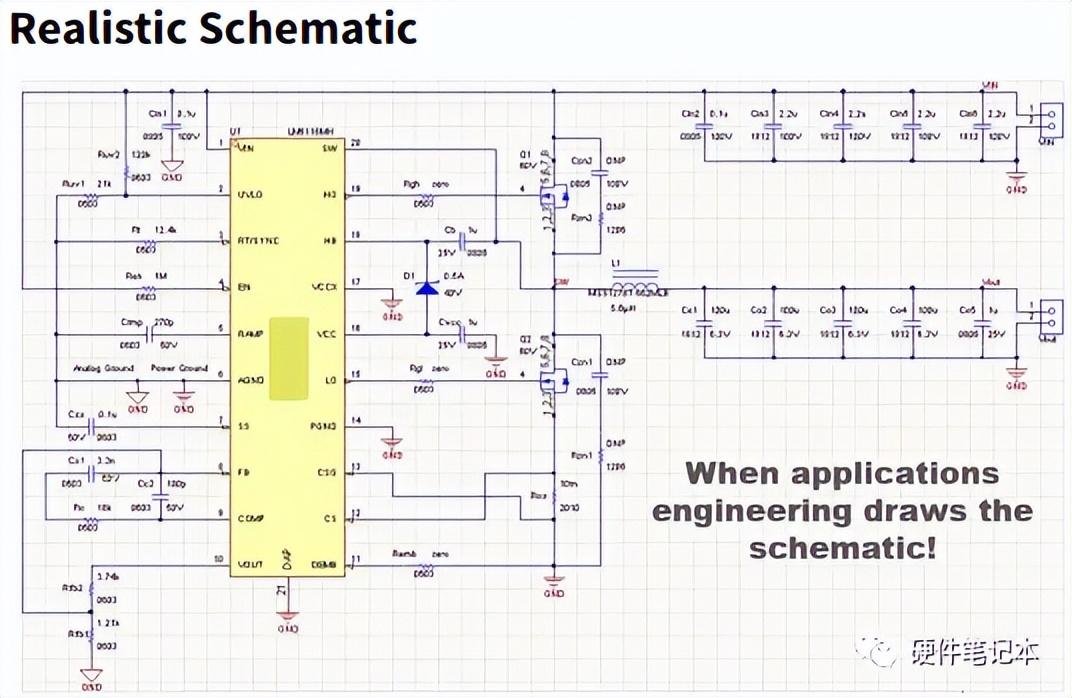

实际同步降压控制器示意图

这里可以明显看到和上面的不一样了。元件在上的电气连接方式有许多名称,不存在标准的一个命名。我一般会先放置开关节点,通常是电感或者变压器绕组以及1-2个电源开关,大电阻 RCS 用于检测电流,它与同步 MOSFET Q2 串联。

下面就会分步教大家来设计。

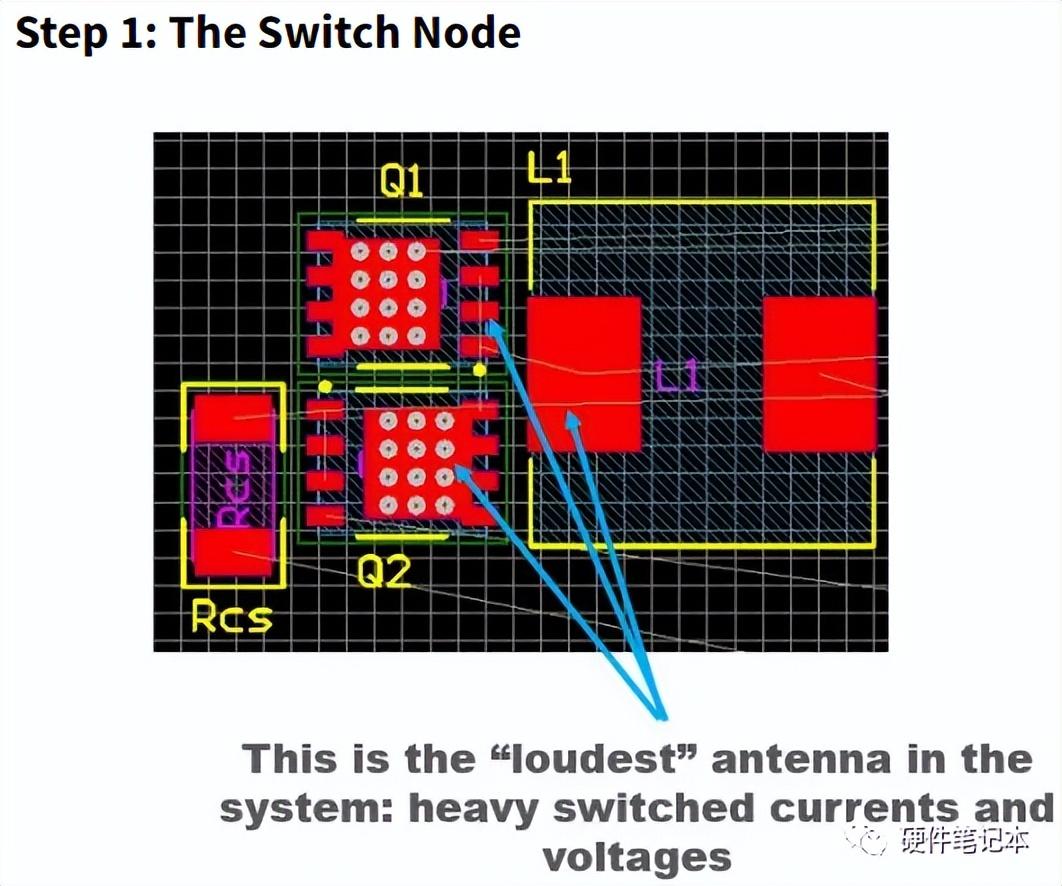

第1步:切换节点

切换节点

开关节点是一个很好的静电辐射器,因为它以一定的开关频率进行震荡。位移电流流动,对自由空间中开关节点和接地平面之间的电容进行充电和放电。一般来说,如果这个节点的面积最小化会更好。

我一般从构成开关节点的功率开关二极管和电感开始,放置在使它们的路径尽可能靠近的位置。然后,放置了一个刚好覆盖所有三个路径的实体形状。

对于除降压稳压器以外的其他稳压器,通过查看高电位摆动的任何节点,寻找方法来最大限度地减少对其它地方的电容。在许多类型中,如反激式或 SEPICS,将有两个开关节点,每个开关节点都需要得到处理。

第 2 步:输入电容组

输入电容组

输入电容、高侧 FET 和低侧 FET 之间的环路需要最小化,这是 Buck 设计中最关键的路径。这里一定要最大限度地减少输出尖峰。并且一定要使用大铜多边形作为与 MOSFET 的主电源连接,这在电气上和热学上都会有帮助(同样这个方法也适用于过孔。)通常越多越好。

通孔还充当电路板背面和内层的热通道。如果可以的话,用焊料填充。虽然在电学或热学方面不如铜好,但焊料比空气好得多。

那个靠近FET的小电容Cin2,是低值 MLCC,通常为 100 nF,主要是为了在降低最高频率的噪声和谐波。低值 MLCC的电容值和物理尺寸都很小,可以最大限度地降低 ESR 和 ESL。在 Cin2 之后,有了更大的 MLCC ,降低了开关频率的输入电压和电流纹波以及更低的谐波。这个电容可以抑制潜在的振荡并在瞬变期间维持输入电压,不过都是低的开关频率,因此这个电容可以放的更远一点。

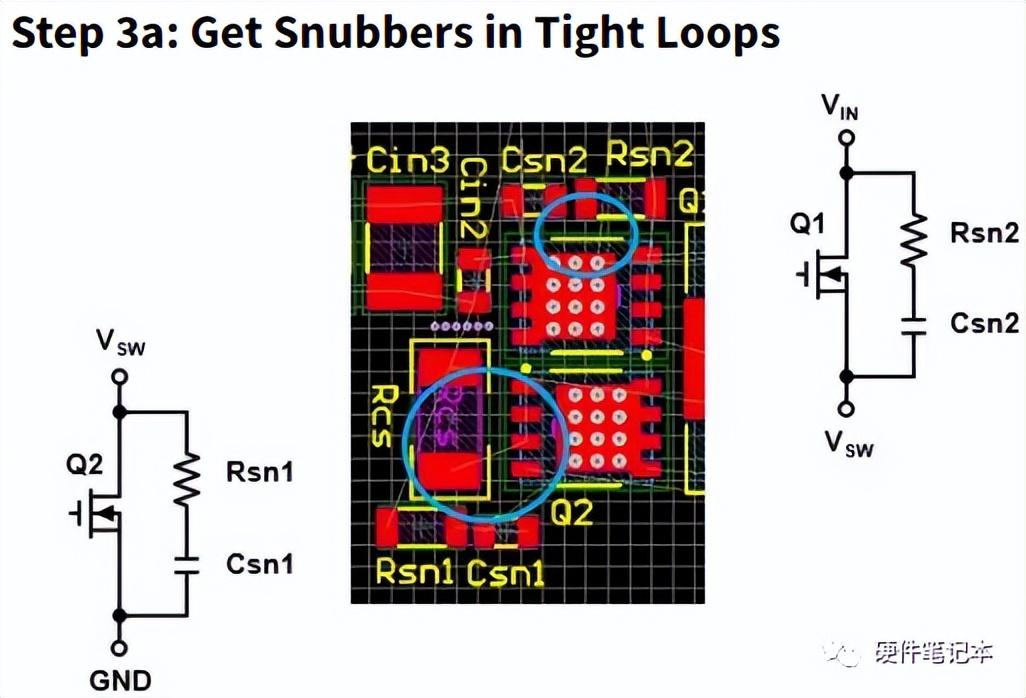

第 3 步:在紧密环路中获得缓冲器

在紧密环路中获得缓冲器

缓冲器滤波器可以降低高频噪声并改善辐射。因为缓冲器处理很高的频率噪声,通常高于 10 兆赫兹。所以它们得以最小的电感进入紧密环路,不然将无法过滤。

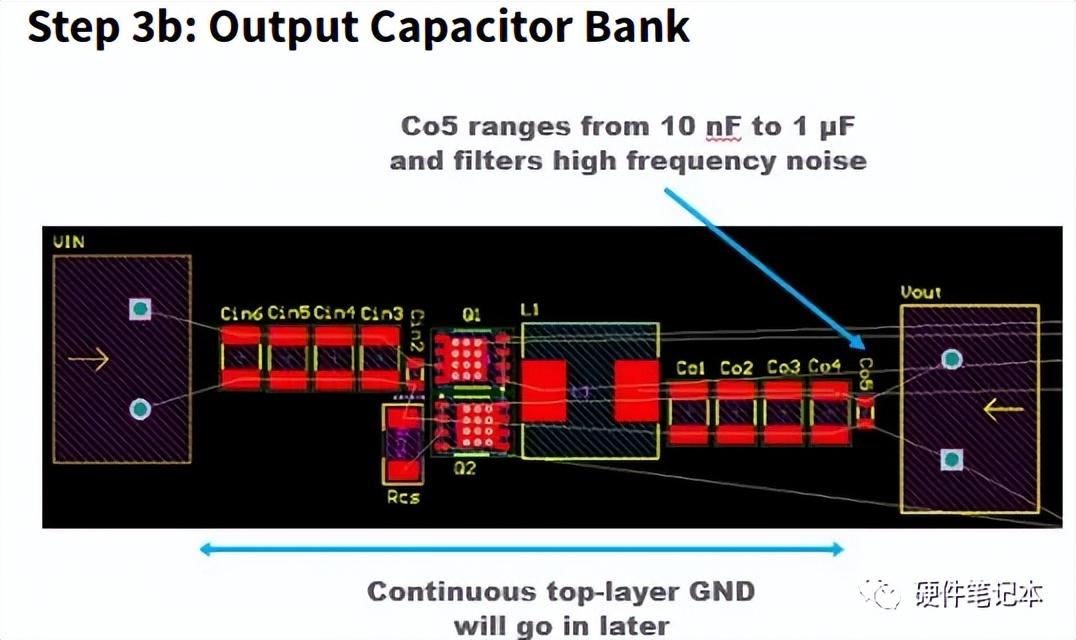

第4步:输出电容组

输出电容组

这里必须要注意,在完整的布局之前,我们必须要注意有关低侧 FET、阳极或二极管。这是一个噪声节点,不应直接连接到地平面。这样做会将噪声注入地平面。这个就好比一群吵闹的孩子在宽阔的操场上。

如果你看到降压稳压器输出出现尖峰,那么这里连接可能不正确。在理想的设计中,降压稳压器的输出几乎没有尖峰。通常,出现在输出端的任何尖峰都是通过地轨传导的。

仔细注意低侧开关接地之间的路径,回到输入电容,输出尖峰几乎可以消除,或者至少大大减少。电感将高频电流和这些元件保持在最低限度。

最小的输出电容 Co5 恰好靠近输出连接器或负载(如果负载位于同一 PCB 上),以在高频噪声干扰负载之前将其清除。如果高频噪声进入输出线束,它会将它们作为天线进行辐射。

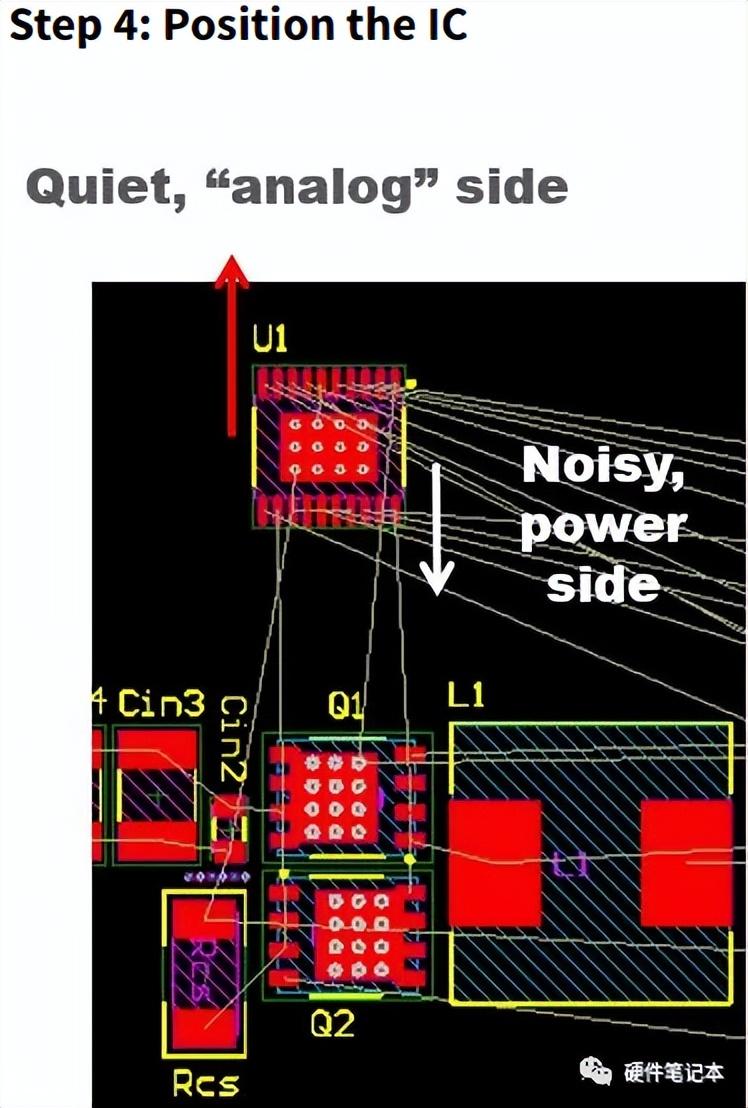

第 5 步:定位 IC

定位 IC

布局良好的 IC 会将噪声引脚(如栅极驱动器)与 IC 一侧的根带引脚组合在一起。然后,敏感的模拟引脚,如对反馈节点的控制或软启动,则位于另一侧。

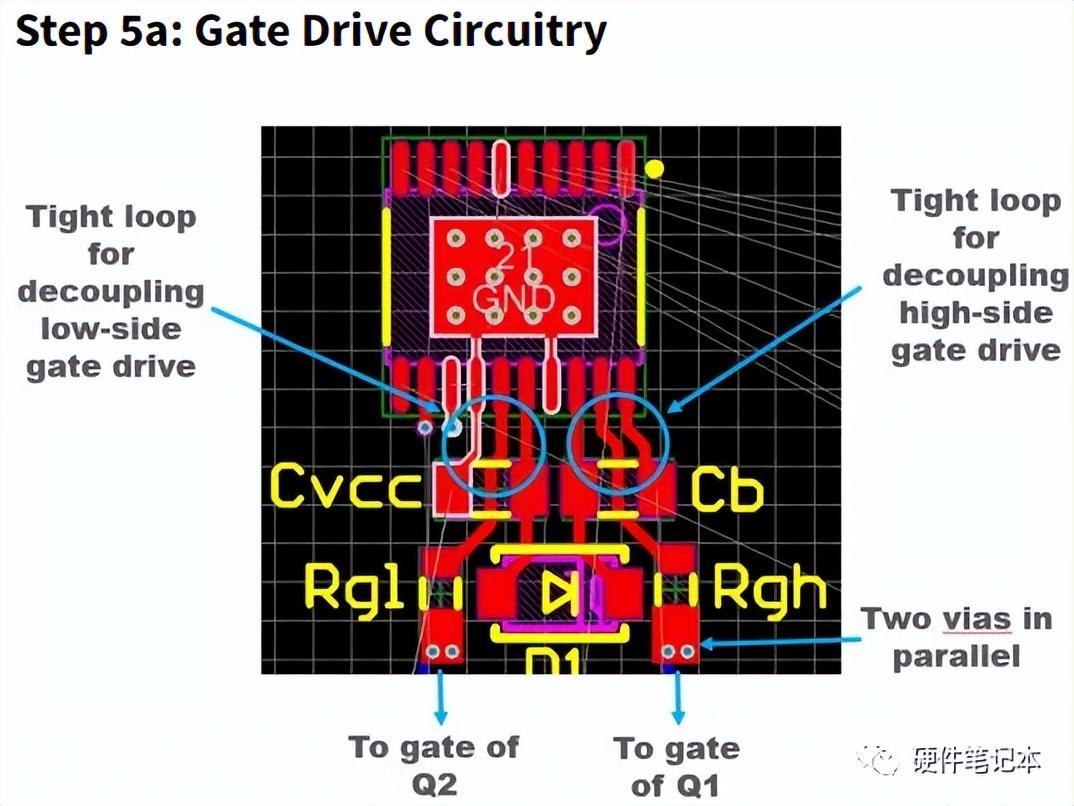

第6步:栅极驱动电路

与外部 MOSFET 的栅极连接是非常高的 DIDD 路径,因此需要仔细考虑。具有大量栅极电荷的大 FET 会产生数安培的峰值电流,此处的长连接会显着减慢 FET 开关的上升和下降时间。这对于降压应用中的高端 FET 尤为重要,因为过慢的边沿会增加开关损耗。

尝试将栅极到驱动器的连接直接放在源极到驱动器的接地连接之上,以尽量减少由此产生的环路所包围的面积,并使用至少 0.3 毫米宽的走线。

我通常是通过两层布线栅极驱动器,所以我将至少两个并联的过孔防止在该路径中的寄生电感中。

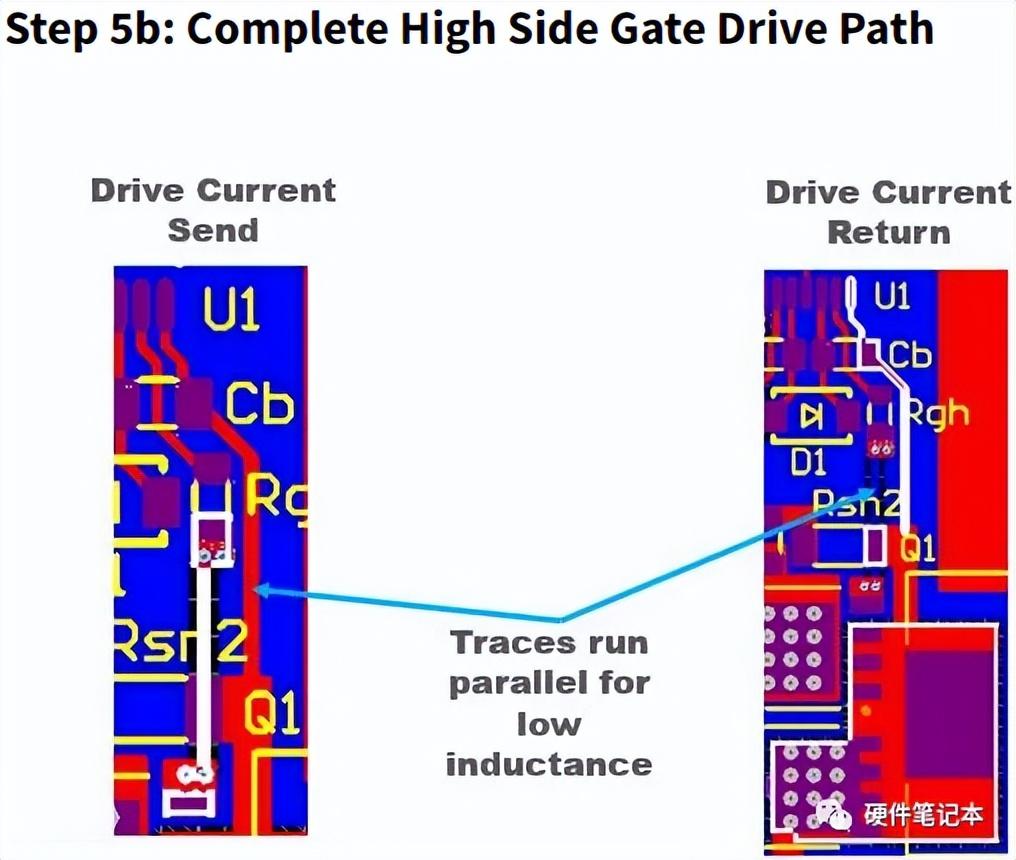

第7步:完成高端栅极驱动路径

完成高端栅极驱动路径

有很多设计在从栅极驱动引脚到 MOSFET 栅极的短、宽、低电感连接方面做得很好,但它是高侧 MOSFET 或低侧,返回路径经常被忽略。

对于高端 FET,返回路径是开关节点。出于散热原因,开关节点通常有大量的散热过孔,可用于将驱动电流带回原处。有时,你可以直接在发送路径下运行返回路径。由于我是在同一顶层布线,所以我选择将它们并联放置在一起,就像差分对一样。

通常,还有一个引导程序,是为 N-MOSFET 产生完全驱动的电荷泵,它的二极管和电容也需要短的、低电导环路。

第8步:完整的低侧栅极驱动路径

完整的低侧栅极驱动路径

低侧或同步 MOSFET 栅极驱动的返回路径通过系统地。这里需要运行一个单独的跟踪。为此,许多控制和稳压器 IC 都有专用的接地引脚,通常称为 P 接地,有时甚至更直接地称为门回路或类似名称。所有这些路径和接地部分之间的物理连接都在 IC 下方。在层间切换时至少使用两个过孔,并尽可能靠近发送路径运行这些返回路径。

第 9步:差分电流检测

差分电流检测

不是每个控制 IC 都有差分感应线,你至少得感应出一个主电流。还有一个问题,就是弟电流检测IC的负极接地。几乎不可能将差分感应线与感应电阻布线在同一层,因此它们必须通过过孔。这次不需要并联过孔,因为电流在RAM 范围内,但是任何实心接地层都会连接到该负侧过孔,同时会导致你PCB走线短路。

通常需要将控制器 IC 的 A 地和 P 地连接起来,即模拟地和电源地,有时称为信号地和电源地,或简称为信号地和地。

第 10步:放置低功率部件

如果你有专门的顶部接地形状的空间,你可以将其用作所有接地参考控制电路、反馈分压器、软启动和控制环路的返回。如果这样的形状不适合,可以使用菊花链从 AGND 引脚连接到各种小信号接地的走线。如果你想通过多层布线此走线,则布局软件会出现问题,因为它想要将过孔连接到内部接地层。而且会引出想要隔离这条痕迹的全部要点。所以,我建议把它放在顶层。

一种方法是提出一个单独的 AGND 符号。你通过多层将所有信号接地点连接在一起,而无需连接到内部平面。但是当连接 AGND 和 PGND,或 AGND 和 PGND 网络时,很可能会产生 DRC 错误。

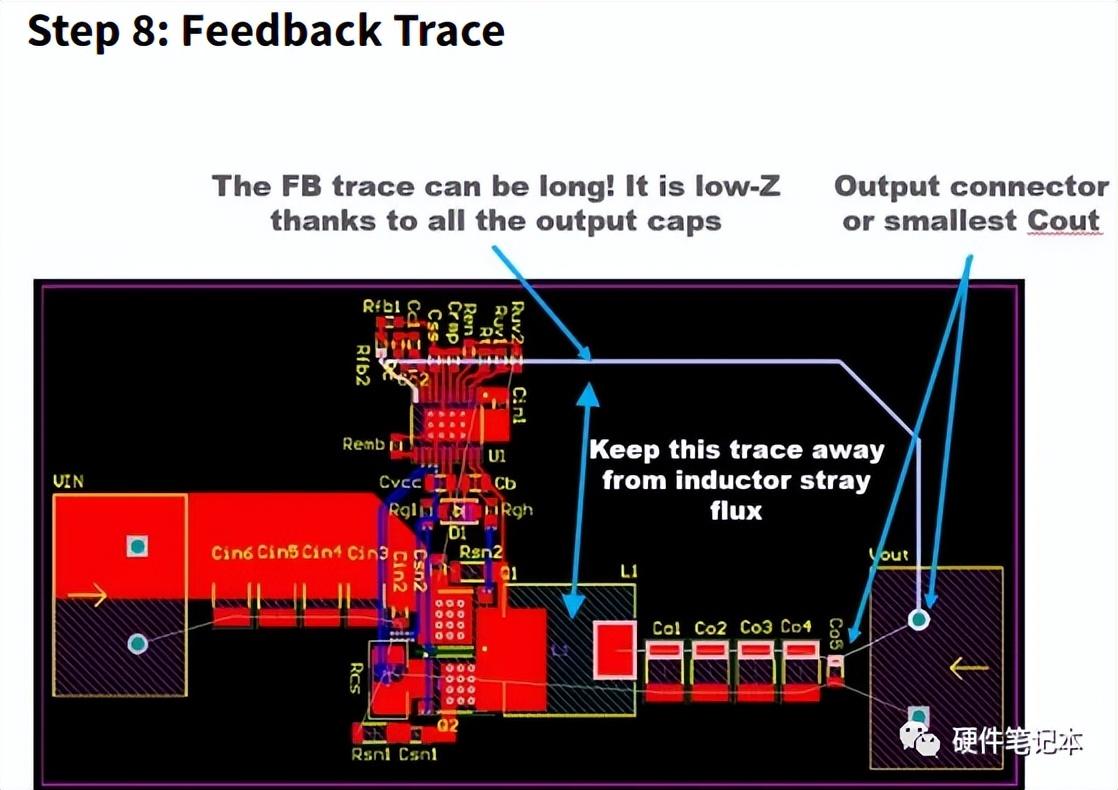

第 11 步:反馈跟踪

反馈跟踪

保持最高阻抗走线较短,因为它们最有可能拾取杂散场。因此,例如,反馈分压器中的两个电阻应位于非常靠近稳压器反馈引脚的位置,而不是电源输出附近。从分压器顶部到电源输出的连接是 Vout,这是一个非常低的阻抗连接,因此不会受到噪声拾取的影响。相反,放大器输入是一个非常高的阻抗输入,并且非常容易受到杂散场感应噪声的影响。

有一种趋势是想让敏感节点变大,还错误地认为这种方法可以提供一些屏蔽的效果,但实际情况正好是相反的。不仅增加了自由空间的电容,并增加了噪声拾取的可能性。使敏感走线变窄并尽可能短。

第12步:顶部敷铜

顶部敷铜

淹没未使用的 PCB 区域的技巧是确保连接到安静的节点。

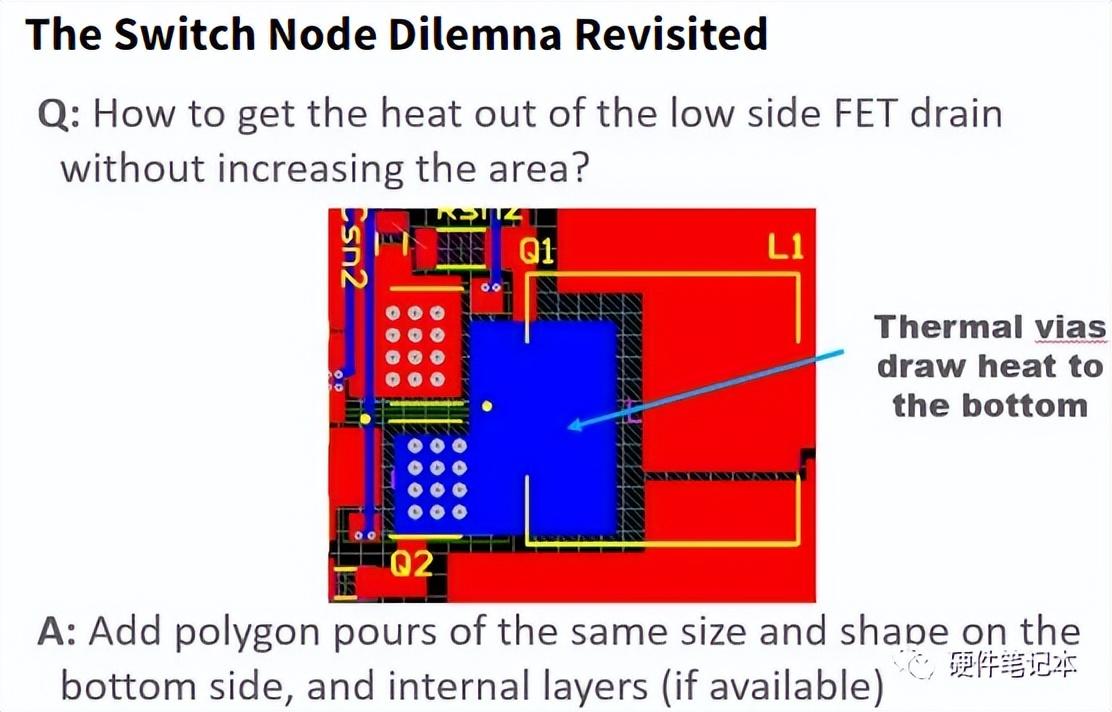

第13步:重新审视切换节点

重新审视切换节点

开关节点非常重要,我们在底层的首要任务是审查热管理和电气噪声之间的这一关键.特别是,低侧 MOSFET 依靠一些单体铜掩膜来保持冷却,因为它的漏极连接到开关节点,而 MOSFET 的大部分热量都从漏极散发出来。这个封装的占位面积是一个热增强型 SO8,内置 12 个热过孔。这里可以在底层放置一个多边形,其形状和大小与顶层多边形相同,刚刚覆盖电感焊盘和两个 MOSFET 的那个。良好的热通孔矩阵将有助于将热量吸收到底层。即使在没有主动冷却的设计中,对流也很可能使一些空气穿过 PCB 底部。

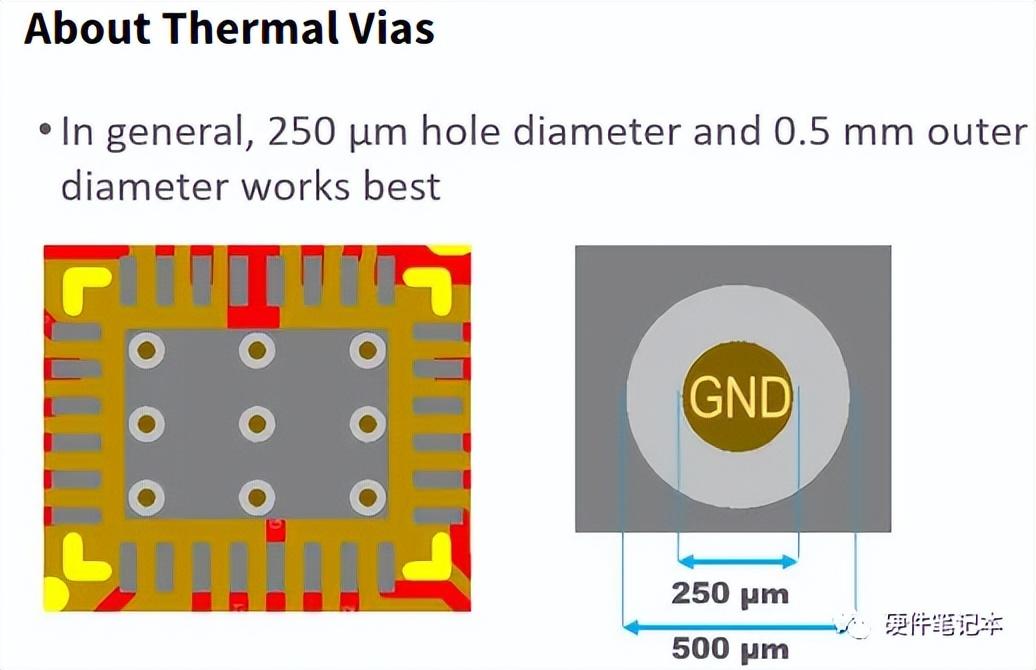

第14步:关于散热孔

散热孔

这是一个PCB 封装,带有一个大散热片。当直接放置在热源下方时,热通孔效果最佳。但同样,这需要与 PCB 制造商进行良好的沟通。我的个人经验是 0.25 毫米的孔与 0.5 毫米的外径相结合,是一个很好的方案。这些尺寸孔偏小,无法吸走太多焊料,但又不算微孔,钻孔成本更高。我通常将它们隔开 1 毫米或 1.5 毫米。

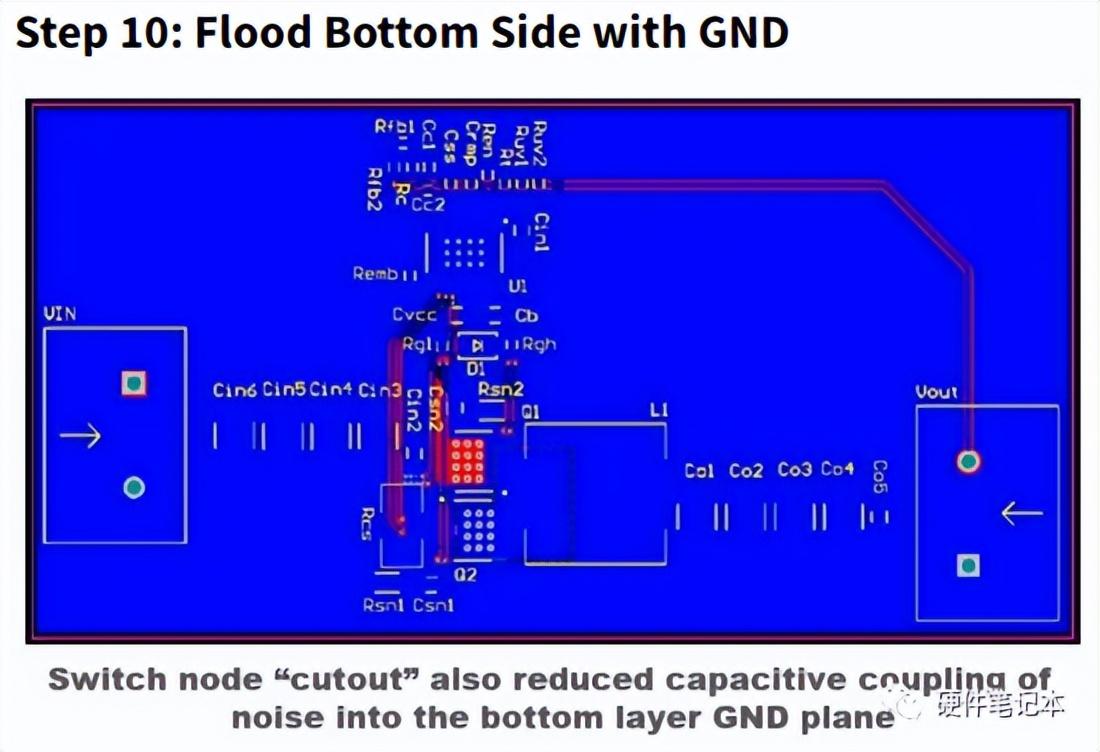

第 15步:用 GND 背面敷铜

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服