时钟初始化是个比较烦锁的过程,流程比较长,其中涉及到大量的端口操作,要理解的基础知识也较多。本文先分析一下时钟初始化的原理,后续再说明如何编程实现该过程。

1. What & Why

很多设备都要求输入一定频率的时钟才可以工作,比较明显的例子是CPU。当然除了CPU外还有其他的设备,可以说时钟是这些设备的心脏,没有时钟它们是不会工作的(切断或降低时钟能达到降频减耗的目的)。在开发板刚启动时,时钟处于一个很低的频率,要我们做一些初始化的工作才能把频率提上去,为设备提供所需的工作时钟频率。这就是为什么要进行时钟初始化。

2. Princeple

时钟初始化涉及到很多电子电路的知识,本人并非该科班出身,只能借助Google做些浅薄的理解。

(1) PLL

PLL (Phase-Locked Loop), 锁相环,主要用于产生与基准时钟同步的振荡信号。

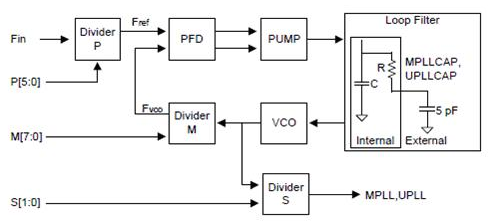

PFD是鉴频鉴相器,PUMP是电荷泵,两个模块组合起来可以通过比较输入时钟信号和反馈时钟信号的频率以及相位来控制环路滤波器(Loop Filter)的电压,从而实现控制VCO(振荡器)的频率,得到我们想要的时钟。P/M/S可以理解成分频器控制逻辑,通过三个控制字,是PLL输出频率的选择更加方便。

总的来说,PLL可以基于输入时钟产生一个新的时钟,该时钟频率可以通过调用P/M/S参数来达到调节输出时钟频率的目的。我们要提高系统时钟的操作可以归结为对PLL的P/M/S参数设置。

(2) AMBA总线

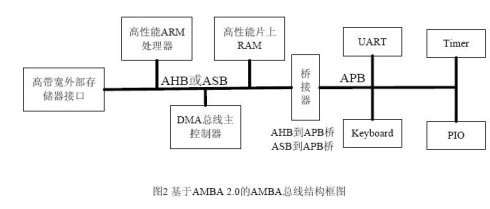

AMBA(Advanced Microcontroller Bus Architecture)总线规范是ARM 公司设计的一种用于高性能嵌入式系统的总线标准。AMBA 总线是一个多总线系统,AMBA 2.0 规范中定义了三种可以组合使用的不同类型的总线:AHB(Advanced High-performance Bus)、ASB(AdvancedSystem Bus)和APB(Advanced Perpheral Bus)。AHB 总线适用于连接高性能和高时钟频率的系统模块,主要用于连接高性能和高吞吐量的设备, 如CPU、片上存储器、DMA设备和协处理器等。APB 总线适用于连接低功耗的外部设备模块。

典型的基于AMBA 2.0 的SoC核心结构如下图所示:

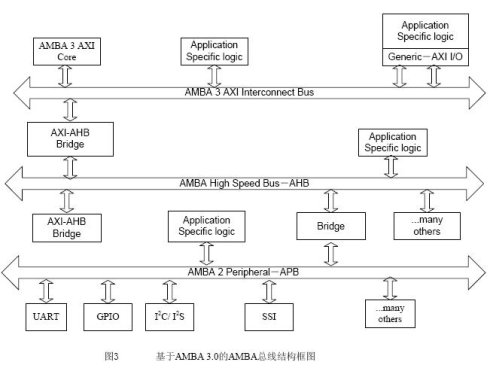

2003 年,ARM 扩展了AMBA 技术的性能与灵活性,发布了AMBA 3.0。AMBA 3.0 包括AMBA 3.0 AXI、AMBA 3.0 APB、AMBA 3.0 AHB-lite 和AMBA 3.0 ATB。基于AMBA 2.0和AMBA 3.0

的AMBA 总线互连结构如下图所示:

(3) S3C6410的三个PLL

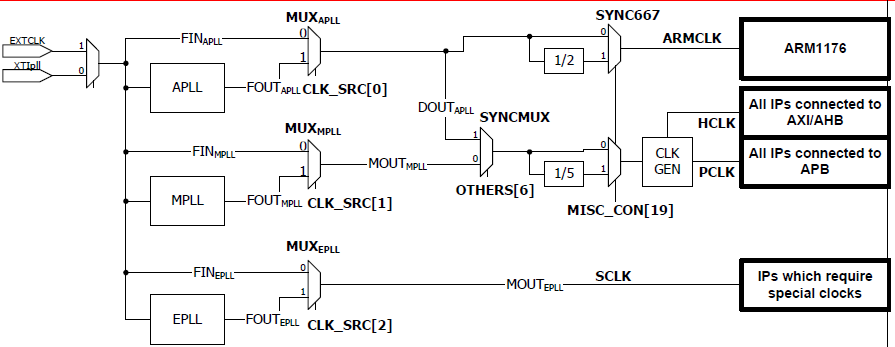

ARM PLL (APLL), main PLL (MPLL), extra PLL (EPLL)

Note:

(1) ARM核的时钟叫ARMCLK,由APLL产生;MPLL产生HCKL和PCLK,HCLK供连接在AXI/AHB上的设备使用,PCLK供连接在APB上的设备使用。EPLL用于一些特殊设备。

(2) ARM1176的最高运行频率是667MHz, AXI/AHB最高运行频率是133MHz, APB最高运行频率是66MHz

初始化时钟系统就是从时钟源头开始,一步步地设置PLL, 多路复用器,分频器等,最终得到目标总线的时钟。

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服