本文编译自福布斯

Synopsys的Sassine Ghazi 首次以CEO的身份登台 SNUG。另外,NVIDIA CEO黄仁勋也在参加完GTC之后,便来到SNUG现场,与Synopsys讨论了公司的合作等事宜。

根据黄仁勋的说法,当NVIDIA公司刚刚起步时,Synopsys就向NVIDIA交付了一箱又一箱的软件手册。如果芯片流片出现错误之后,那么当时作为初创公司的NVIDIA就会破产,因此他们需要 Synopsys 仿真和设计工具来确保芯片开发的万无一失。

一万亿晶体管和埃米的旅程

Sassine和黄仁勋在会议开始时讨论了芯片设计人员面临的挑战,从芯片复杂性到Chiplets小芯片,再到系统设计和芯片设计的交叉点。 下面的幻灯片总结了他们共同取得的成就,如今整个芯片设计工作流程实现了 10-15 倍的改进,且正转向生成人工智能和系统软件。

Nvidia / Synopsys 的合作在生产力和性能方面取得了巨大进步

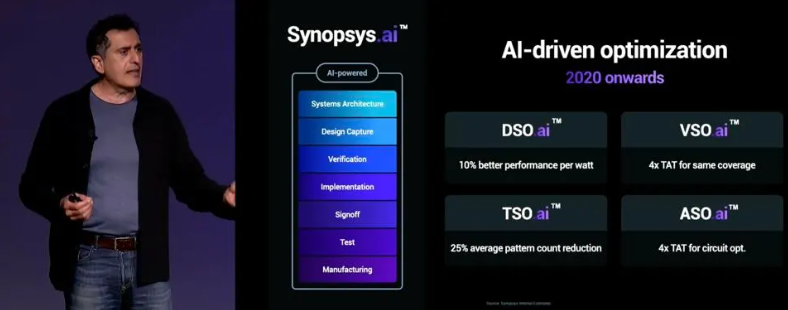

Synopsys 已经通过其首个人工智能增强设计平台 DSO.AI 显着改进了设计,并将强化学习的使用范围扩大到验证、测试和模拟电路设计中。 这些人工智能驱动的工具已在数百个客户流片中使用,并在性能、功耗、面积 (PPA) 方面实现了 10% 以上的提升,周转时间加快了 10 倍,验证覆盖率实现了两位数的改进, 与不使用 AI 的优化相比,相同覆盖范围下的测试速度提高了 4 倍,模拟电路优化速度提高了 4 倍。 他们还在 Design.da、Silicon.da 和 Fab.da 等数据分析平台中添加了人工智能,以实现更好的 PPA 和更高的制造良率。

Synopsys 还构建了 Synopsys.ai,这是一种生成式 AI 解决方案,可帮助芯片设计团队的更多初级成员获得有关无数 AI 工具和云服务产品的问题的答案。 请注意,Synopsys 不会将某些东西称为“生成式 AI”,除非它是使用大型语言模型构建的。 例如,.ai 系列是使用强化学习构建的,该技术在解决布局布线等博弈论问题时仍然是最先进的。

Synopsys 在其设计/验证/测试产品组合中全面嵌入了人工智能

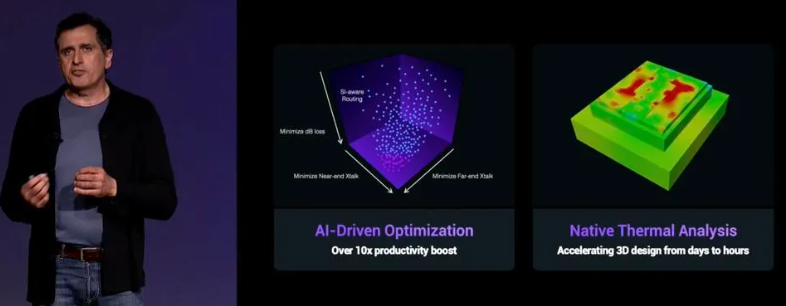

现在该公司正在将人工智能应用到3D芯片设计中。 3D 设计带来了各种热设计挑战,借助面向Multi-Die系统(多裸晶系统)的Platform Architect和Synopsys.ai解决方案的全新功能3DSO.ai,推动Multi-Die设计创新,可以将效率提高多达 10 倍,并在短短几小时内利用本机执行热分析求解器以帮助解决热挑战。

Synopsys 宣布推出用于基于 Chiplet 的设计的新优化和热分析工具

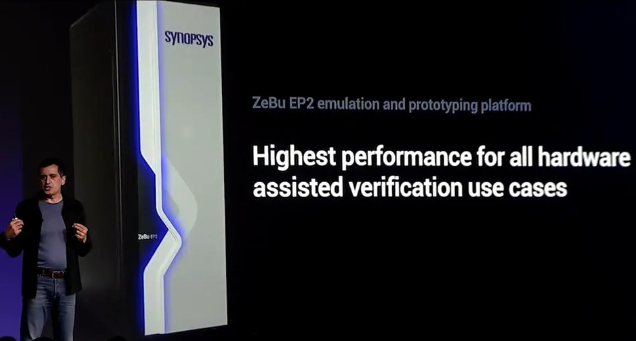

Sassine 还宣布推出一款新硬件 ZeBu EP2 仿真和原型平台,该平台可以仿真高达 56亿门的芯片,这是以前闻所未闻的规模。新的 ZeBu 仿真器用于软件启动、软件/硬件验证以及功耗/性能分析。 如今,没有人通过模拟逻辑和布局来设计芯片。

Synopsys 全新 ZeBu EP2 解决方案,用于硬件辅助验证和原型设计

在硬件辅助验证 (HAV) 领域,Synopsys 还推出了 HAPS-100 12 系统,这是 Synopsys 容量和密度最高的基于 FPGA 的原型系统,通过灵活的互连,特别适用于大型设计的原型设计,例如多芯片系统和大型 SoC。该产品与ZeBu EP2硬件平台共享。

超融合(Hyperconvergence):下一个 EDA 前沿

最后,Sassine 谈到了超融合的概念。 这个想法是,在 EDA 堆栈各层的交叉点上仍然存在大量优化改进。 通过将人工智能应用到这种抽象和模型级别,可以发现和解决这些隐藏的 PPA 机会。 这个级别的人工智能结合在一个紧密耦合的系统中。 AI 可以跨这些层搜索更大的空间,并释放潜在的 PPA 以便进一步优化。 虽然量化超融合人工智能的优势还为时过早,但Synopsys有多个客户已经测试了这一概念和模型。

总结

Synopsys相信,提高芯片的PPA并降低制造复杂度是一个漫长的旅程,有才华、经验丰富的设计工程师需要专注于更多差异化工作,包括在架构和软件层面上进行的设计。 也许一些“简单”的工作,可以完全由AI在少数工程师的监督下进行。