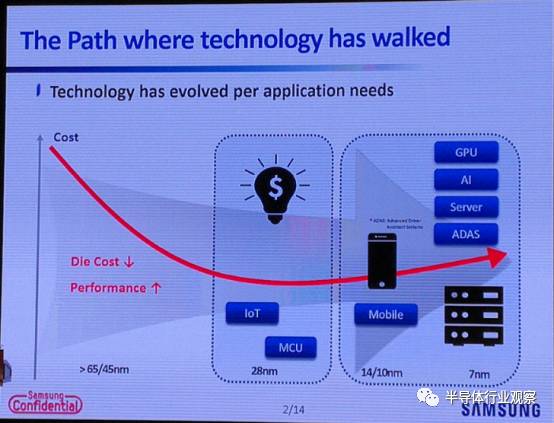

近几年,由于材料和设备的限制,电子产业的金科玉律摩尔定律似乎逐渐走向了瓶颈。尤其是到了14nm之后,以往随着节点往前推进,Die Cost下降而Perforrmance提升的定律被打破,集成电路产业迎来了大挑战。但三星作为一个全球数一数二的IDM,为了继续延续摩尔定律,三星在CSTIC2017上带来了独到的见解。

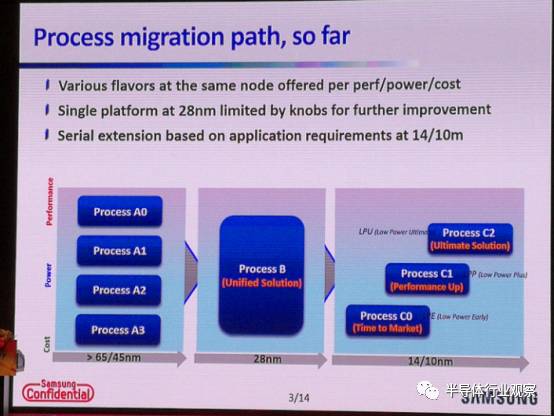

因此厂商们需要针对不同的应用,在相同节点上开发出不同的方案:

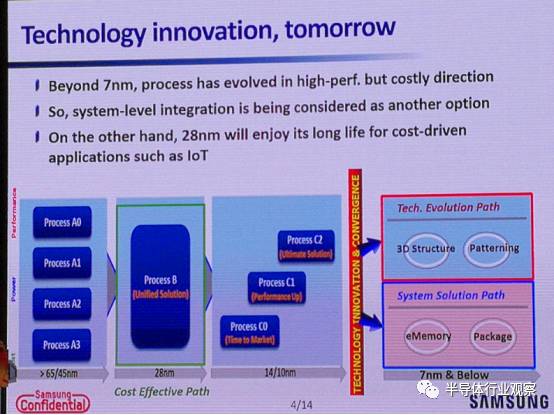

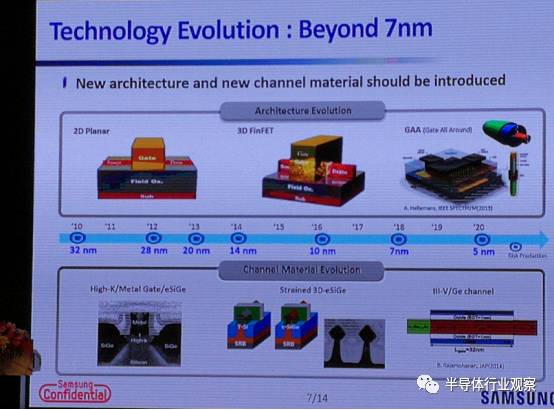

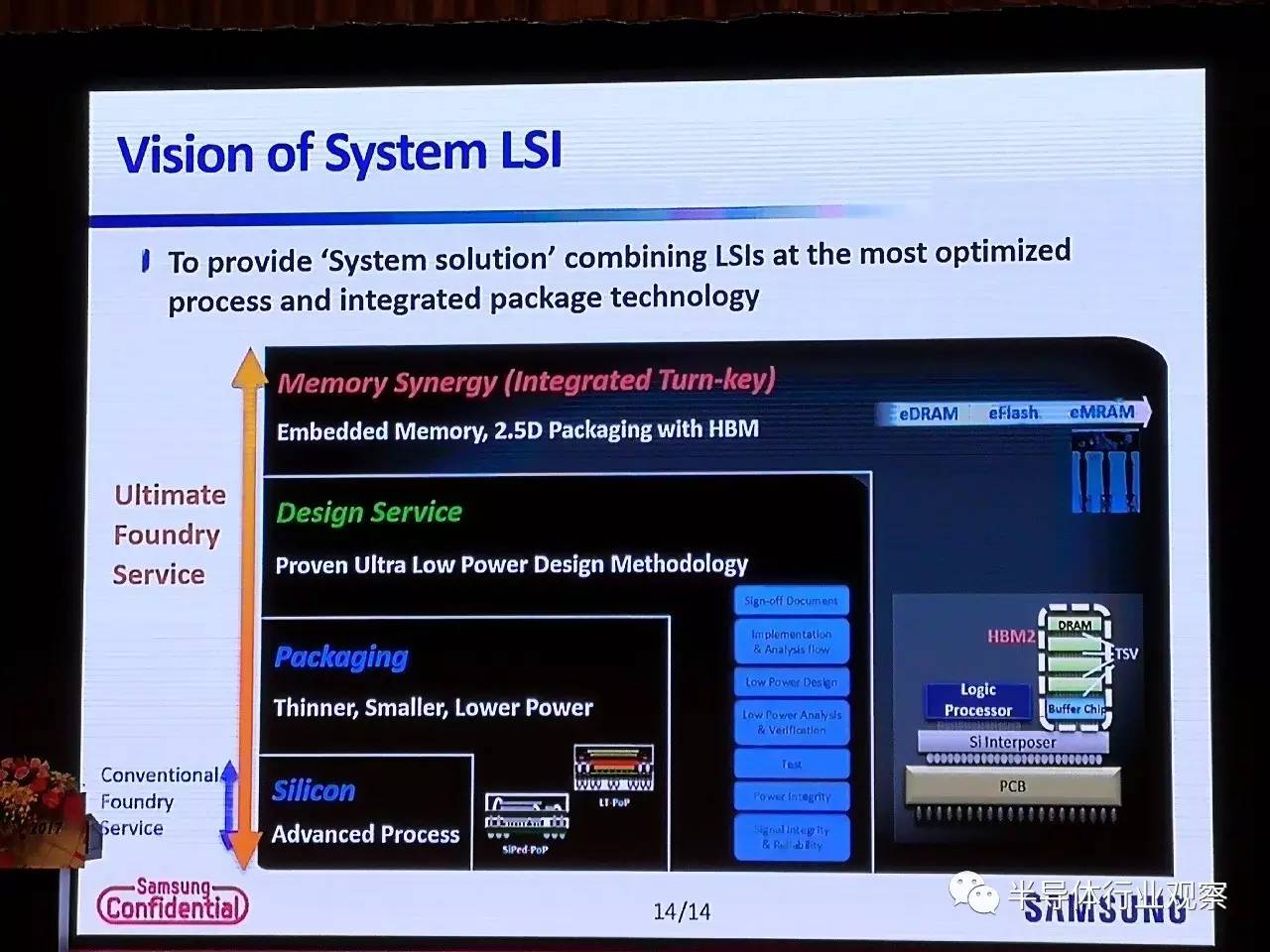

在14nm/10nm的情况下,开发者们还可以在现有的体系下做改进,但是进入到了7nm,则对技术创新有了新的选择。三星需要从两方面创新:一是技术创新,也就是3D结构加patterning;另一种则是系统创新的ememory加packaging。

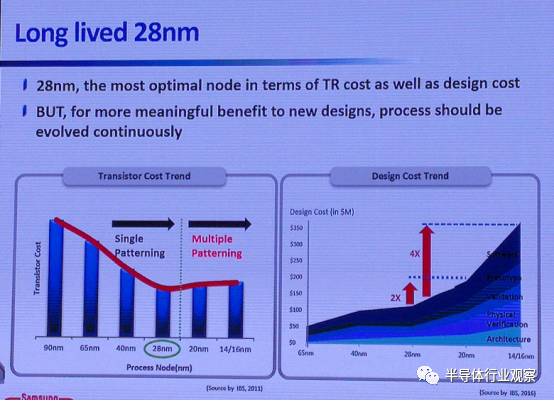

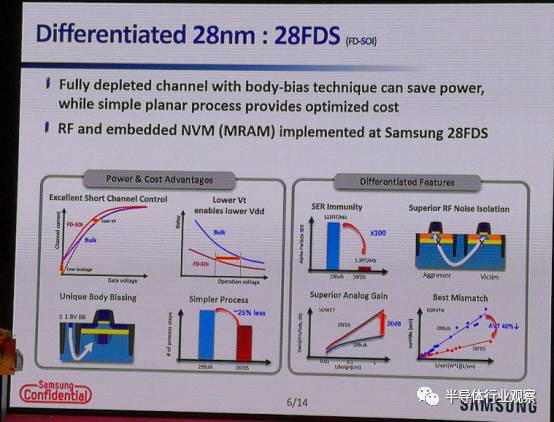

三星认为,移动处理器虽然推动产业界向7nm进展,但是由于物联网的存在和即将爆发,且这些产品对成本很敏感,因此28nm这个甜蜜节点将会存在很长一段时间。

除了传统的28nm,三星认为28nmFD-SOI工艺因为其优势,会成为三星关注的一个重点。FD-SOI最大的亮点在于超低功耗,尤其是对比HKMG(后闸极,约50%+),如今物联网(IoT)、汽车等嵌入开发对芯片的这一特性非常敏感,ST、飞思卡尔等都明确表态支持且等待排片。

7nm之后的架构和材料的创新

回到现在产业界正在紧盯的7nm工艺,三星认为它会在2018年到来,因为沟道变窄了,那就要求在在设计制备的时候需要从架构、沟道材料和工艺制备上进行创新,而GAA、三五族沟道材料和EUV光刻是对应的最好答案。

在这里我们详细介绍一下GAA和三五族沟道材料:

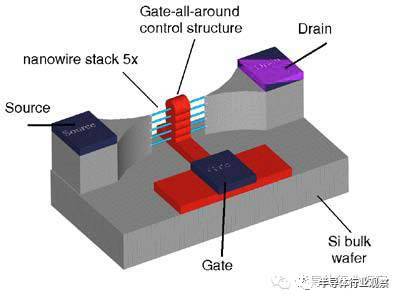

(1)Gate-all-around (GAA)

GAA有时候被称作横向纳米线场效应管。这是一个周边环绕着 gate 的 FinFet 。GAA 晶体管能够提供比 FinFet 更好的静电特性,这个可满足某些栅极宽度的需求。

从表面上看, GAA 和栅极夹杂在源极和漏极之间的 MOSFET 很类似。另外, GAA 同样包含了 Finfet ,但和目前 fin 是垂直使用的 Finfet 不同, GAA 的 Finfet 是在旁边。GAA Fet 包含了三个或者更多的纳米线,形成沟道的纳米线悬空且从源极跨到漏极。其尺寸是惊人的。 IMEC 最近介绍的一个 GAA fet 的纳米线只有 8nm 直径。

控制电流流动的 HKMG 架构能够填补源极和漏极之间的差距。

但是从 FinFet 向 GAA 的转变并不会有很大的优势,当中你只是获得了对晶体管静电性能控制的提升。GAA 最大的提升在于缩小了栅极宽度。这样你就可以得到一个全环绕和一点的静电性能的控制。当然, gate 的缩小是必不可少的。

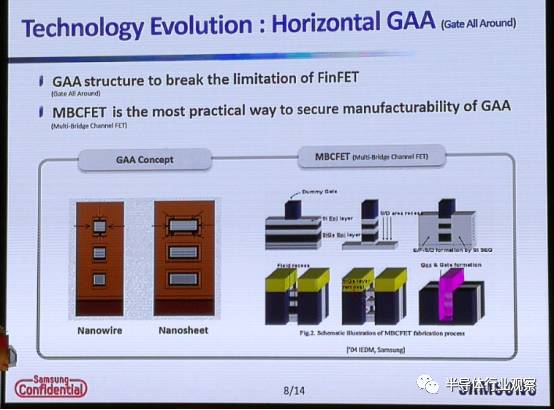

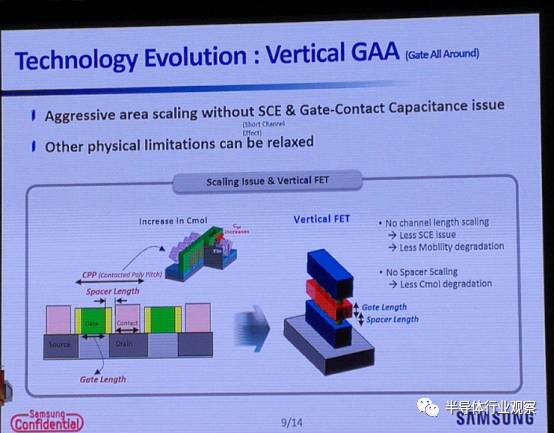

在GAA上,也分为两种方案,一种是水平的,它能够打破FinFET的限制。

另一种是垂直的,能突破更多的物理限制。

(3)EUV

(2)三五族沟道材料

沟道材料这一段时间以来一直是个热门的话题。沟道是一个连接MOS器件源与漏之间的一个导电区域。当一个MOSFET晶体管在导通时栅电容器加在沟道上的电压会产生一个反型层,使少数载流子在源与漏之间很快通过。反之则晶体管关闭。

沟道材料中发生大的改变是在90纳米工艺,那时全球工业界开始引入应变硅材料。芯片制造商采用外延工艺在PMOS晶体管形成中集成了SiGe的应变硅,或者称让晶格结构发生畸变。这样可以通过增加空穴的迁移率来达到增大驱动电流。

芯片制造商在10nm或者7nm工艺时沟道材料必须要作改变。在一段时间中曾认为首选是在PMOS中采用Ge,以及NMOS中采用InGaAs材料。因为Ge的电子迁移率可达3,900cm平方/Vs,而相比硅材料的为1,500cm,InGaAs的电子迁移率可达40,000cm平方/Vs。但是三五族沟道材料受到了厂商的更多关注。

与硅相比,由于III-V化合物半导体拥有更大的能隙和更高的电子迁移率,因此新材料可以承受更高的工作温度和运行在更高的频率下。且没有明显的物理缺陷,而且跟目前的硅芯片工艺相似,很多现有的技术都可以应用到新材料上,因此也被视为在10nm之后继续取代硅的理想材料。目前需要解决的最大问题,恐怕就是如何提高晶圆产量并降低工艺成本了。

(3)EUV光刻

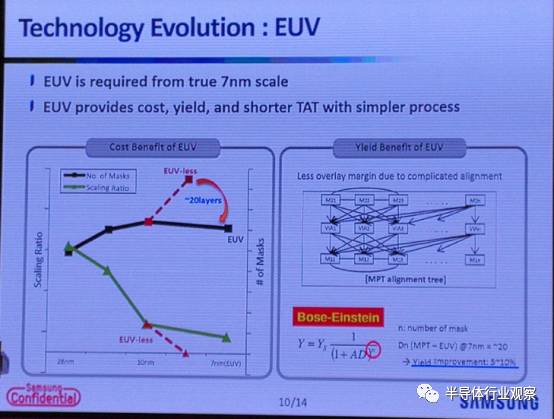

三星认为,到了7nm,EUV光刻是势在必行。

这里我们也说一下EUV光刻。

80年代后期,半导体行业开始用激光代替汞灯作为光源,将波长从365nm 降低到 248nm。但是一些研究者们已经开始计划一个更大的进步——向X射线范围挺近。当时就职于日本电信公司 NTT的 Hiroo Kinoshita 在 1986 年发表了使用 11nm 射线的结果。另外还有 AT&T 公司的贝尔实验室和 Lawrence Livermore 国家实验室也分别实践了这种技术。1989 年,一些相关研究学者在光蚀刻学术会上碰面并交换了研究思想。再后来,相关的研究开始得到国家和行业内的赞助。

90年代后期,ASML 公司和其他一些合作伙伴开始研究后来广为人知的技术——EUV 光刻技术。也是这个时候,在 ASML 公司荷兰总部 Veldhoven 小镇长大的 Anton van Dijsseldonk ,成为了公司开展该项目的第一个全职雇员。van Dijsseldonk 回忆道:“摩尔定律的终点已经被大家所预见到了。半导体行业一直都在寻找方法来保持技术革新和进步。芯片制造商们也在努力改进套刻技术——将晶片从光刻机中加工取出后再放入其中,并在原来的位置精准地印刷出下一层图像。那时的人们都在寻找不同的方法,而 EUV 就是里面较为不同的一个。”

EUV光刻生产中仍有一些设备上的难题亟待攻克。其中就包括对空白检验工具和光刻胶光化学性质的研究。

7nm之后的系统创新

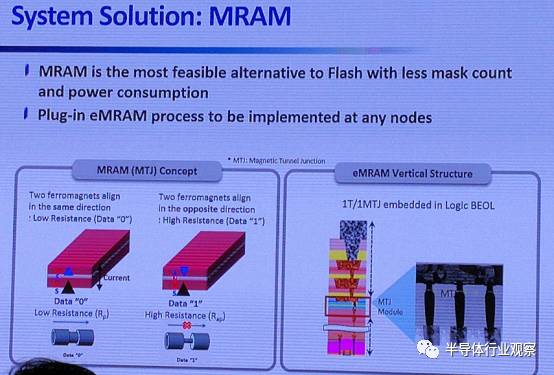

根据三星介绍,7nm之后除了在架构和材料商创新,还可以在系统上创新。其中包括了MRAM创新方案和集成封装。

先谈一下MRAM。

三星认为,MRAM是最有希望替代Flash的存储技术,因为需要更少的mask,所以其称为会变得更低,再加上功耗优势,这让mram称为他们关注的方向。

MRAM的全称是Magnetoresistance Random Access Memory,磁致电阻随机存储器。目前,MRAM的诸多研究中,已经可以开始生产的产品结构被称为STT-MRAM(Spin Transfer Torque Magnetoresistance Random Access Memory,自旋注入磁化反转磁致电阻随机存储器)。因此,本文的介绍也基于STTMRAM进行,简称为MRAM。

如果单看上文给出的名字:自旋注入磁化反转磁致电阻随机存储器,如此“高大上”的名称肯定让人眼晕。实际上,MRAM的结构并不复杂,原理也不难。它采用了类似三明治的结构。为了讲清楚它的工作原理,我们先了解一些特性:

磁电阻效应:这是指某些材料在强磁场下表现高电阻,弱磁场下表现低电阻(或者相反)。磁电阻效应在很多金属和半导体上都可看到,电阻率变化正负都有,常见的比如锑化铟、砷化铟等都是磁电阻效应比较明显的材料。

量子隧道效应:又称为势垒贯穿,是指电子在表现出波的性质的时候,有一定概率以波的方式越过势垒的效应。简单来说,就是在绝缘层极薄的情况下,它拥有一定的导电能力。

自旋注入磁化反转效应:这个效应前文提到了,也就是Spin Transfer Torque。

在了解各种效应后,理解MRAM的设计就不难了。如图3所示的MRAM三明治结构。上下两层磁体夹着中间的绝缘膜,其厚度大约几纳米,如此薄的绝缘膜使得量子隧道效应能很自如的展现出来。

除了绝缘层外,MRAM中可变磁方向的层(利用自旋注入磁化反转效应)被称为“自由层”,而固定不变的永磁体层被称为“参考层”。

当一个MRAM单元通电后,电流利用量子隧道效应,在自由层和参考层之间流动。当参考层的磁场方向和自由层相同时,磁场表现为叠加强磁场,电阻变低,电流变大;当两者方向相反时,磁场表现为互斥弱磁场,电阻变高,电流变小,相反的情况也可以。工程人员只需要测试电流的高低差值、或者电压差,就可以很自如的给出1和0两种状态定义,从而存储数据。

不仅如此,由于自由层的磁场方向改变是由于外部条件引发电子自旋方向改变,因此只要外部条件消失,电子自旋方向理论上会稳定持久的存在下去,这就意味着在完成了写入状态后,数据状态会被永久的保留。

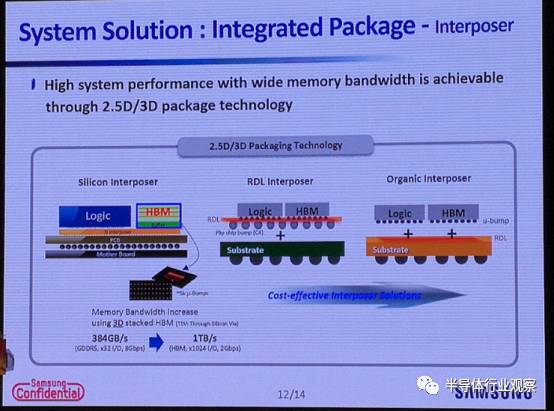

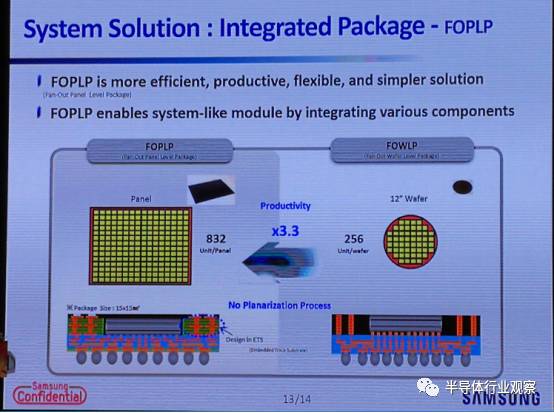

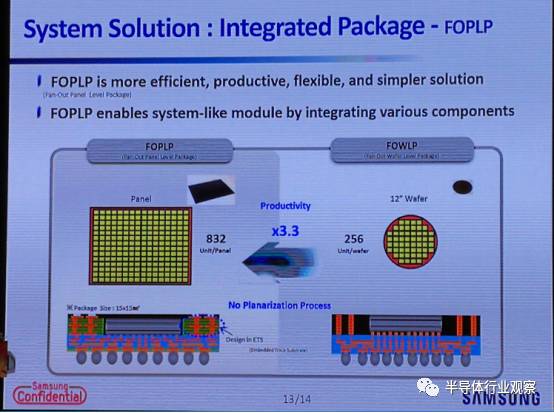

另外,集成封装也是三星看好的另一个系统解决方案。

三星认为,借助2.5D/3D的封装技术,最终做出来的芯片拥有更高的带宽,进而带来更强的系统性能。

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 jyzhang@moore.ren

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 jyzhang@moore.ren

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服