【导读】自遵循IBM的要求,将X86架构和产品授权AMD以来,英特尔和AMD就成为了处理器领域当之无愧的巨头。尤其在PC时代,这两者几无竞争对手,他们也一直引领着芯片设计。

虽然错过了手机时代,但现在的服务器和AI时代,这两家半导体“老兵”有了广大的发挥之地。为了满足终端的需求,他们也在自己的芯片设计和制造上各出奇招。例如,Chiplet正在成为他们的下一个战场。

继该领域的先驱 AMD 之后,英特尔在日前的Intel Innovation活动上也宣布推出基于 Chiplet 的产品 Meteor Lake。据介绍,Meteor Lake 的结构结合了 5 种类型的tile:当中包括了4 种类型的tile(CPU/IO/图形/SoC)以及位于所有这些tile之下的基本tile。从这颗芯片开始,我们正式见证了英特尔全面进入Chiplet时代。

延续“摩尔定律”经济成本高企,小芯片技术应运而生

英特尔公司创始人之一戈登·摩尔曾发表“摩尔定律”,指出“在成本不变时,集成电路上可以容纳的晶体管数目每经过约18个月至24个月便会增加一倍”。这一判断在很长时间内都准确预判芯片技术进展——芯片尺寸缩小、晶体管密度增加,且功耗降低。然而,随着芯片制程逐渐升级至约28nm时,提高晶体管密度的成本升高、设计复杂性增加且开发周期变长,这意味着芯片开发和制造成本开始逐渐上升。并非所有厂商都有能力负担高昂的研发费用,很长一段时间内都仅有三星和台积电两家厂商成功将10nm以下的制程技术推向市场。这意味着“摩尔定律”在经济性上出现了一定程度的失灵。

在此背景下,小芯片技术应运而生,通过将不同制程节点的多个单一功能的小芯片模块化拼搭,从而实现更优经济成本。2015年,美国美满电子科技公司(Marvell)提出模块化芯片(Modular Chip,Mochi)概念,旨在拆分SoC芯片的功能,以模块化的形式构建芯片模组,从而实现更低的设计与生产成本。随后,AMD公司以平衡性能、功耗和成本为目标推出模块化处理器芯片“霄龙”(EPYC),使其成为当时功能集成度最高的芯片。同时,AMD公司提出“性能/瓦”(performance/W)和“性能/美元”(performance/$)等芯片经济性衡量标准。

在小芯片技术出现前,厂商普遍采用SoC的方式,将多个面向不同类型计算任务的计算单元,通过光刻的形式制作到同一块晶圆上,包括中央处理器(CPU)、图形处理器(GPU)、数字信号处理器(DSP)、图像信号处理器(ISP)等众多的不同功能的计算单元,以及诸多的接口IP,其追求的是高度的集成化,利用先进制程对所有的单元进行全面的提升。这需要将多个负责不同类型计算任务的计算单元,通过光刻的形式制作到同一块芯片上,因而成本高企、开发难度极大。

而小芯片系统颠覆了上述开发流程,将一块原本复杂的SoC芯片进行解构,根据功能需求来选择不同的计算单元或功能单元,并为不同单元分配最合适的制程节点进行设计和制造。最后,通过先进封装技术将各个单元彼此互连,集成封装为一个系统级芯片组,有效降低了芯片系统的复杂度和开发成本。

相比于SoC,小芯片具有以下优点。一是可重用知识产权(IP):同一个小芯片可用于许多不同的设备。二是异构集成:小芯片可以用不同的工艺、材料和制程节点制造,针对其特定功能进行优化。三是高良率:可以在组装前测试每个小芯片,提高最终器件的良率。

中美开启Chiplet竞速

8月上旬,由英特尔、AMD、高通和英伟达等芯片巨头发起成立的全球Chiplet生态联盟UCIe,公布1.1规范版本更新,称建立Chiplet生态合规和互操作性测试要求,并首次成立汽车工作组推进Chiplet在车芯上落地。早前,AMD发布了全球首个CPU(中央处理器)与GPU(图形处理器)耦合、拥有1460亿晶体管的 AI 加速芯片Instinct MI300,利用13个Chiplet实现性能提升,超越英伟达产品,计划今年下半年量产。

与此同时,中国也在积极Chiplet技术生态布局。近日,无锡市创投、无锡锡东新城商务区管委会、清源投资、无锡芯光互连技术研究院四方共同发起成立“芯光互连产业基金”,这是国内首个重点关注Chiplet芯片设计的垂直性产业基金项目,并启动国内Chiplet开发者大赛,推进国内Chiplet技术的应用落地。

“Chiplet热潮在全世界就两个国家,一个是美国,一个是中国。”中国工程院院士许居衍8月10日表示,Chiplet技术将改变芯片设计、电子系统的“设计范式”,不仅使设计电路如同“搭积木”成为可能,而且有利于集成电路应用创新。

中国计算机互连技术联盟秘书长郝沁汾 对钛媒体App表示,Chiplet技术涉及到芯片全产业链,国内包括设计、EDA/IP、封装和制造环节的企业都在积极关注Chiplet技术进展,成熟工艺和Chiplet技术结合,在某些应用领域能够接近或替代传统7nm、5nm先进制程芯片的技术效果。

许居衍院士强调,“中国Chiplet的开放大有可为。”

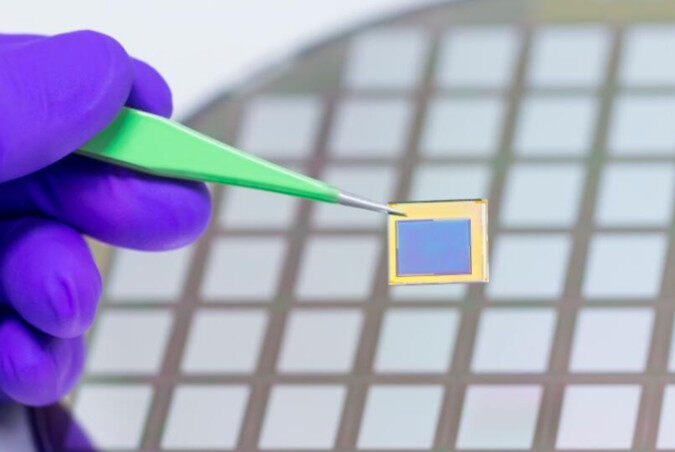

规模将超4000亿,中国同时面临机遇与挑战

Chiplet即“小芯片”或“芯粒”,是芯片制造领域近年备受热议的技术路线,通过把不同芯片的能力模块化,利用新的设计、互连接口、封装等技术,在一个封装的产品中使用来自不同技术、不同制程甚至不同工厂的芯片,从而不仅满足多元化、差异化市场需求,还能显著降低芯片开发成本。

早至上世纪70年代,业界就有与Chiplet类似的“多芯片模组”(MCM)概念,后拓展为“多芯片封装协议”(MCP)、“多元件集成电路”(MCO)等。后来,Chiplet概念由美国半导体公司Marvell创始人周秀文(Sehat Sutardja)于2015年提出的模块化芯片架构演化而来,AMD率先将其应用于服务器芯片设计。

实际上,从16nm/14nm节点开始,芯片设计和制造成本飙升,一个完全规模化工艺点的更新周期从18个月延长到30个月甚至更长,半导体工艺技术发展带来的功耗、性能和面积(PPA)收益下降。如今最先进的芯片有数十亿个晶体管,但芯片的扩展变得越来越困难,而且扩展所带来的价格、性能和功率优势的缩减速度都快于晶体管,尤其超过3nm之后,FinFET(鳍式场效晶体管)技术将失去动力。

同时在价格方面,芯片成本随着制程工艺升级不断增加。以先进工艺节点处于主流应用时期的设计成本为例,工艺节点为28nm时,单颗芯片设计平均成本约为4000万美元,7nm芯片的设计成本为2.17亿美元,5nm芯片的设计成本为4.16亿美元,3nm的设计将耗资5.9亿美元。

因此,考虑到整个芯片制造成本与功效等因素,将一个较大的芯片分解成多个更小的芯片,并根据需要进行混合和匹配的成本更低,产量更高的Chiplet应运而生。

据研究机构Omdia的数据预计,到2024年,Chiplet的市场规模将达到58亿美元,是2018年6.45亿美元规模的9倍;到2035年,市场规模将进一步扩大到570亿美元(约合人民币4151.08亿元)以上,是2018年规模的88倍。预计Chiplet技术将迎来广阔的发展空间。

据钛媒体App的统计,目前国内从事Chiplet相关研发的企业和机构主要包括四类:

一是做计算芯片设计的企业,例如寒武纪、壁仞科技、瑞芯微电子(Rockchip)等;

二是以芯原股份、芯耀辉、芯和半导体等 EDA/IP(知识产权)企业;

三是一批新兴的专为企业提供Chiplet设计方案的封装设计服务公司,例如奇异摩尔等;

四是后端封测制造企业,例如长电科技、华天科技、通富微电、甬矽电子等公司。

而且,Chiplet标准方面也备受关注,国内主要包括中科院计算所,工信部电子标准院,以及华为、中兴等多家中国企业和科研院所。

国外则主要是UCIe联盟,发起成员包括AMD、Arm、日月光(ASE)、谷歌云、英特尔、英伟达、Meta、微软、高通、三星、台积电以及阿里巴巴;贡献者成员包括IBM、应用材料、LG、安靠、博世、SK海力士、西门子、长电科技、通富微电、合见工软等;采用成员包括力积电、芯来科技等。此外,欧洲微电子研发中心(IMEC)也在开展Chiplet相关研究。

郝沁汾向钛媒体App透露,截至目前,中科院计算所发起的Chiplet组织中国计算机互连技术联盟(CCITA)成员企业已达100家。

当前,海外企业在Chiplet方向上有多个落地产品、进步速度较为激进。例如台积电,其正在开发一种名为“集成芯片上系统”(SoIC)的技术,这种技术可以为客户提供使用芯片的3D设计;而AMD在Chiplet技术上深耕已久,目前7nm CPU和GPU产品均使用了Chiplet设计并封装,未来AMD还将通过转接板和更密集的互连减少连线开销,直接在计算芯片上堆叠存储芯片,以及3D堆叠技术实现芯片封装等。

国内方面,今年1月,晶圆封装龙头长电科技宣布,公司XDFOI Chiplet高密度多维异构集成系列工艺已按计划进入稳定量产阶段,同步实现4nm节点多芯片系统集成封装产品出货;龙芯中科采用Chiplet技术,研发出一款面向服务器市场的32核CPU处理器龙芯3D5000,已经于今年上半年提供测试样片;而寒武纪第四代Al处理器MLUarch03、壁仞科技通用GPU BR100等量产芯片也都采用了Chiplet技术。

产业链队伍逐渐壮大

近年里,华为、苹果、英特尔等巨头均已自研Chiplet技术并推出相关产品。国内供应链也有序发展,今年3月份,中国Chiplet产业联盟联合国内系统、IP、封装厂商一起,共同发布了《芯粒互联接口标准》 ACC1.0,该标准为高速串口标准,着重基于国内封装及基板供应链进行优化,以成本可控及商业合理性为核心导向。据了解,目前行业正逐步构建一个开放的Chiplet生态系统。

“Chiplet技术在数据中心、高性能计算、AI和5G等领域有着广泛的应用前景。目前,相关技术已经越来越成熟,主要表现在Chiplet模块间的互连技术和制程协调管理相关技术在不断发展和进步;UCIe标准推动Chiplet技术的广泛应用;许多公司正在Chiplet上投入大量的研发资源;业内对Chiplet技术是半导体行业的一个重要趋势已形成共识。”钧山资管董事总经理王浩宇对《证券日报》记者表示。

在应用方面,Chiplet技术也在逐步从理论阶段走向实践阶段。不过,王浩宇认为,推动Chiplet技术真正广泛应用和切实落地,还需行业在几个方面进一步突破。“在互连技术上仍需突破,同时如何有效地协调和管理不同的制程,也是一个挑战;有一套标准的Chiplet接口和协议,是推动Chiplet技术落地的关键;形成有效的供应链和生态系统对于Chiplet技术的落地至关重要;Chiplet技术需持续降低成本、提高效率,如此厂商才会愿意大规模地研发和使用这种技术。”

在北京社科院研究员王鹏看来,以Chiplet为代表的技术发展将在打通行业堵点、坚实算力底座方面起到重要作用,目前Chiplet生态的发展还有很长的路,架构设计和先进封装需要齐头并进,产业链企业应形成分工,以生态协作方式共同加速Chiplet的落地。

来源:贤集网

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服