日前,Rambus宣布推出6400 MT/s DDR5寄存时钟驱动器(RCD),并向各大DDR5 RDIMM内存模块制造商提供样品。相比第一代 4800 MT/s解决方案,Rambus 第三代6400 MT/s DDR5 RCD的数据传输速率和带宽提高了33%。相对而言,目前其他几家主流的DDR5 RCD厂商还停留在第二代DDR5上。

而与此同时,IT基础设施的不断增长,使得提高内存传输速率的需求不断提升。正如Rambus内存互连芯片业务部门产品营销副总裁 John Eble所说,在三到四个月之前,一些全新发布的服务器CPU进一步提高了其数据传输速率,因此第三代6400 MT/s速率的DDR5势在必行。

IDC内存半导体部门副总裁Soo-Kyoum Kim也表示:“DDR5大幅提升了计算系统的性能。随着数据中心应用更加频繁地要求越来越高的内存带宽,DDR5生态系统将成为提升下一代数据中心性能提升这一基本需求的关键。”

DDR5的重大改变

DDR至今已经演进至第五代,每一代都有着很多升级。

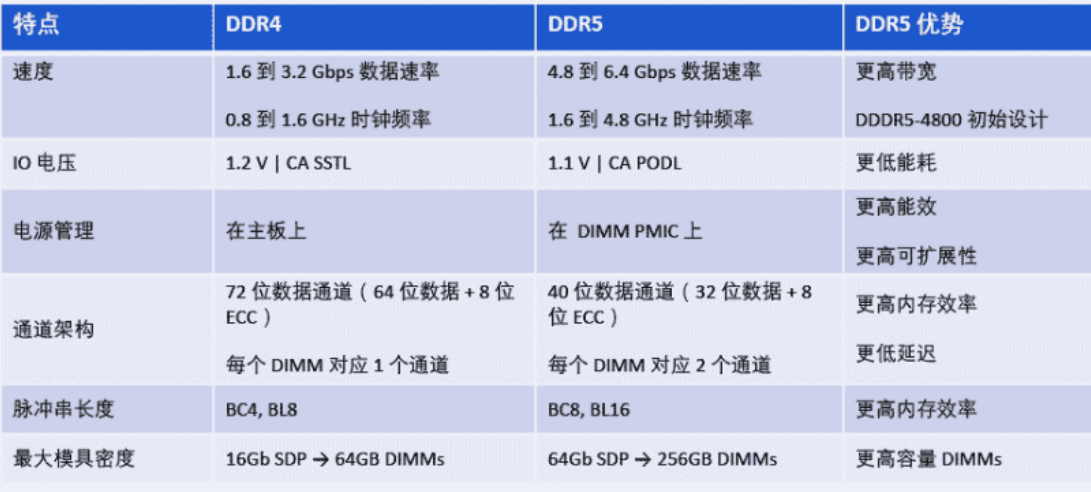

如图所示,这是RAMBUS公司列举的DDR4与DDR5的不同,包括速度、IO电压、电源管理、通道架构、脉冲串长度以及最大模具密度等。

DDR5 的这些变化引入了许多设计需求,涉及更高的速度和更低的电压,这提出了新一轮的信号完整性挑战。设计师将需要确保主板和 DIMM 能够处理更高的信号速度。在执行系统级仿真时,需要检查所有 DRAM 位置的信号完整性。

DDR4 在信号完整性方面所面临的主要设计挑战在于双数据速率 DQ 总线,而对低速命令地址 (CA) 总线的关注较少。而在 DDR5 的设计中,即使是 CA 总线也会要求特别注意信号完整性。对于 DDR4,曾考虑过用差分反馈均衡 (DFE) 来改善 DQ 数据通道。而对于 DDR5,连RCD 的 CA 总线接收器也需要DFE 选项,以确保良好地接收信号。

另一个考量是主板上的供电网络 (PDN),包括带 PMIC 的 DIMM。考虑到更高的时钟和数据速率,需要确保 PDN 能够处理好高速且信号完整性良好的运行负载,并为 DIMM 提供干净良好的电源。

连接主板和 DIMM 的 DIMM 连接器也必须处理好新的时钟和数据速率。对于系统设计师而言,由于印刷电路板 (PCB) 周围的时钟速度和数据速率更高,系统设计时必须更加重视电磁干扰和电磁兼容(EMI 和 EMC)。

从DDR5 DIMM工作原理看RCD的重要性

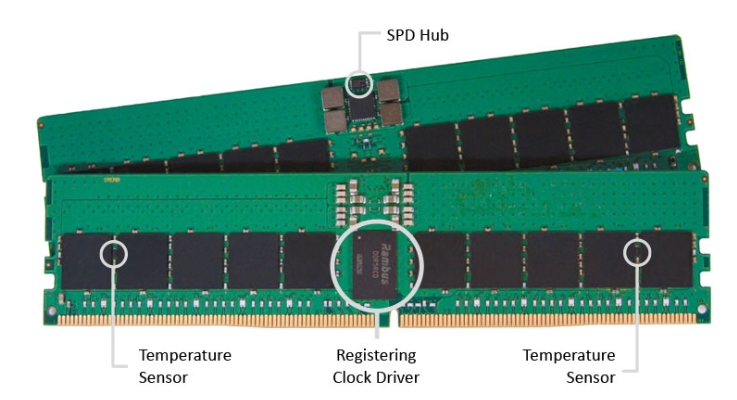

DDR5的DIMM除内存颗粒外,通常还需要包括寄存时钟驱动器 (RCD)、串行存在检测集线器 (SPD Hub) 和温度传感器 (Temperature Sensor),用来实现RDIMM和NVDIMM的管理与控制,并且利用SPD集线器还可以支持PC客户端的UDIMM或SODIMM等方案。另外还有一种是LRDIMM,需要额外的DATA Buffer芯片。

在这其中,RCD 是关键的控制芯片,它将命令/地址信号和时钟分配给 DIMM 上的 DRAM颗粒。

SPD集线器支持通过 I3C 总线进行系统配置和热管理的重要数据通信,并且有一个集成的温度传感器。

每个DIMM上有两个温度传感器提供精确的热感测,并与 SPD 集线器结合,为内存模块提供三个热遥测点。

如图所示,典型的UDIMM需要一系列芯片组,RAMBUS可以给客户完整的解决方案。

坚持长期投资换来的回报

Rambus公司成立将近30年,一直专注于内存接口领域的研发。从2016年起就推动DDR5的迭代和发展,并在市场上首个推出了第一代DDR5 RCD、第二代RCD以及如今的第三代RCD,以及其他包括集线器和温度传感器的整体方案,满足客户不同要求。

John 预计使用DDR5 RCD第三代的系统将在2024年开始出货,并在2025年实现量产。