引言

为减少汽车碰撞事故的发生,汽车碰撞技术在近年发展很快。汽车避撞技术首先需要解决的问题是汽车之间的安全距离,当汽车与汽车之间的距离小于安全距离时,就应该能够自动报警。本文给出了高速防撞器的核心部分:车距报警器的设计方法。设计了一款安装于车前/车尾的便携式系统,能在汽车停车、倒车以及行使过程中自动监控汽车与其它汽车、人和障碍物之间的距离,如果距离小于规定的安全距离(一般为两米左右)则报警,防止恶**故的发生。

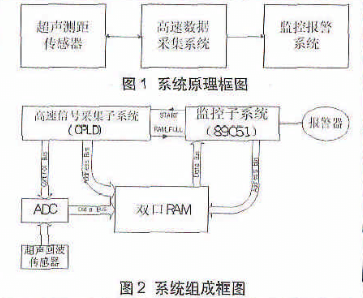

其原理是不断监控利用超声波距离传感器得到的距离信息,遇到“危险信号”(距离过小)则报警。但是,由于汽车在行使过程中一般速度较高,同时某些用途的汽车的驾驶环境决定了其交通环境具有突发性、意外性的特点。因此,距离报警器必须具有实时、准确的特点,这对该系统的实时性要求非常高。系统原理框图如图1所示。

系统功能

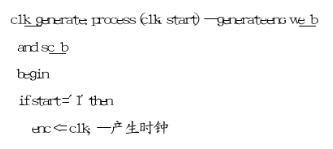

系统的功能框图主要有两个子系统组成:信号采集子系统和监控子系统,如图2所示。其中,信号采集子系统用于实现高速距离信号的采集,核心器件包括一片CPLD和一个和超声测距传感器相连的ADC。而监控子系统由51单片机最小系统组成,主要负责信号的预处理、判断和驱动报警器。两个子系统之间的通讯,由一片双口RAM来完成。

两个子系统的具体功能实现如下:

高速信号采集子系统

·CPLD接到MCU(89C51)的工作触发信号(START,高电平有效)之后,开始控制和超声距离传感器的ADC,进行实时数据采集;

·与ADC控制信号同步提供RAM地址计数器(A0~A16)和写信号(/WE),使得每次ADC的结果直接存入双口RAM并且自动增加地址;

·当地址计数器达到最大的时候,发出中断脉冲信号(RAM_FULL,上升沿有效),提示监控子系统RAM已满,可以进行下一步处理;

C51监控子系统

·启动后,发出工作触发信号(START)给CPLD子系统,通知信号采集子系统开始工作,然后进入等待循环;

·接到RAM_FULL中断(INT1)脉冲之后,知道RAM已经写满一帧。读取双口RAM中的数据,提取距离信息,判断是“危险”还是“安全”;

·如果距离处于“安全”则退出中断服务程序返回;如果为“危险”则拉低SRART信号,让CPLD和ADC停止工作,并立刻驱动报警器报警,直至控制人员(司机)做出相应反映后手工复位。

系统软、硬件设计

ADC选择

由于系统频率为20MHz,根据Nyquist定律,采样频率应该在40MHz以上,为了提高精度,本系统选用了AD公司的AD9283芯片,该芯片工作电压为3.3V,最高工作频率为100MHz,8Bit并口输出。工作时,只需要CPLD控制器产生采样时钟输入(上升沿有效)就可以完成一次AD采样。

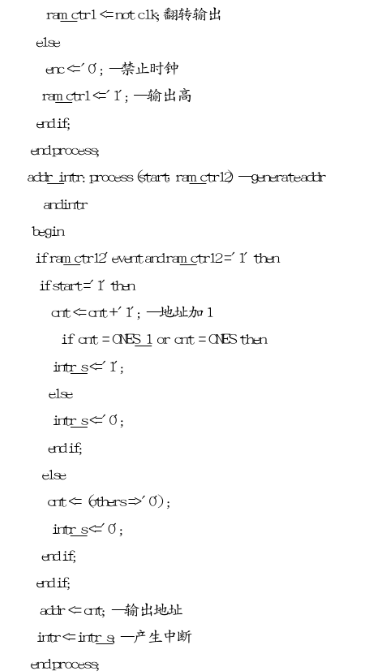

CPLD控制器

本系统的核心器件是CPLD控制器。在以往的数据采集系统中,ADC-RAM模块往往采用MCU作为CPU来控制,因此,采集频率直接受到MCU速度的制约,并且当速度要求较高时,和RAM存储器的同步也成为问题。基于这个考虑,系统采用Altera公司的EPM7064 CPLD芯片来同时控制ADC和RAM,从而很好地解决了时序精度和同步的问题。CPLD的功能逻辑,用VHDL语言实现,首先定义了七个实际需要用到的端口:

start 开始采样,单片机提供,告知CPLD子系统开始工作;

clk CPLD的时钟,本系统采用epm7064的全局时钟引脚;

enc ADC时钟,上升沿有效;

we_ram_b 为RAM提供WE信号,低有效;

cs_ram_b 为RAM提供CS信号,低有效;

addr 为RAM提供地址信号,累加直至加满产生中断;

intr RAM写满中断输出,输出一个上升沿;

对应于前面描述的两个逻辑,我们用VHDL语言编写了两段过程。

系统仿真采用MAXPLUXII 10.1,经测试完全符合本系统的要求。

89C51单片机监控子系统部分为典型的51最小系统。其中,P0、P2被用于地址、数据复用口,INT1接受RAM_FULL的中断输入,P1口被用于控制,发送START信号等。

数据缓存及通讯

本系统包括两个子系统,因此,两个子系统之间必须通过缓冲器来进行通讯。一般而言,多处理器间通讯方法有三种:(1) 双口RAM; (2) 高速FIF0; (3)总线开关加存储器。双端口 RAM作为一种特殊的RAM芯片,在高速数据采集处理系统中得到广泛的应用。它具有两个独立的端口,各自均有一套独立的数据总线、地址总线和控制总线,允许两个端口独立地对存储器中的任何单元进行存取操作。当两个端口同时对存储器中的同一单元进行存取操作时,可由其内部仲裁逻辑决定优先权。即当两组地址总线完全相同时,片内总线仲裁逻辑向后访问的一方发出等待信号,使该方进入等待,待另一方访问结束之后等待撤消,等待方继续访问这一地址。双口RAM的特殊结构使得双机可以方便快速地进行数据交换,大大提高了主机与DSP运动控制卡的并行处理能力,而且解决了DMA方式存在的问题。我们选用Integrated Device Technology公司的IDT7132/IDT7142单片双口 RAM,它是2K*8Bit的双口高速静态RAM,存取速度为20ns,CPLD系统和89C51可以同时访问。

超声传感器和报警器

系统输入部分采用奥特仪表制造公司的P42-M超声传感器,而报警器为新华电子公司的XH04电磁式蜂鸣器。

整机调试

由于要采集的超声信号属于高频信号,因此,PCB电路板的电磁兼容性问题显得非常重要,本系统PCB板由专业厂商设计,充分考虑到了抗干扰的因素。经过测试,高频信号在系统中没有产生影响系统整体性能的干扰。

我们用数字信号发生器产生不同频率的方波、三角波信号作为仿真信号直接输入到ADC模拟输入端进行测试,并在试验中逐渐改变C51软件中的报警阈值。测试结果表明,该系统很好地达到了预想的功能要求,并且有良好的实时性和鲁棒性。