stc89c52引脚图及引脚功能说明

本文为您带来单片机STC89C52引脚图,及STC89C52各个具体的引脚功能说明,详情请看如下全文内容。

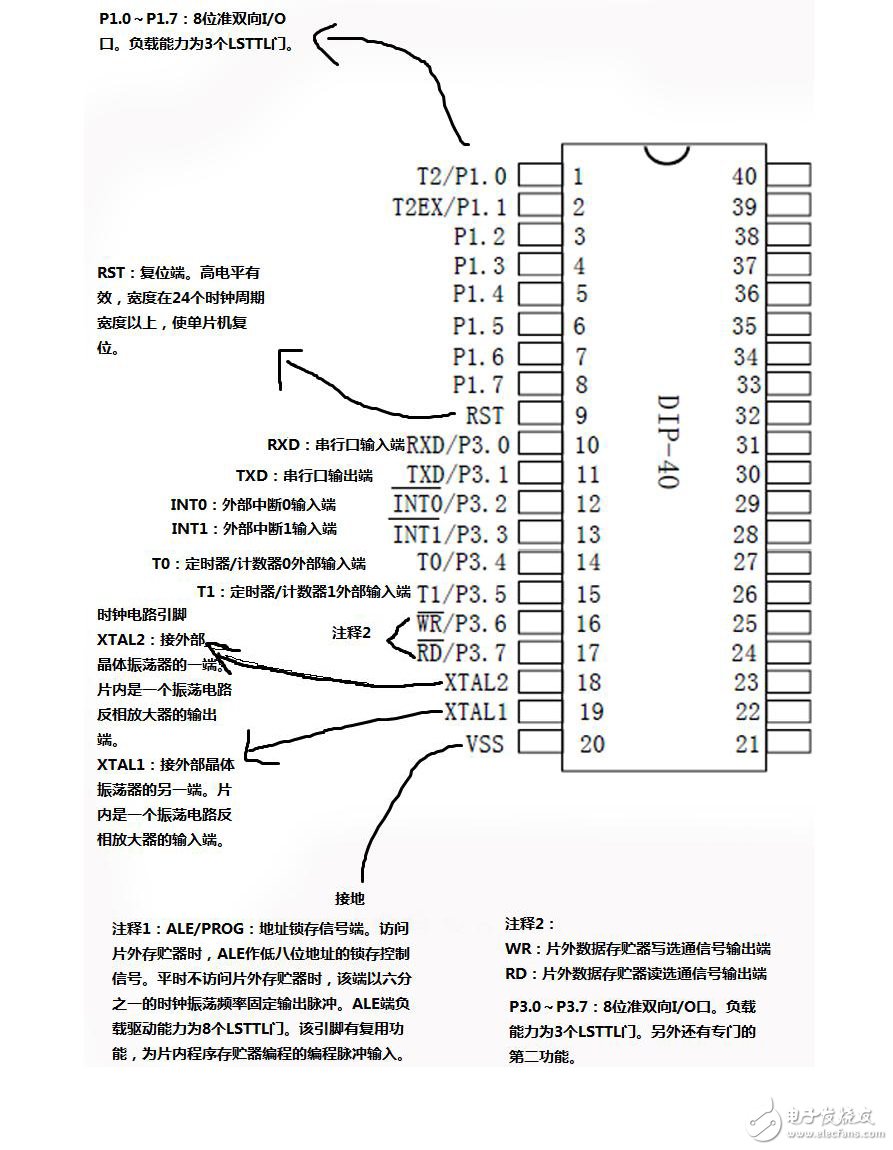

单片机STC89C52引脚图,如下图所示:

STC89C52功能简述:

STC89C52引脚说明:

VCC(40引脚):电源电压

VSS(20引脚):接地

P0口:P0口是一个8位漏极开路的双向I/O口。作为输出口,每位能驱动8个TTL逻辑电平。对P0端口写“1”时,引脚用作高阻抗输入。当访问外部程序和数据存储器时,P0口也被作为低8位地址/数据复用。在这种模式下,P0具有内部上拉电阻。在flash编程时,P0口也用来接收指令字节;在程序校验时,输出指令字节。程序校验时,需要外部上拉电阻。

P1口:P1口是一个具有内部上拉电阻的8 位双向I/O 口,p1 输出缓冲器能驱动4个TTL逻辑电平。对P1 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。

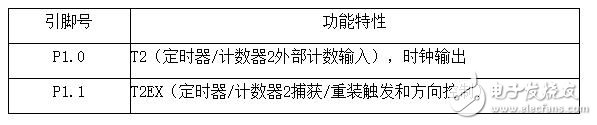

此外,P1.0和P1.2分别作定时器/计数器2的外部计数输入(P1.0/T2)和时器/计数器2 的触发输入(P1.1/T2EX),具体如下表所示。在flash编程和校验时,P1口接收低8位地址字节。

表1 P1.0和P1.1引脚复用功能

引脚号第二功能

P1.0 T2(定时器/计数器T2的外部计数输入),时钟输出

P1.1 T2EX(定时器/计数器T2的捕捉/重载触发信号和方向控制)

P1.5 MOSI(在线系统编程用)

P1.6 MISO(在线系统编程用)

P1.7 SCK(在线系统编程用)

P2口:P2口是一个具有内部上拉电阻的8位双向I/O 口,P2输出缓冲器能驱动4个TTL逻辑电平。对P2端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。

在访问外部程序存储器或用16位地址读取外部数据存储器(例如执行MOVX @DPTR)时,P2口送出高八位地址。在这种应用中,P2口使用很强的内部上拉发送1。在使用8位地址(如MOVX @RI)访问外部数据存储器时,P2口输出P2锁存器的内容。在flash编程和校验时,P2口也接收高8位地址字节和一些控制信号。

P3口:P3口是一个具有内部上拉电阻的8位双向I/O 口,P3输出缓冲器能驱动4个TTL逻辑电平。对P3端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。P3口亦作为STC89C52特殊功能(第二功能)使用,如下表所示。在flash编程和校验时,P3口也接收一些控制信号。

P3口除作为一般I/O口外,还有其他一些复用功能:

表2 P3口引脚复用功能

RST——复位输入。当振荡器工作时,RST引脚出现两个机器周期以上高电平将是单片机复位。

ALE/PROG——当访问外部程序存储器或数据存储器时,ALE(地址锁存允许)输出脉冲用于锁存地址的低8位字节。一般情况下,ALE仍以时钟振荡频率的1/6输出固定的脉冲信号,因此它可对外输出时钟或用于定时目的。要注意的是:每当访问外部数据存储器时将跳过一个ALE脉冲。

对FLASH存储器编程期间,该引脚还用于输入编程脉冲(PROG)。

如有必要,可通过对特殊功能寄存器(SFR)区中的8EH单元的D0位置位,可禁止ALE操作。该位置位后,只有一条MOVX和MOVC指令才能将ALE激活。此外,该引脚会被微弱拉高,单片机执行外部程序时,应设置ALE禁止位无效。

PSEN——程序储存允许(PSEN)输出是外部程序存储器的读选通信号,当STC89C52由外部程序存储器取指令(或数据)时,每个机器周期两次PSEN有效,即输出两个脉冲,在此期间,当访问外部数据存储器,将跳过两次PSEN信号。

EA/VPP——外部访问允许,欲使CPU仅访问外部程序存储器(地址为0000H-FFFFH),EA端必须保持低电平(接地)。需注意的是:如果加密位LB1被编程,复位时内部会锁存EA端状态。如EA端为高电平(接Vcc端),CPU则执行内部程序存储器的指令。FLASH存储器编程时,该引脚加上+12V的编程允许电源Vpp,当然这必须是该器件是使用12V编程电压Vpp。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。