S3C2410 LCD控制器的外部管脚图和内部方框图

S3C2410管脚

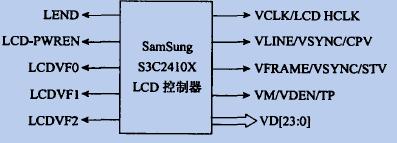

S3C2410 LCD控制器用于传输视频数据和产生必要的控制信号,像VFRAME、VLINE、VCLK、VM等等。除了控制信号,S3C2410还有输出视频数据的端口VD[23 z O],如图1示。将要用到的管脚描述如下:VCLK—— 像素时钟信号;VD[23:O]——LCD像素输出端口;VM/VDEN/TP— —LCD驱动器的AC偏置信号(STN)/数据使能信号(TFT)/SEC TFT源驱动器数据加载脉冲信号。

图1 S3C2410 LCD控制器的外部管脚图

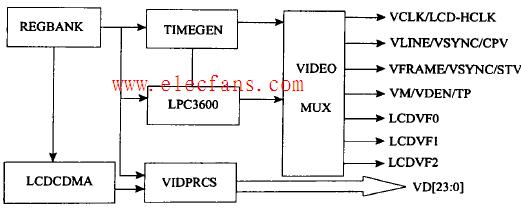

LCD控制器由REGBANK、LCDCDMA、VIDPRCS、TIMEGEN 和LPC3600组成(见图2)。

REGBANK有17个可编程寄存器组和256×16的调色板存储器,用来设定LCD控制器。LCDCDMA是一个专用DMA,自动从帧存储器传输视频数据到LCD控制器,用这个特殊的DMA,视频数据可不经过CPU 干涉就显示在屏幕上。VIDPRCS接受从LCDCDMA 来的视频数据并在将其改变到合适数据格式后经VDF23:O]将之送到LCD驱动器,如4/8单扫描或4双扫描显示模式。TIMEGEN由可编程逻辑组成,以支持不同LCD驱动器的接口时序和速率的不同要求。TIMEGEN产生VFRAME、VLINE、VCLK、VM信号等。

数据流描述如下:FIFO存储器位于LCDCDMA。当FIFO空或部分空时,LCDCDMA要求从基于突发传输模式的帧存储器中取来数据,存人要显示的图像数据,而这个帧存储器是LCD控制器在RAM 中开辟的一片缓冲区。当这个传输请求被存储控制器中的总线仲裁器接收到后,从系统存储器到内部FIFO就会成功传输4个字。FIFO的总大小是28个字,其中低位FIFOL是12个字,高位FIFOH 是16个字。S3C241O有两个FIFO来支持双扫描显示模式。在单扫描模式下,只使用一个FIFO(FIFOH)。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。