相信大家对产品并不陌生,因为它在我们的电路中随处可见,小到晶振,通常我们的MCU需要一个25MHz(或者其他频率的)的Oscillator;或者是一个采集系统,里面的可能相对复杂,可能有ADC的采样,FPGA的数字时钟等,如何让ADC前端的数据不失真的被FPGA获取,时钟信号非常关键。

本文引用地址:在给大家带来时钟新产品之前,我给大家介绍两个关键参数,因为在绝大多数的Timing/Clock产品中都会提到这两个参数,这两个参数分别是Jitter(时钟抖动)和 Phase Noise(相位噪声)。

Jitter(时钟抖动)

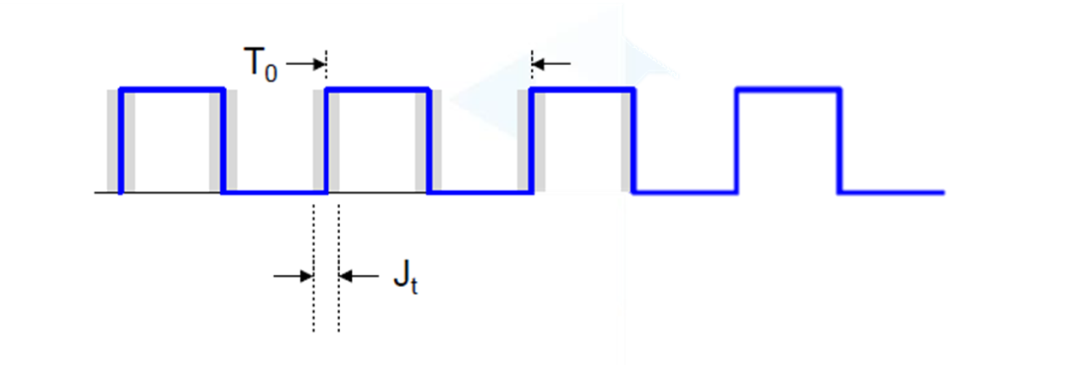

时钟抖动是一个时域的概念,是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动.可以用抖动频率和抖动幅度对时钟抖动进行定量描述。通常希望一个周期性波形(特别是时钟)跨过特定门限的时间非常精确,与该理想值的偏差称为抖动。时钟抖动可以分为随机抖动(Random Jitter,简称rj)和固有抖动(Deterministic Jitter),随机抖动的来源为热噪声、shot noise和flick noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动;固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。简单来说,在频域里面随机抖动表现为噪声,固有抖动可以近似看成是谐波,毛刺。

图1 Jitter的时域表现

Phase Noise(相位噪声)

相位噪声是频域的概念,它通常与频率相关,是指系统(如各种射频器件)在各种噪声的作用下引起的系统输出信号相位的随机变化。描述无线电波的三要素是幅度、频率、相位。频率和相位相互影响。理想情况下,固定频率的无线信号波动周期是固定的,正如飞机的正常航班一样,起飞时间是固定的。频域内的一个脉冲信号(频谱宽度接近0)在时域内是一定频率的正弦波。

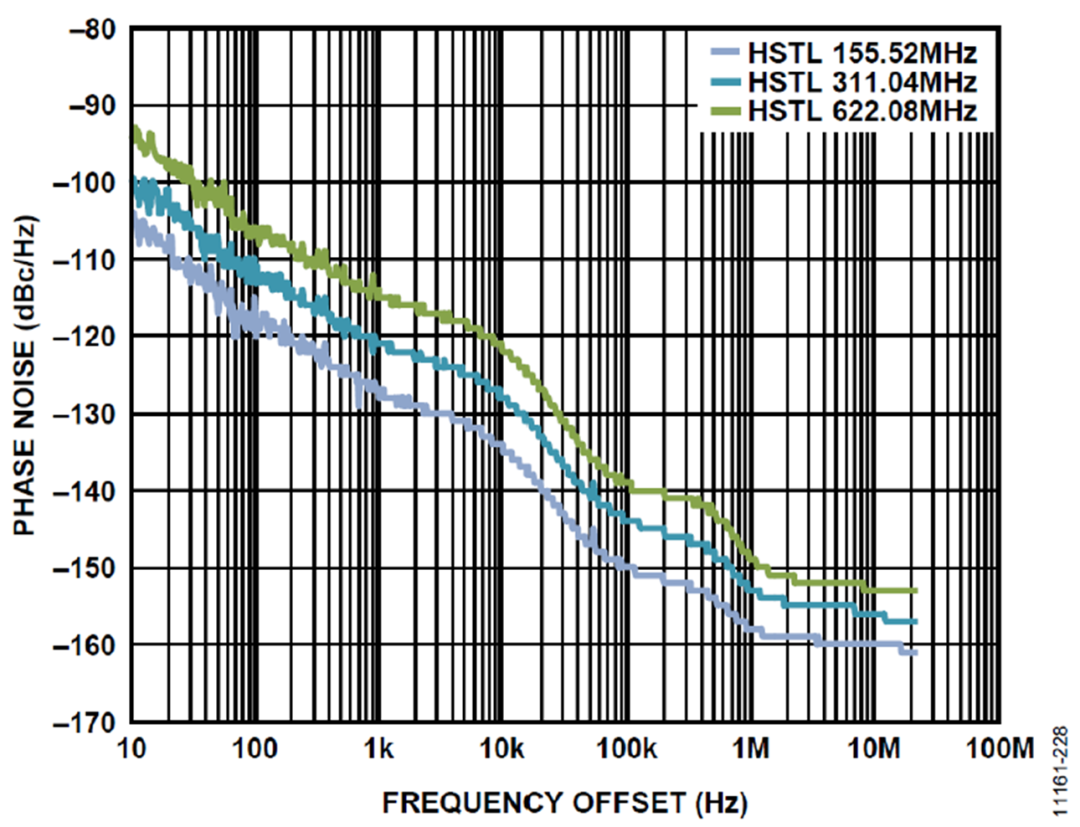

图2 Typical Phase Noise Figure

怎么去理解这个图呢?横轴是频率偏移,纵轴是相位噪声,单位是dBc/Hz,咱们看绿色这条线是在622.08MHz测试的,通常规格书里面会标出-138dBc/Hz@100KHz,622.08MHz,意思是这个时钟在622.08MHz,针对这个中心频点,偏移100KHz的频谱噪声相对于载波的能量比,这个值越小,代表噪声越小,时钟抖动越小。

另外一方面,对于同一器件,频率越高,相噪越差;频率提高一倍,相噪恶劣6dB。

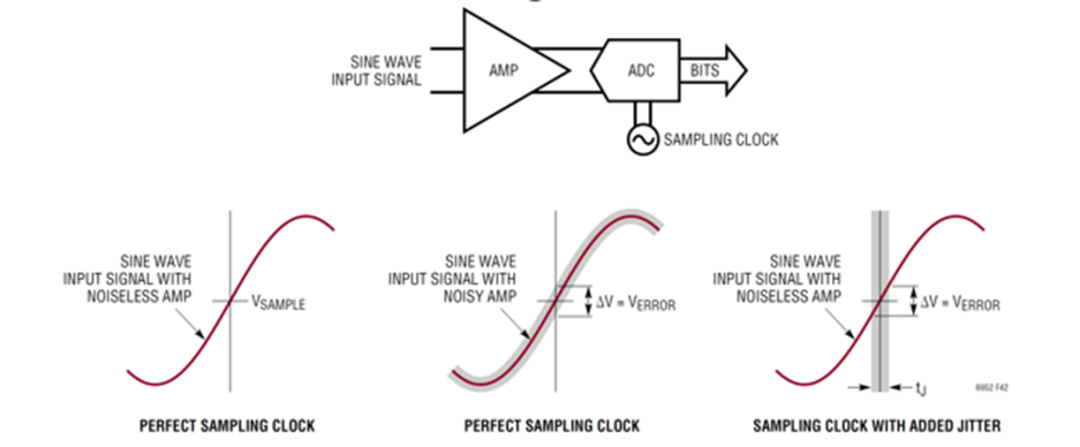

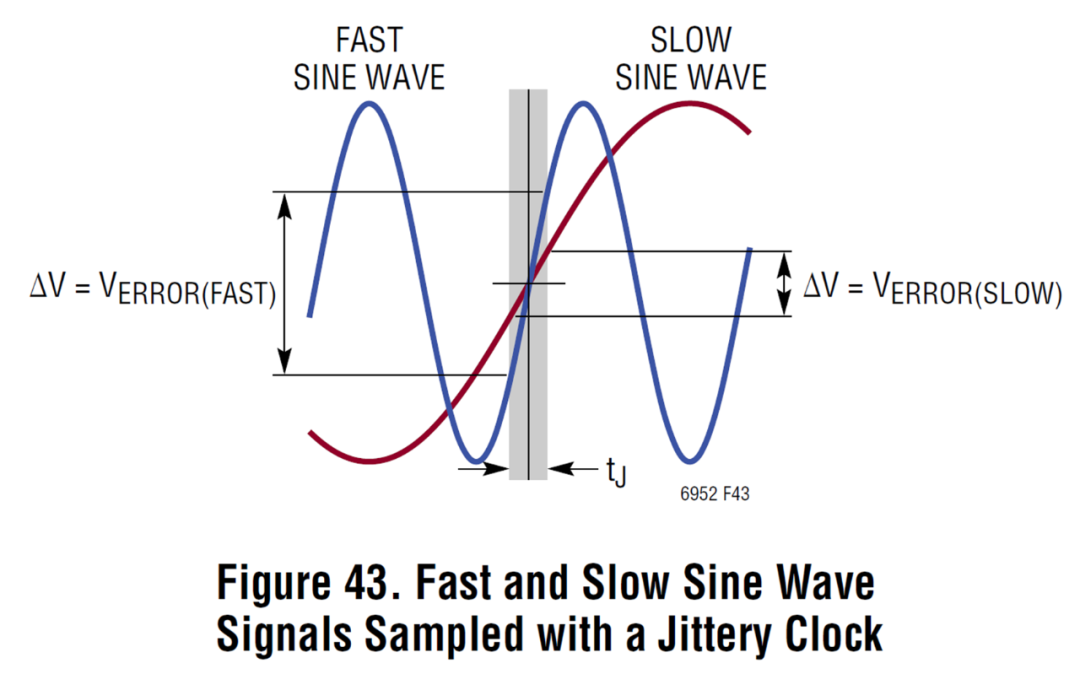

图3 Jitter对采样系统的影响

双环路时钟发生器可清除抖动并提供多个高频输出

随着数据转换器的速度和分辨率不断提升,对具有更低相位噪声的更高频率采样时钟源的需求也在不断增长。时钟输入面临的积分相位噪声(抖动)是设计师在设计蜂窝基站、军用雷达系统和要求高速和高性能时钟信号的其他设计时面临的众多性能瓶颈之一。普通系统有多个低频噪声信号,PLL 可将其上变频至更高频率,以便为这些器件提供时钟。单个高频 PLL 可以解决频率转换问题,但很难设计出环路带宽足够低,从而能够滤除高噪声参考影响的PLL。搭载低频高性能VCXO 和低环路带宽的 PLL可以清除高噪声参考,但无法提供高频输出。高速和噪声过滤可以通过结合两个 PLL 同时实现:先是一个低频窄环路带宽器件(用于清除抖动),其后是一个环路带宽较宽的高频器件用于扇出高频和提升远端相位噪声。

双环路时钟发生器产品及应用

实用案例1:

AD9528 — JESD204B/JESD204C Clock Generator with 14 LVDS/HSTL Outputs

Application: 5G small cell — RU timing for transceiver and FPGA

Features:

1. 可支持14路LVDS/HSTL输出,最高输出频率可到1.25G

2. 双环路时钟发生器架构,PLL1作为输入时钟clean up,支持110MHz的鉴相频率,外部VCXO输入;PLL2作为第二级锁相环,支持275MHz的鉴相频率,内部集成VCO

3. 时钟抖动小于160fs@122.88 MHz,12 kHz to 20 MHz integration range

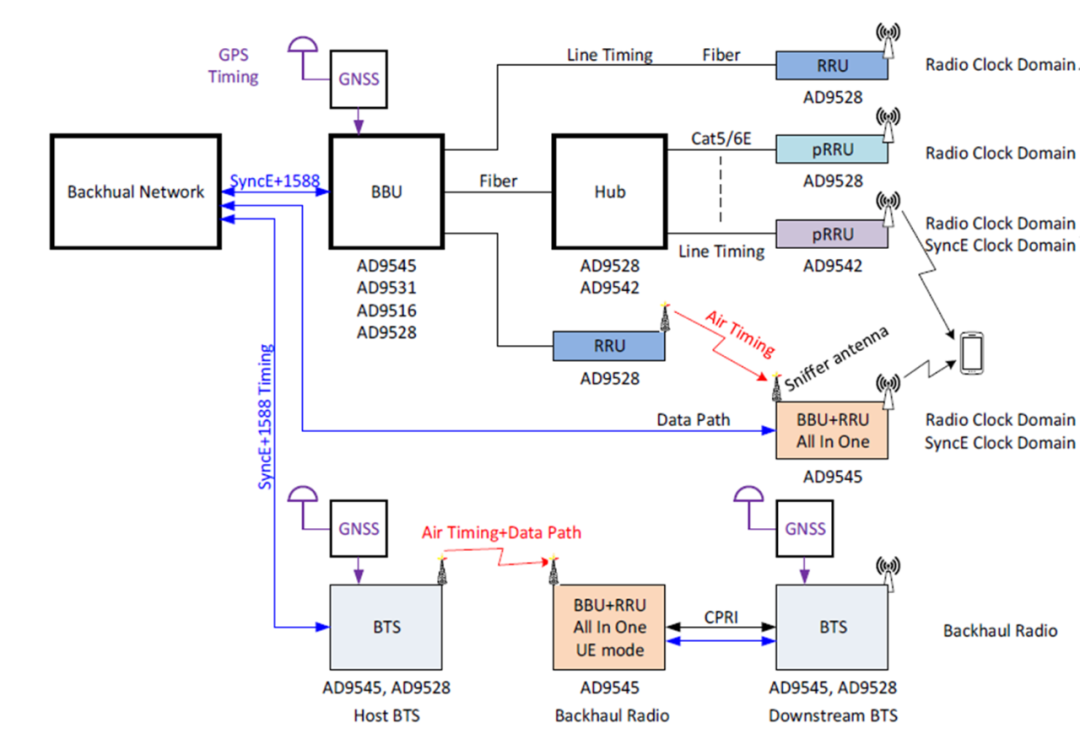

图4 AD9528/AD9545时钟在Small Cell的应用

实用案例2:

HMC7044 — High Performance, 3.2 GHz, 14-Output Jitter Attenuator with JESD204B

Application: High speed data converter clocking

Features:

1. 可支持14路LVDS, LVPECL, orCML输出,最高输出频率可到3.2GHz

2. 双环路时钟发生器架构,PLL1作为输入时钟clean up,支持800MHz的输入参考频率,外部VCXO输入;PLL2作为第二级锁相环,支持250MHz的鉴相频率,内部集成VCO,频率调节范围为2.4-3.2GHz

3. 时钟抖动小于44fs@2457.6 MHz, 12 kHz to 20 MHz integration range

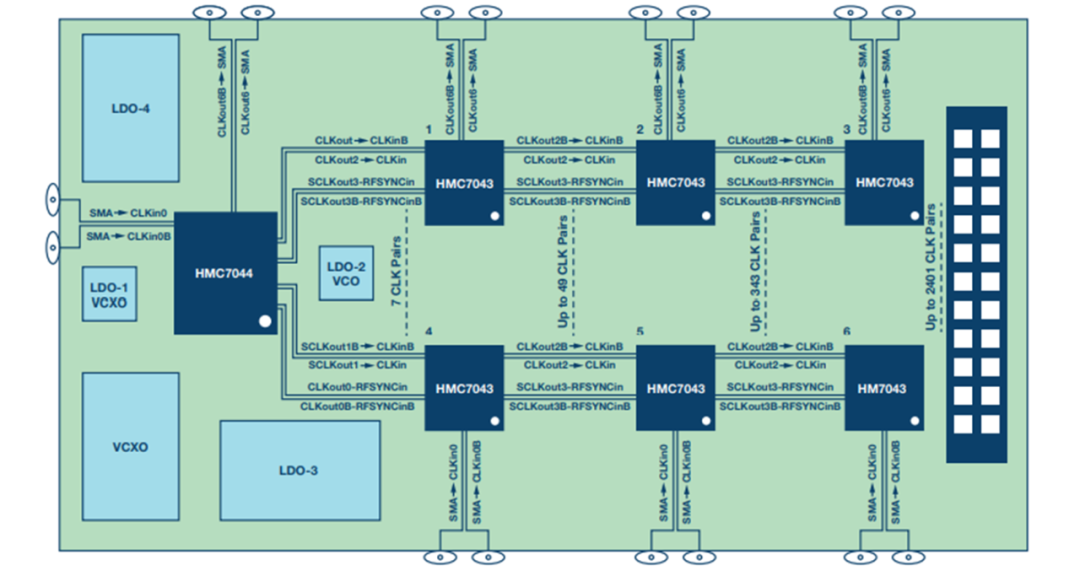

4. 超低抖动非常适合高速采集系统,在采样率低于3.2G,多通道数据采集非常有优势,可以通过多片级联HMC7044+HMC7043的方式实现多天线MIMO系统的时钟同步

图5 HMC7044/HMC7043在多通道数据转化阵列的应用

最新宽带时钟产品ADF4377及应用

ADF4377 — Microwave Wideband Synthesizer with Integrated VCO

● Application: High speed data converter clocking above 3GHz samplerate, MxFE sample clock

● Preferred companion chip to the AD9081/2, AD9177, AD9207/9, AD9986/AD9988, and data converters such as the AD9213ADC, or the AD9689, AD9208, AD917xDAC and AD916x

Features:

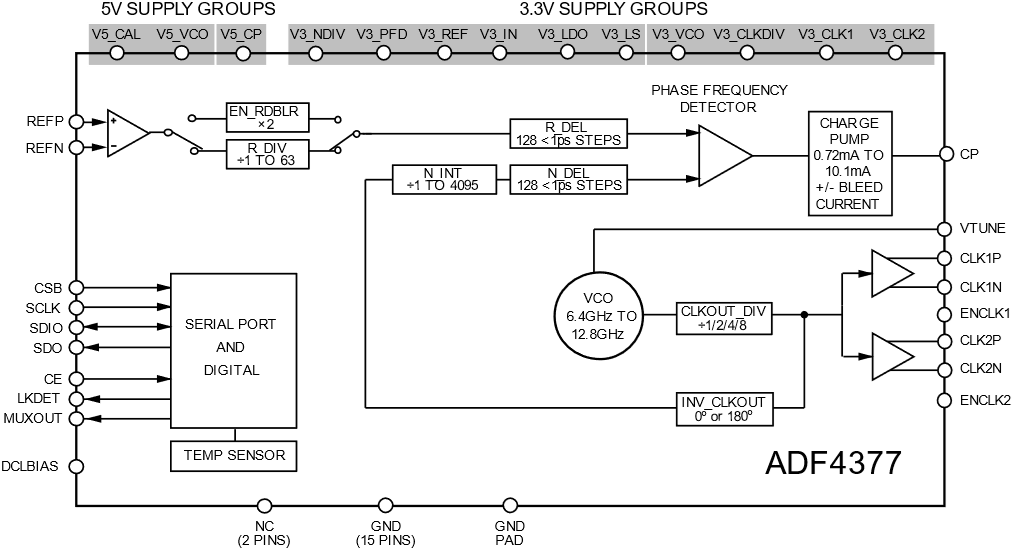

1. 输出频率高达12.8GHz,内置6.4-12.8GHzVCO,无需倍频,没有了FOUT/2和3*FOUT/2的谐波

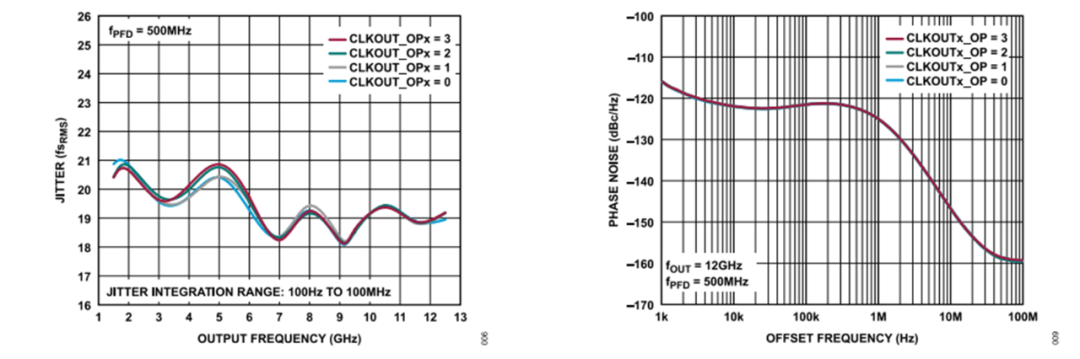

2. 超低时钟抖动:Jitter=18fs RMS (integration bandwidth: 100Hz to 100MHz), Jitter = 27 fs RMS (ADC SNR method)

3. 超低的宽带噪底:−160 dBc/Hz at 12 GHz,Low In-Band Phase Noise (PhN),In-Band PhN Floor = -239dBc/Hz (>3dB better than any other),In-Band 1/f PhN = -147dBc/Hz (>13dB better than any other)

4. 鉴相频率高达500MHz,输入基准源频率高达1GHz

图6 ADF4377系统框图

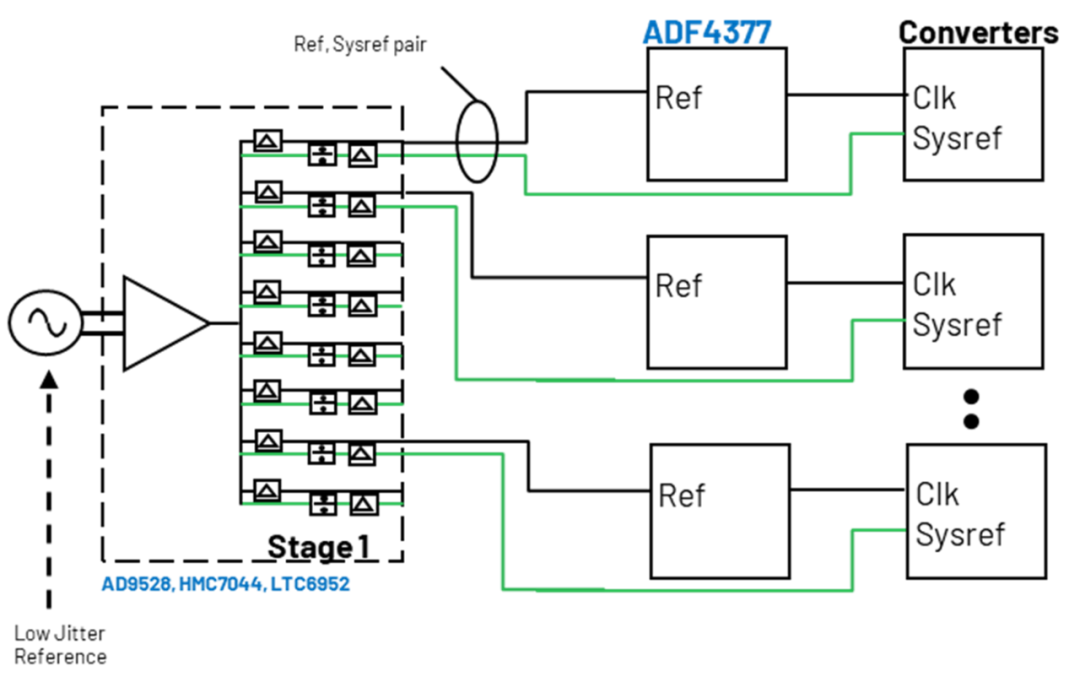

图7 ADF4377给高速数据转换系统提供低噪声时钟

图8 ADF4377的时钟抖动和相位噪声

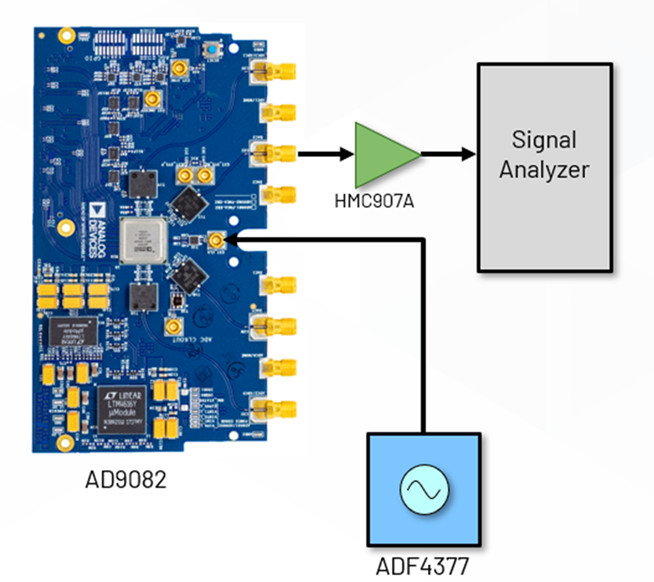

图9 ADF4377给AD9082提供时钟

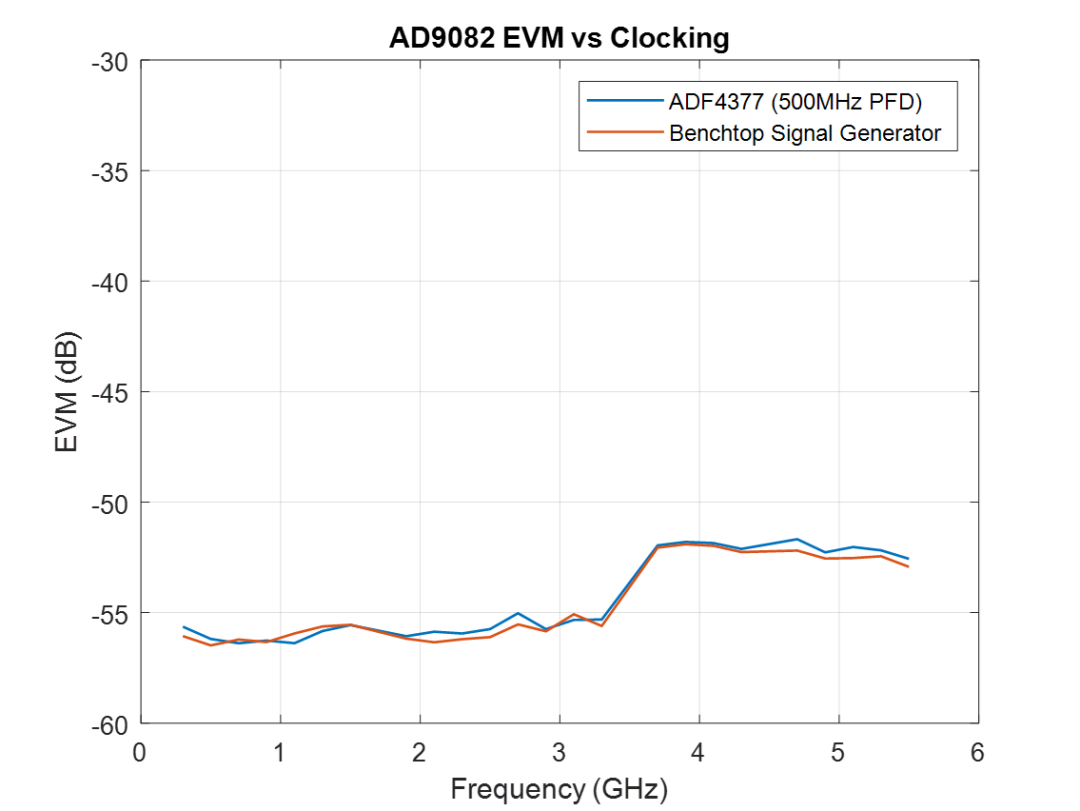

图10 ADF4377给AD9082提供时钟,EVM测试对比