本实验活动的目标是进一步强化上一个实验活动 “使用CD4007阵列构建逻辑功能” 中探讨的逻辑基本原理,并获取更多使用复杂门级电路的经验。具体而言,您将了解如何使用CMOS传输门和CMOS反相器来构建传输门异或(XOR)和异或非逻辑功能。

本文引用地址:背景知识

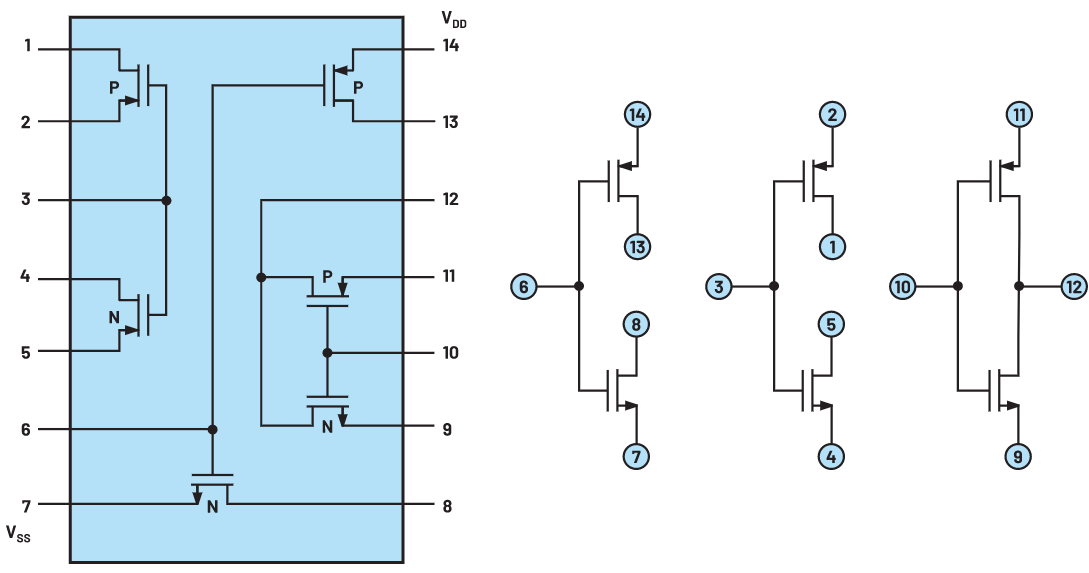

为了在本实验活动中构建逻辑功能,需要使用 ADALP2000 模拟部件套件中的CD4007 CMOS阵列和分立式NMOS和PMOS晶体管(ZVN2110A NMOS和ZVP2110A PMOS)。CD4007由3对互补MOSFET组成,如图1所示。每对共用一个栅极(引脚6、3和10)。所有PMOSFET(正电源引脚14)以及NMOSFET(地引脚7)的衬底都共用。左边一对,NMOS源极引脚连接到NMOS衬底(引脚7),PMOS源极引脚连接到PMOS衬底(引脚14)。另外两对均为通用型。右边一对,NMOS的漏极引脚连接到PMOS的漏极引脚,即引脚12。

图1.CD4007功能框图。

CD4007是一款多功能IC。例如,单个CD4007可用于构建三个反相器、一个反相器加上两个传输门或其他复杂的逻辑功能,如NAND和NOR门。反相器和传输门尤其适合构建传输门XOR和XNOR逻辑功能。XOR和XNOR逻辑门的示意图符号如图2所示。

图2.XOR和XNOR示意图符号。

静电放电

CD4007与许多CMOS集成电路一样,很容易被静电放电损坏。CD4007包括二极管,可防止其受静电放电的影响,但如果操作不当仍可能会损坏。使用对静电敏感的电子产品时,通常会使用防静电垫和腕带。然而,在家里(正规的实验环境之外)工作时,可能没有这些物品。避免静电放电的一种低成本方法是在接触IC之前先使自己接地。在操作CD4007之前,使积聚的静电放电将有助于确保在实验过程中不会损坏芯片。

材料

● ADALM2000 主动学习模块

● 无焊试验板

● 1个CD4007(CMOS阵列)

● 2个ZVN2110A NMOS晶体管

● 2个ZVP2110A PMOS晶体管

说明

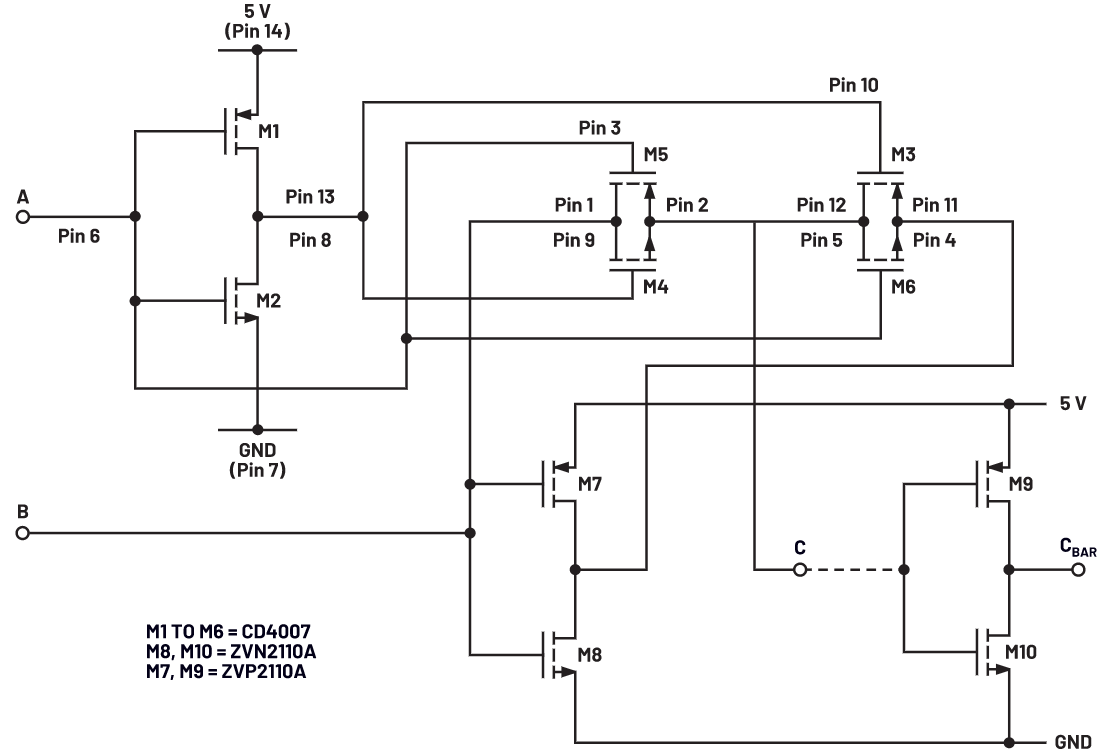

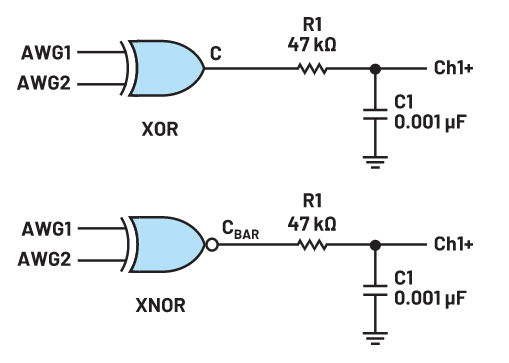

现在我们将使用单刀双掷(SPDT)传输门开关和两个CMOS反相器来构建XOR门(和XNOR),如图3所示。两个传输门协同工作以实现选择器操作。根据A输入的状态,输入B或输入B的反相会通过节点C (XOR)输出。另外两个反相器M9和M10使C反相以产生CBAR (XNOR)输出。

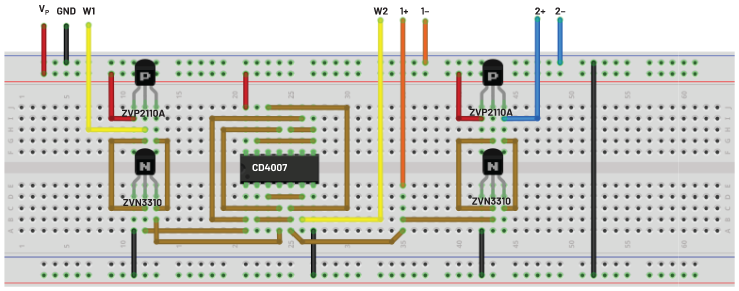

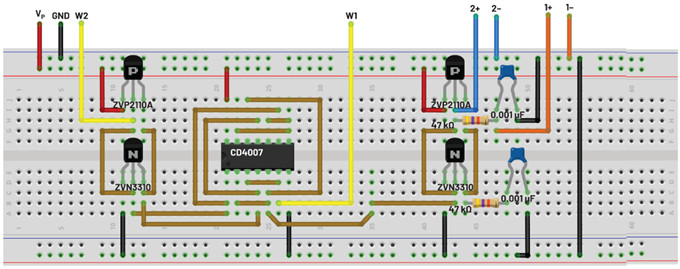

在无焊试验板上构建图3所示的XOR/XNOR电路。器件M1至M6采用CD4007 CMOS阵列,两个反相器级(反相器级M7和M8,以及M9和M10)分别使用ZVN2110A NMOS和ZVP2110A PMOS。电路使用ADALM2000的固定5 V电源供电。

电路中有两个逻辑输入A和B。同相XOR输出位于节点C,而该输出的反相位于节点CBAR以形成XNOR函数。

图3.XOR和XNOR门。

硬件设置

在实验最初,将两个AWG输出配置直流源。根据需要,示波器通道将用于监控电路的输入和输出。固定+5 V电源用于为电路供电。在此实验中,应禁用固定–5 V电源。

图4.XOR和XNOR门试验板电路。

程序步骤

将AWG1连接引脚6,作为A输入端。将AWG2连接引脚1和9,作为B输入端。示波器通道1连接引脚2、5和12,作为C输出端。示波器通道2连接M9和M10的漏极引脚,作为CBAR输出端。确保打开固定5 V电源。

首先,打开AWG控制界面并将AWG1设置为0 V直流电压,对A施加逻辑低电平。将AWG2设置为0 V直流电压,对B输入段施加逻辑低电平。

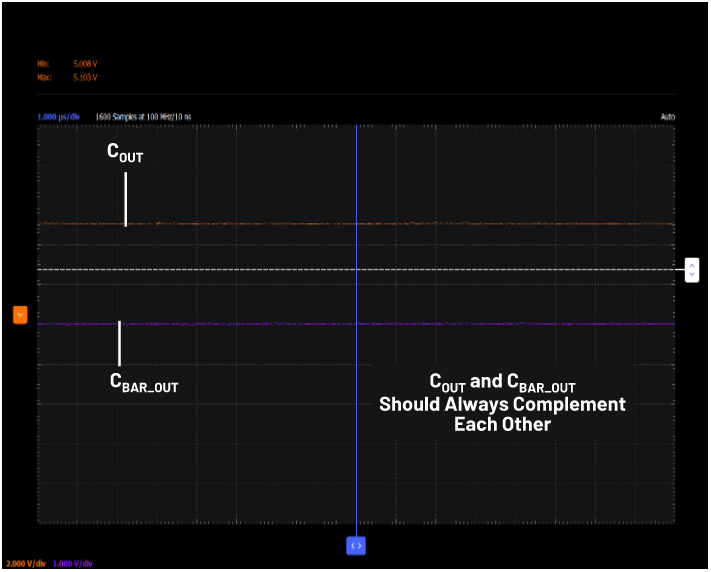

图5.COUT和CBAR输出。

观察示波器通道1上栅极的输出C。示波器界面上应显示稳定的直流电压。

现在将两个AWG通道均配置为具有5 V幅度峰峰值和2.5 V偏移(0 V至5 V摆幅)的方波。将AWG1设置为1 kHz频率,将AWG2设置为2 kHz频率或AWG1频率的两倍。确保将AWG设置为同步运行。

观察示波器界面上A和B输入信号相应的C输出和CBAR输出。

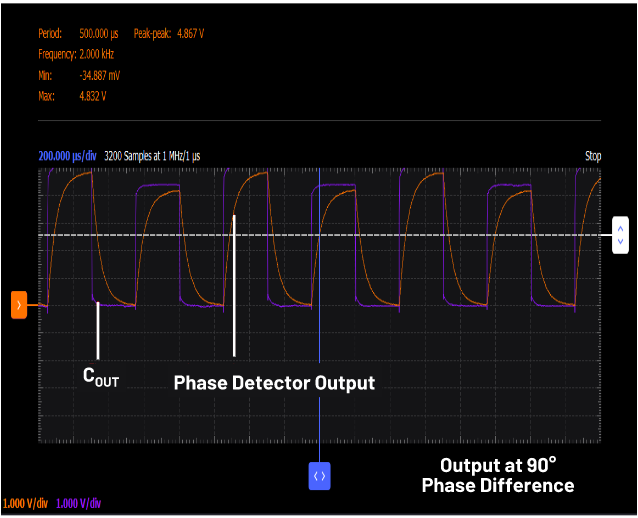

接着,将AWG2设置为与AWG1相同的1 kHz频率,但将AWG2的相位设置为90°。观察示波器界面上A和B输入信号相应的C输出和CBAR输出。

XOR门用作鉴相器

鉴相器或相位比较器是一种,用于产生代表两个逻辑信号输入之间相位差的模拟输出电压信号。它是锁相环(PLL)的中心元件。检测信号之间的相位关系是许多系统中的重要功能模块,如电机控制、雷达、电信、解调器和伺服机构。

方波信号的鉴相器可由XOR逻辑门组成。当比较的两个信号完全同相时,即相位差为0°,XOR门将输出恒定的零电平。例如,当两个信号的相位相差10°时,在10/180或1/18周期(两个信号值不同的极小部分周期)中,XOR门将输出高电平。当信号相位相差180°时,即一个信号为高电平而另一个为低电平,反之亦然,此时XOR门的输出在每个周期内都会保持高电平。

当XOR门鉴相器用于PLL系统时,它通常锁定在相位检测范围中间的90°相位差附近。在90°时,XOR具有50%占空比的方波输出,输出频率是输入频率的两倍。方波占空比根据两个输入信号的相位差发生变化。XOR门的输出通过低通滤波器产生的模拟电压与两个信号之间的相位差成正比。它需要对称的方波输入。如果一个输入的占空比与另一个输入的占空比略有不同,则低通滤波输出将会偏移90°相位差时的理想中间范围。

说明

将图6所示的RC低通滤波器添加到XOR试验板电路中。将示波器通道1连接到RC滤波器输出。

图6.XOR门鉴相器。

硬件设置

将两个AWG通道均配置为具有5 V幅度峰峰值和2.5 V偏移(0 V至5 V摆幅)的方波。将AWG1和AWG2的频率都设置为1 kHz。同时确保从AWG1和AWG2的相位都设置为0°开始。确保将AWG设置为同步运行。

图7.XOR门鉴相器试验板电路。

程序步骤

将示波器通道1连接到C1的RC滤波器输出,观察鉴相器的滤波(DC)输出。将示波器通道2连接到XOR门的输出C,观察逻辑门输出的脉冲宽度。

图8为Scopy波形图示例。

图8.XOR门鉴相器采样输出。

替代元件选择

使用四个独立NMOS和PMOS晶体管(ZVN2110A和ZVP2110A)构建的反相器对也可以由第二个CD4007 IC构成,或者可以是采用六路反相器IC的CMOS反相器,如74HC04或CD4049。CD4066四通道SPST开关也可以作为采用CD4007构建的开关的替代器件。

问题

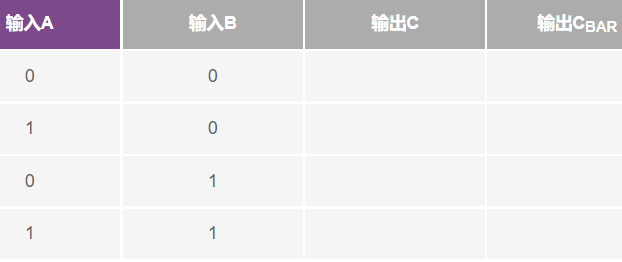

对于图3中的电路,将AWG1和AWG2设置为逻辑高电平(5 V)和低电平(0 V)值,并填入以下表格。

表1.每组输入(A和B)的输出值

您可以在 学子专区论坛上找到答案。

来源:

作者:Antoniu Miclaus 和 Doug Mercer