训练生成式人工智能(GenAI)神经网络模型通常需要花费数月的时间,数千个基于GPU并包含数十亿个晶体管的处理器、高宽带SDRAM和每秒数太比特的光网络交换机要同时连续运行。虽然人工智能(AI)有望带来人类生产力的飞跃,但其运行时能耗巨大,所以导致温室气体的排放也显着增加。

根据《纽约时报》报导,到2027年,人工智能服务器每年的用电量将达到85至134太瓦时(terawatt),大致相当于阿根廷一年的用电量。

为了应对日益加剧的能耗挑战,AI处理器的供电网络经历了多代的进化。这种全面的演进发展涉及电路架构、电源转换拓扑、材料科学、封装和机械/热工程方面的创新。

训练处理器的供电方案负载点和分比式模式的进化

从2020年到2022年,热设计功率(TDP)几乎翻了一番,从400W增加到了700W。TDP指标是指训练应用中GPU引擎的连续功耗。自2022年起,半导体行业的TDP水平不断攀升,到了2024年3月,市场上甚至出现了一款TDP高达1000W的GPU。

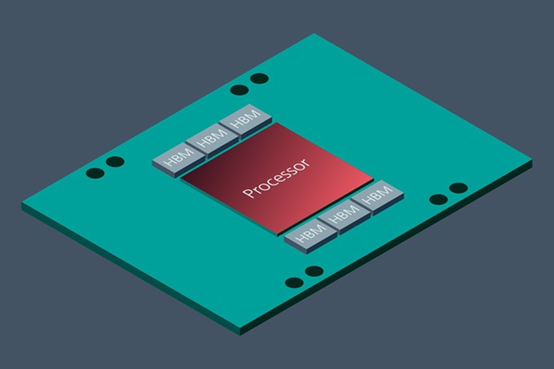

图一 : 基于GPU的训练处理器芯片复合体,加速器模块(AM)上安装有高宽带内存(HBM)

用于生成式AI训练的小芯片(chiplet)处理器复合体整合了一个GPU或ASIC芯片,以及六到八个高宽带内存(HBM)芯片。采用4奈米CMOS 制程的GPU通常以0.65V的内核VDD运行,可能包含1000亿或更多的晶体管。HBM提供144GB的储存容量,其工作电压一般为1.1V或1.2V。该处理器的一个关键供电特性与人工神经网络算法负载有关。对比处于空闲状态的GPU和算法满载状态的GPU,瞬态电流消耗(dI/dt)差别可能非常大,可能达到每微秒2000安培或更多。

此外,该处理器不能容忍较大的电源电压下冲或过冲幅值;这些负载阶跃瞬变必须限制在标称VDD的10%以内。设计用于生成式AI训练处理器的供电解决方案时,由于这些动态操作条件的原因,峰值电流输送能力通常设计为连续电流输送能力的两倍,峰值事件通常持续数十毫秒(图一)。

对于CPU、FPGA、网络交换机处理器以及现在的AI训练和推理芯片发展最重要的供电架构是负载点(PoL)方法。相较于传统的多相并联电源架构,分比式PoL电源架构实现了更高的功率和电流密度。这种电源架构借鉴了理想变压器的「匝数比」概念,通过分压实现电流倍增。电流倍增的可扩展性使我们能够根据不同的输出电压和电流需求,开发一系列全面的PoL转换器。这对客户来说至关重要,因为高级AI训练处理器的需求正快速变化。

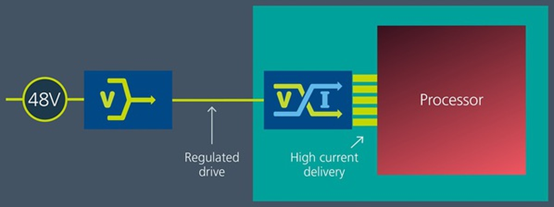

图二 : 分比式电源架构可以提供超过1000安培的大电流,并使供电网络的阻抗降低20倍

分比式电源架构(FPA)—分解为稳压和变压功能

生成式AI电源系统设计面临的主要挑战,包括:

‧ 很高的电流输送能力,范围从500安培到2000安培

‧ 负载需要出色的动态响应

‧ 巨大的PDN损耗和阻抗

‧ 48V母线基础架构的标准化使用,需要从48V转换到1V以下的能力

要解决这种大电流和高密度负载点(PoL)问题,需要采用不同的方法。先进的分比式电源架构将稳压和变压/电流倍增功能进行了分解,可将这些供电级放置在最佳位置,从而达到最高的效率和功率/电流密度。

当输入电压(VIN)等于输出电压(VOUT)时,稳压器的效率最高,随着输入输出比的增加,效率逐渐降低。在36至60V的典型输入电压范围内,最佳输出母线电压将是48V,而不是中继母线架构(IBA)中常见的传统12V母线电压。48V输出母线所需的电流是12V母线的四分之一(P=VI),而PDN的损耗是电流的平方(P = I2R),这意味着损耗降低至原来的 1/16。

因此,先安装稳压器并将其调节至48V输出,可以实现最高的效率。稳压器还必须接受有时低于48V的输入电压,这就需要一个降压-升压的功能来满足这一设计需求。一旦输入电压得到了稳压,下一步便是将48V转换为1V。

在需要为1V负载供电的情况下,最佳变压比为48:1。在这种情况下,稳压器将输入电压降压或升压到48V输出,再由变压器将电压从48降至1V。降压变压器以相同的比率加大电流,因此变压器组件也可以称为电流倍增器。在这种情况下,1安培的输入电流将倍增至48安培的输出电流。为了最大限度地减少大电流输出的PDN损耗,电流倍增器必须小巧,以便尽可能靠近负载放置。PRM稳压器和VTM/MCM模块化电流倍增器结合,构成Vicor分比式电源架构。这两个器件相互合作,各司其职,实现完整的DC-DC转换功能。

PRM通过调制未稳压的输入电源提供稳压输出电压,即「分比式母线电压」。该母线供电给VTM,由VTM将分比式母线电压转换为负载所需的电平。

与IBA不同,FPA不通过串联电感器从中继母线电压降压至PoL。FPA不通过降低中间母线电压来平均电压,而是使用电流增益为1:48或更高的高压稳压和电流倍增器模块,以提供更高的效率、更小的尺寸、更快的响应和1000安培及以上的可扩展性(图二)。

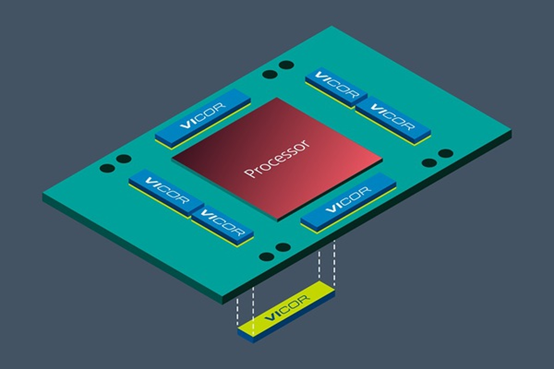

垂直放置PoL转换器减少功耗耗散

在前几代大电流生成式AI处理器电源架构中,PoL转换器被放在处理器复合体的横向(旁边)位置。由于铜的电阻率和PCB上的走线长度,横向放置的PoL供电网络(PDN)的集总阻抗相当高,可能达到200μΩ或更高。随着生成式AI训练处理器的连续电流需求增加到1000安培,这意味着PCB本身就会消耗掉200瓦的功率。考虑到在AI超级计算机中用于大型语言模型训练的加速器模块(AM)多达数千个,而且几乎从不断电,通常会持续运行10年或更长时间,这200瓦的功率损耗在整体上变得非常庞大。

认识到这种能源浪费后,AI计算机设计师已经开始评估采用垂直供电(VPD)结构,将PoL转换器直接放置在处理器复合体的下方。在垂直供电网络中,集总阻抗可能降至10μΩ或更低,这意味着在内核电压域1000安培的连续电流下,只会消耗10瓦的功率。也就是说,通过将PoL转换器从横向放置改为纵向放置,PCB的功耗减少了200–10=190瓦(WPCB)(图三)。

图三 : 生成式AI加速模块从横向(顶部)供电改为纵向(背部)供电,可将PDN损耗降低至1/20

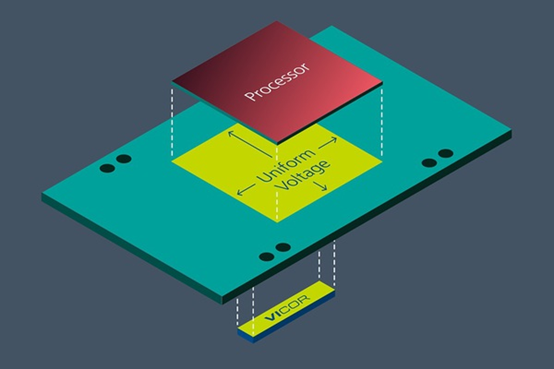

PD的另一个优点是降低了GPU芯片表面电压梯度,这也有助于节省电力。如前所述,典型的4奈米CMOS GPU的标称工作电压为0.65VDD。使用横向供电时,将电源提供给处理器复合体的四边,由于集成电路的配电阻抗较高(通常使用电阻率高于铜的铝导体),可能需要0.70V的电压,才能确保GPU芯片中心的电压达到标称值0.65V。而采用纵向供电时,可以确保整个芯片表面的电压为0.65V。0.70–0.65=50 mV,这个差值乘以1000安培,可额外节省50瓦(WVDD)的功率。在本例中,节省的总功率为190 WPCB + 50 WVDD = 240瓦(图四)。

根据未来几年公共领域对加速器模块(AM)需求的预测(2024年超过250万件),以及对电力成本的合理估计(每兆瓦时75美元),每个AM节省240W电力,到2026年将在全球范围内实现太瓦时的电力节省,相当于每年节约数十亿美元的电力营运成本,而且根据可再生能源的使用比例,每年还能永久性地减少数百万吨的二氧化碳排放。

图四 : 使用VPD时,处理器芯片的表面电压均匀,有助于最大限度地提高计算效能,同时最小化功率损耗。

遏制失控的生成式AI功耗

Vicor正引领生成式AI供电技术的创新浪潮,所提供的分比式负载点转换器解决方案有助于提升生成式AI处理器的功效,使生成式AI的功耗与社会层面的环境保护和节能目标相一致。

Vicor持续推动电源架构的创新,并开发先进的新产品,致力于解决生成式AI模型训练带来的功耗增加问题。通过采用先进的分比式电流倍增器方法进行负载点DC-DC转换,就可以充分发挥生成式AI优势,同时有效控制全球范围内的能源消耗。

(本文作者翁鸿裕为Vicor 中国台湾总经理)

生成式AI助功率密集的计算应用进化

发布时间: 2024-06-13

来源: 电子产品世界

文章来源于: 电子产品世界

原文链接

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。