8051单片机的四组I/O端口

1.概述

单片机的I/O端口是输入信号和输出信号的通道。8051单片机有P0、P1、P2、P3四组I/O 端口,每组端口有8个引脚。

2.P0端口

2.1 概述

P0端口有P0.0~P0.7共8个引脚,这些引脚除了可用作输入引脚和输出引脚外,在外接存储器时,还可用作地址/数据总线引脚。P0端口每个引脚的内部电路结构都相同,其内部电路结构如图1所示。

图1 P0端口的内部电路结构图

2.2 P0端口用作输出端口的工作原理

下面讲解单片机需要从P0.x 引脚输出高电平“1”。如图1所示,单片机内部相关电路通过控制线送出“0(低电平)”到与门的一个输入端和电子开关的控制端,控制线上的“0”一方面使与门关闭(即与门的一端为“0”时,不管另一端输入何种信号,输出都为“0”),晶体管VT1栅极为“0”处于截止,地址/数据线送来的信号无法通过与门和晶体管VT1;控制线上的“0”另一方面控制电子开关,让电子开关与锁存器的端连接。CPU 再从内部总线送高电平“1”到锁存器的D端,同时往锁存器的CL端送写锁存器信号,D端的“1”马上存入锁存器并从Q和端输出,D 端输入“1”,Q 端输出“1”,端则输出“0”,端输出“0”经电子开关送到晶体管VT2的栅极,VT2截止,由于VT1也处于截止,P0.x引脚处于悬浮状态,因此需要在P0.x引脚上接上拉电阻,在VT2截止时,P0.x引脚输出高电平。

下面讲解单片机需要从P0.x 引脚输出高电平“0”。如图1所示,单片机内部相关电路通过控制线送出“0(低电平)”到与门的一个输入端和电子开关的控制端,控制线上的“0”一方面使与门关闭(即与门的一端为“0”时,不管另一端输入何种信号,输出都为“0”),晶体管VT1栅极为“0”处于截止,地址/数据线送来的信号无法通过与门和晶体管VT1;控制线上的“0”另一方面控制电子开关,让电子开关与锁存器的端连接。CPU 再从内部总线送高电平“0”到锁存器的D端,同时往锁存器的CL端送写锁存器信号,D端的“0”马上存入锁存器并从Q和端输出,D 端输入“0”,Q 端输出“0”,端则输出“1”,端输出“1”经电子开关送到晶体管VT2的栅极,VT2导通,由于VT1处于截止,P0.x引脚处于悬浮状态,因此需要在P0.x引脚上接上拉电阻,在VT2导通时,P0.x引脚输出低电平。

总的来说,当单片机需要将P0端口用作输出端口时,内部CPU会送控制信号“0”到与门和电子开关,与门关闭(上晶体管VT1同时截止,将地址/数据线与输出电路隔开),电子开关将锁存器与输出电路连接,然后CPU通过内部总线往P0端口锁存器送数据和写锁存器信号,数据通过锁存器、电子开关和输出电路从P0端口的引脚输出。在P0端口用作输出端口时,内部输出电路的上晶体管处于截止(开路),下晶体管的漏极处于开路状态(称为晶体管开漏),因此需要在P0端口引脚接外部上拉电阻,否则无法可靠输出“1”或“0”。

2.3 P0端口用作输入端口的工作原理

如图1所示,当单片机需要将P0端口用作输入端口时,内部CPU会先往P0端口锁存器写入“1”(往锁存器D端送“1”,同时给CL端送写锁存器信号),让,VT2截止,关闭输出电路。P0端口引脚输入的信号送到输入三态门的输入端,此时CPU再给三态门的控制端送读引脚控制信号,输入三态门打开,P0端口引脚输入的信号就可以通过三态门送到内部总线。

如果单片机的CPU需要读取P0端口锁存器的值(或称读取锁存器存储的数据),会送读锁存器控制信号到三态门(上方的三态门),三态门打开,P0锁存器的值(Q 值)经三态门送到内部总线。

2.4 P0端口用作地址/数据总线的工作原理

如图1所示, 如果要将P0端口用作地址/数据总线,单片机内部相关电路会通过控制线发出“1”,让与门打开,让电子开关和非门输出端连接。当内部地址/数据线为“1”时,“1”一方面通过与门送到 VT1的栅极,VT1导通,另一方面送到非门,反相后变为“0”,经电子开关送到VT2的栅极,VT2截止,VT1导通,P0端口引脚输出为“1”;当内部地址/数据线为“0”时,VT1截止,VT2导通,P0端口引脚输出“0”。

总的来说,当单片机需要将P0端口用作地址/数据总线时,CPU会给与门和电子开关的控制端送“1”,与门打开,将内部地址/数据线与输出电路的上晶体管 VT1接通,电子开关切断输出电路与锁存器的连接,同时将内部地址/数据线经非门反相后与输出电路的下晶体管VT1接通,这样VT1、VT2状态相反,让P0端口引脚能稳定输出数据或地址信号(1或0)。

3.P1端口

3.1 概述

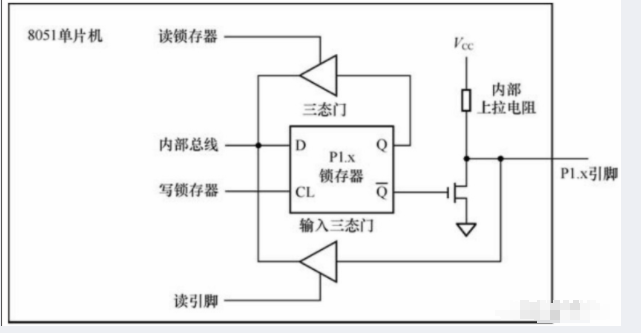

P1端口有P1.0~P1.7共8个引脚,这些引脚可作输入引脚和输出引脚。P1端口每个引脚的内部电路结构都相同,其内部电路结构如图2所示。P1端口的结构较P0端口简单很多,其输出电路采用了一个晶体管,在晶体管的漏极接了一只内部上拉电阻,所以在 P1端口引脚外部可以不接上拉电阻。

图2 P1端口的内部结构电路图

3.2 P1端口用作输出端口的工作原理

如图2所示,当需要将P1端口用作输出端口时,单片机内部相关电路除了会往给锁存器的D端送数据外,还会往锁存器CL端送写锁存器信号,内部总线送来的数据通过D端进入锁存器并从Q和端输出,当D端输入“1”,则端输出“0”(Q端输出“1”),端的“0”送到晶体管的栅极,晶体管截止,从P1端口引脚输出“1”。 当D端输入“0”,则端输出“1”(Q端输出“0”),端的“1”送到晶体管的栅极,晶体管导通,从P1端口引脚输出“0”。

3.3 P1端口用作输入端口的工作原理

如图2所示,当需要将 P1端口用作输入端口时,单片机内部相关电路会先往 P1锁存器写“1”,让Q=1、,会使晶体管截止,关闭P1端口的输出电路,然后CPU往输入三态门控制端送一个读引脚控制信号,输入三态门打开,从 P1端口引脚输入的信号经输入三态门送到内部总线。

4.P2端口

4.1 概述

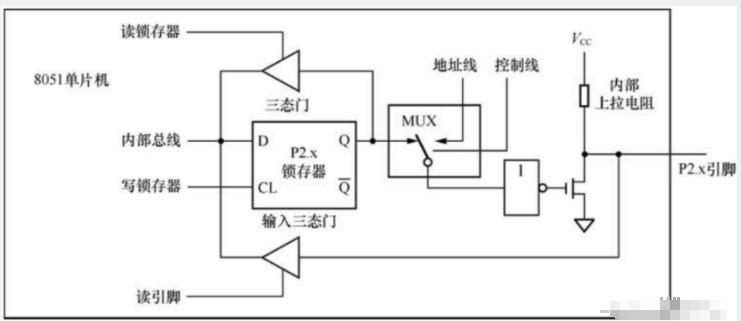

P2端口有P2.0~P2.7共8个引脚,这些引脚除了可用作输入引脚和输出引脚外,在外接存储器时,还可用作地址总线(高8位)引脚。P2端口每个引脚的内部电路结构都相同,其内部电路结构如图3所示。

图3 P2端口内部结构电路图

4.2 P2端口用作输出端口的工作原理

如图3所示,当需要将P2端口用作I/O端口时,单片机内部相关电路会送控制信号到电子开关的控制端,让电子开关与P2锁存器的Q端连接。若要将P2端口用作输出端口,CPU会通过内部总线将数据送到锁存器的D端,同时给锁存器的CL端送写锁存器信号,D端数据存入锁存器并从Q端输出,再通过电子开关、非门和晶体管从P2端口引脚输出。

4.3 P2端口用作输入端口的工作原理

如图3所示,当需要将P2端口用作I/O端口时,单片机内部相关电路会送控制信号到电子开关的控制端,让电子开关与P2锁存器的Q端连接。若要将P2端口用作输入端口,CPU会先往P2锁存器写“1”,让Q=1、,Q=1会使晶体管截止,关闭P2端口的输出电路,然后CPU往输入三态门控制端送一个读引脚控制信号,输入三态门打开,从P2端口引脚输入的信号经输入三态门送到内部总线。

4.4 P2端口用作地址总线引脚的工作原理

如图3所示,如果要将 P2端口用作地址总线引脚,单片机内部相关电路会发出一个控制信号到电子开关的控制端,让电子开关与内部地址线接通,地址总线上的信号就可以通过电子开关、非门和晶体管后从P2端口引脚输出。

5.P3端口

5.1 概述

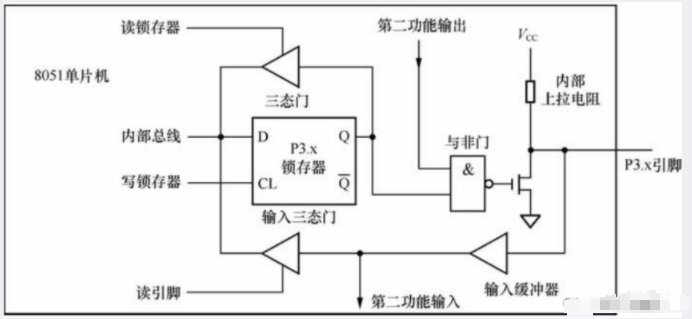

P3端口有P3.0~P3.7共8个引脚,P3端口除了可用作输入引脚和输出引脚外,还具有第二功能。P3端口每个引脚的内部电路结构都相同,其内部电路结构如图4所示。

图4 P3端口内部结构电路图

5.2 P3端口用作输出端口的工作原理

如图4所示,当需要将P3端口用作I/O端口时,单片机内部相关电路会送出“1”到与非门的一个输入端(第二功能输出端),打开与非门(与非门的特点是:一个输入端为“1”时,输出端与另一个输入端状态始终相反)。若要将P3端口用作输出端口,CPU给锁存器的CL端送写锁存器信号,内部总线送来的数据通过D端进入锁存器并从Q端输出,再通过与非门和晶体管两次反相后从P3端口引脚输出。

5.3 P3端口用作输入端口的工作原理

如图4所示,当需要将P3端口用作I/O端口时,单片机内部相关电路会送出“1”到与非门的一个输入端(第二功能输出端),打开与非门(与非门的特点是:一个输入端为“1”时,输出端与另一个输入端状态始终相反)。若要将P2端口用作输入端口,CPU会先往P3锁存器写“1”,让Q=1,与非门输出“0”,晶体管截止,关闭P3端口的输出电路,然后CPU往输入三态门控制端送一个读引脚控制信号,输入三态门打开,从P3端口引脚输入的信号经过输入缓冲器和输入三态门送到内部总线。

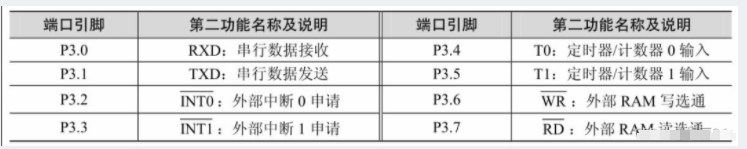

5.4 当P3端口用作第二功能时

P3端口的每个引脚都有第二功能,具体见下表。P0端口用作第二功能(又称复用功能)时,实际上也是在该端口输入或输出信号,只不过输入、输出的是一些特殊功能的信号。当单片机需要将 P3 端口用作第二功能输出信号(如、信号)时,CPU 会先往P3 锁存器写“1”, Q=1,它送到与非门的一个输入端,与非门打开,内部的第二功能输出信号送到与非门的另一个输入端,反相后输出去晶体管的栅极,经晶体管再次反相后从 P0端口引脚输出。当单片机需要将P3端口用作第二功能输入信号(如T0、T1信号)时,CPU也会往P3锁存器写“1”,Q=1,同时第二功能输出端也为“1”,与非门输出为“0”,晶体管截止,关闭输出电路,P0端口引脚输入的第二功能信号经输入缓冲器送往特定的电路(如T0、T1计数器)。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。