如何优化隔离栅级驱动电路?

栅极驱动光电耦合器FOD31xx系列的功能是用作电源缓冲器,来控制功率MOSFET或IGBT的栅极。它为MOSFET 或 IGBT 的栅极输入供应所需的峰值充电电流,来打开器件。该目标通过向功率半导体的栅极提供正压(VOH)来实现。若要关闭MOSFET或IGBT,需拉起驱动器件的栅极至0电压(VOL)或更低。

本文引用地址:标准栅极驱动光电耦合器如何工作?

栅极驱动光电耦合器FOD31xx系列的功能是用作电源缓冲器,来控制功率MOSFET或IGBT的栅极。它为MOSFET 或 IGBT 的栅极输入供应所需的峰值充电电流,来打开器件。该目标通过向功率半导体的栅极提供正压(VOH)来实现。若要关闭MOSFET或IGBT,需拉起驱动器件的栅极至0电压(VOL)或更低。

许多功率控制应用采用两个或两个以上串联功率半导体的“图腾柱”上桥和下桥连接。上桥N沟道MOSFET漏极连接至电源的正极(+)端子,并且它的源极连接至下桥晶体管的漏极上。下桥晶体管的源极连接至系统电源的负极(-)端。负载驱动的一端连接至上桥和下桥晶体管的共节点处。上桥和下桥晶体管的正确控制,要求两个晶体管既不能同时开启也不能同时导通。流入串联上桥和下桥器件的电流被称为“直通”电流。直通电流浪费功率,并导致上桥和下桥晶体管的损坏。

消除直通电流的最常见技术是:在上桥和下桥开关切换之间添加延迟或延时。该延迟的引入,是通过控制供应给上桥和下桥栅极驱动器的信号的时间。

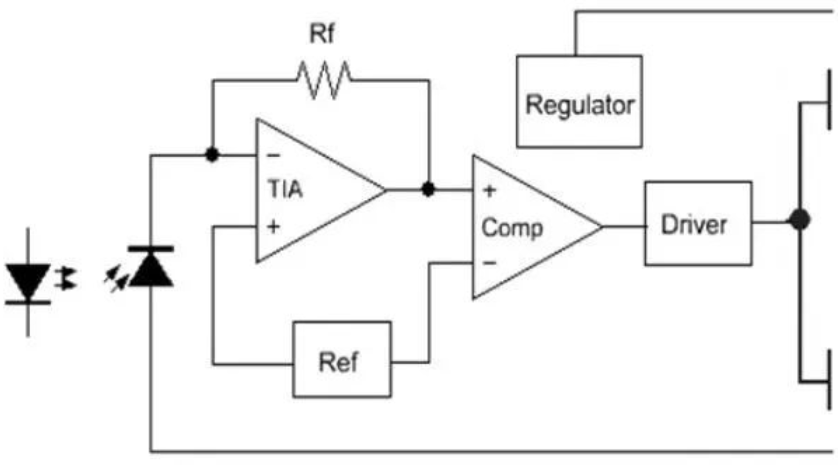

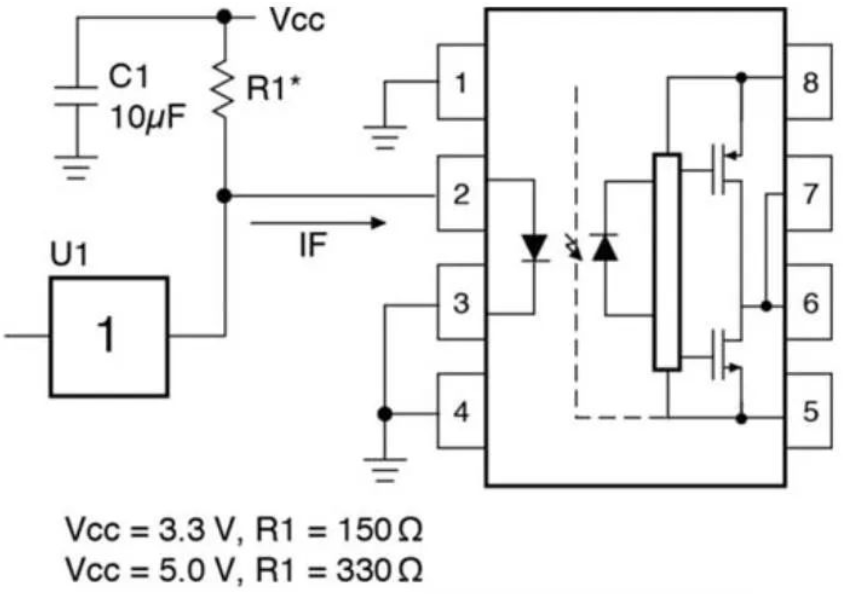

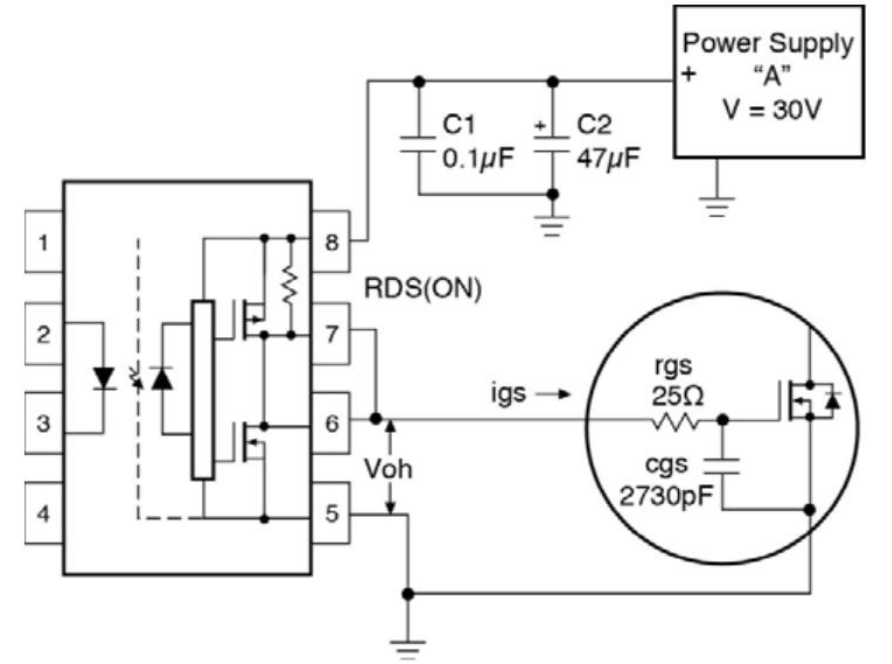

图1是栅极驱动器内部框图。驱动器的每个部分由一个通用电源或偏置电源供电。初始电源开启时,由于电路的复杂性而存在电路延迟。这些复杂性导致一种情况(在最初上电期间):当栅极的输出跟随施加的VDD电源的上升沿,直至电源稳定。一旦偏置电平正确,栅极驱动器输出返回至正确的状态:由LED控制。

本应用指南讨论了关键的设计标准,包括LED驱动、初始条件、最大开关频率和功率。

图1 FOD31xx框图

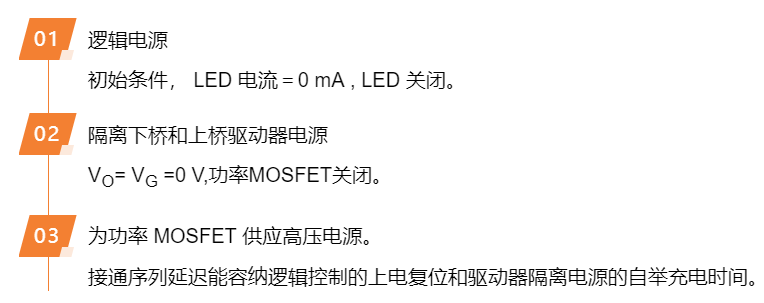

初始条件:器件启动

工作条件

在典型逆变器应用中有三个电源。第一个是逻辑电源(+3.3 V 或+5 V 或+10 V )。第二个是隔离下桥和上桥驱动器电源(+20 V FOD3182、+25VFOD3120)。第三个是供应给MOSFET / IGBT的高压电源。为了最小化偏压电源稳定时间的任何影响,一种解决方案是控制电源激活的顺序:

LED驱动器

峰值正向电流,IF(peak),为<1 A (1 μs ,300 pps )。推荐的工作电流为10 mA 至16 mA 。电流上升速率低于250 ns 。LED电流上升的最快速率将最小化传播延迟和输出开关抖动。

电源考虑因素

FOD31xx产品是高增益(23 db)、高功率输出、光放大器。它们所需的电源带有低输出阻抗,在DC至40 MHz 范围内。使用低 ESR旁路电容和信号接地面,有助于减少自感应电源噪声,并防止输出上升和下降时间的降低。

在FOD3182上的传播延迟

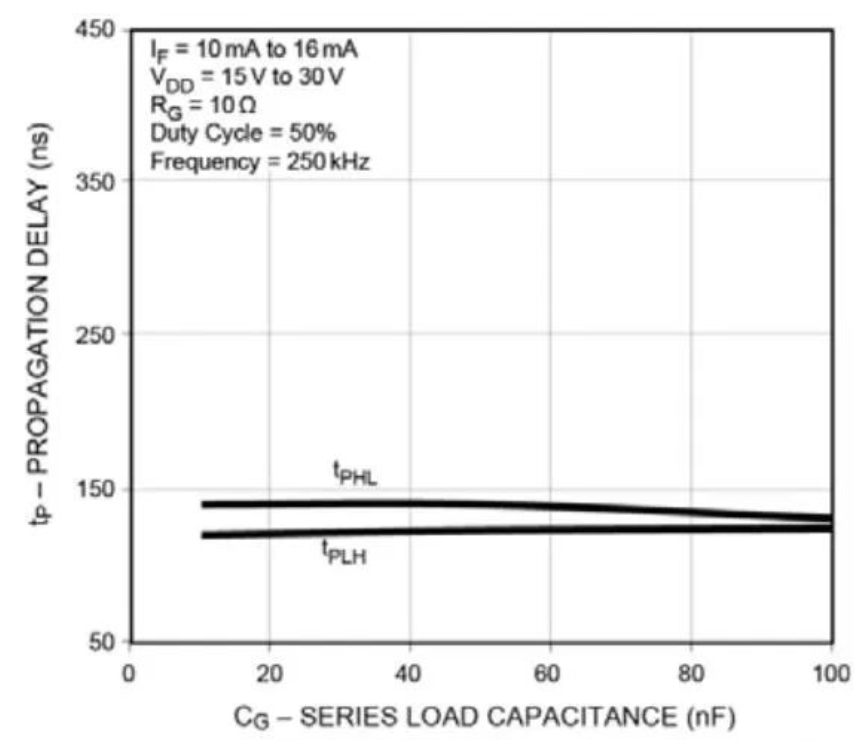

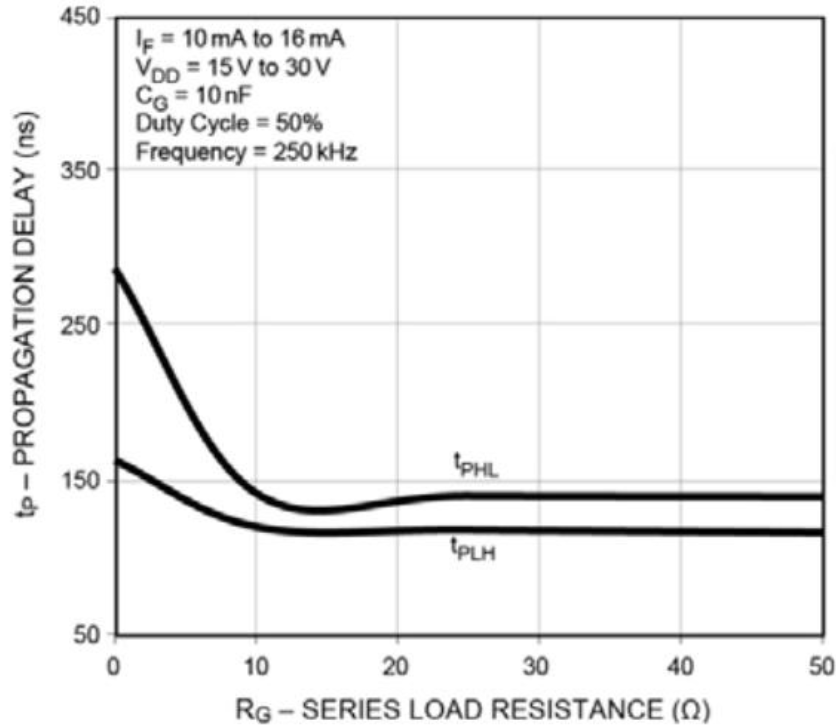

图2表明,传播延迟与负载电容无关,并且,典型脉宽失真度(PWD)小于40 ns。

图2 传输延迟与串联负载电阻

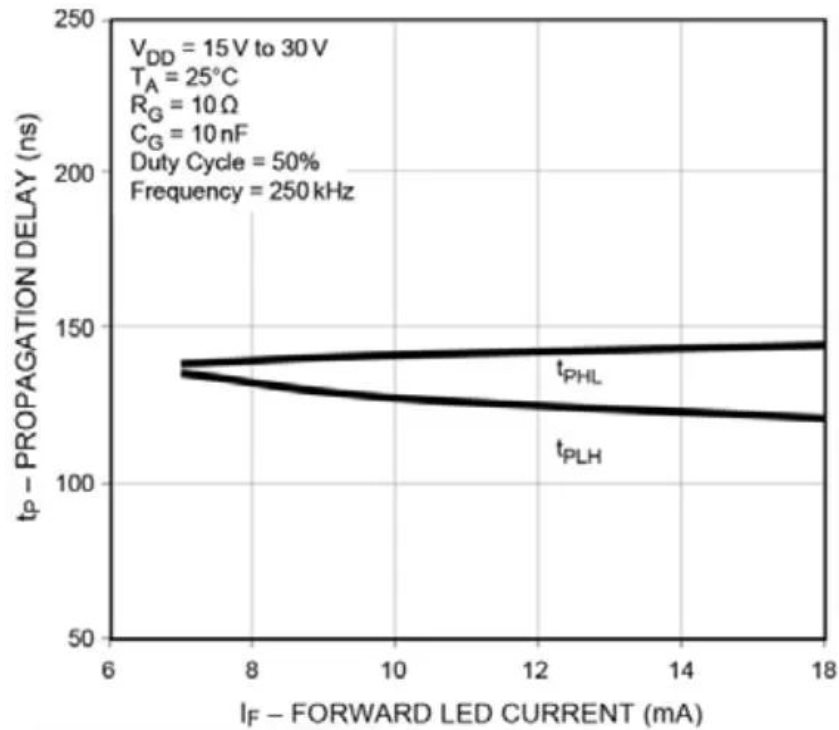

图3表明,传播延迟取决于LED电流。典型PWD是+4 ns / mA 。

图3 传播延迟与正向 LED 电流

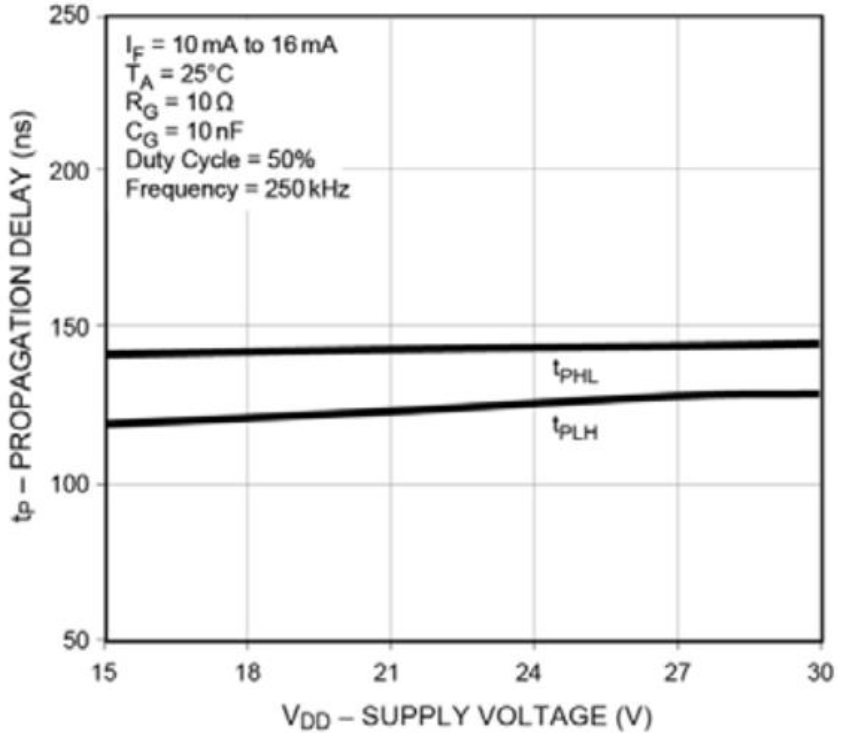

图4和图5说明了延迟的独立性与串联负载和电源电压有关。

图4 传输延迟与串联负载电阻

图5 传输延迟与电源电压

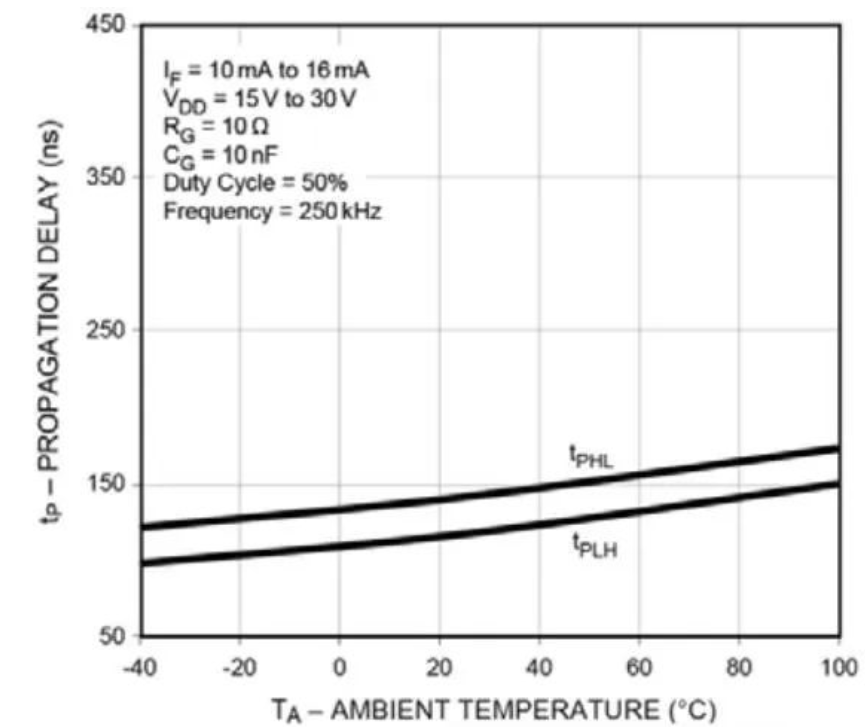

采用温度稳定LED、温度补偿放大器和电流源,传播延迟在-40℃至100℃间的变化通常是+0.2 ns /℃,如图6所示。

图6 传播延迟与TA

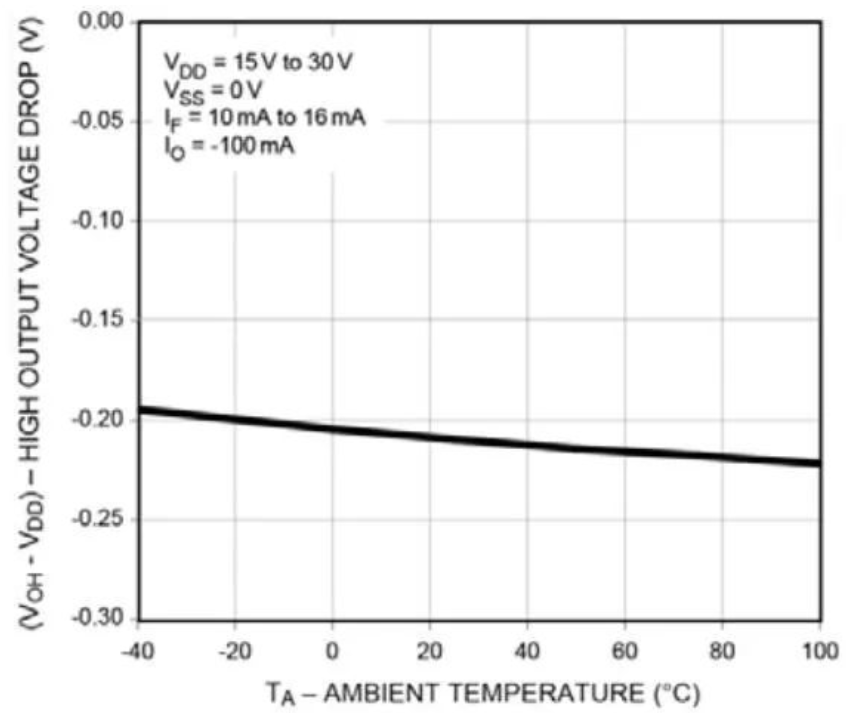

采用P沟道MOSFET作为上拉与双极性晶体管相比,有两个优点:第一,低 RDS(ON)可实现最小的内部电压降,为给定的VCC-VEE提供较大的接通电压。其次,开关延迟比多级PNP晶体管小。图7是FOD3120的压降曲线。

图7 输出高压降与TA

门驱动 CMTI(或噪声抑制)性能

光隔离MOSFET和IGBT驱动器可提供在负载的高压和应用控制逻辑之间的安全绝缘和噪声隔离。FOD31xx系列的共面结构提供高电介质隔离和低输入至输出电容,优化了安全性和最小化了噪声耦合。该封装结构使其安全性符合美国和欧洲标准,工作电压超过800 V 。

由负载开关产生的电气噪声引起的干扰通过共面光耦合技术受阻,并且特殊的电一一光屏蔽进一步减少了开关瞬变至栅极驱动器有源电路间的电容耦合。

一个典型的240 VAC交流电源转换器可产生800 V的开关瞬变,压摆率大于6kV/ μs 。这样巨大的瞬变会在输入和输出之间产生一个3 mA的峰值电流(当应用于一个只有0.5 pF的CIo的隔离器件时)参见图8。

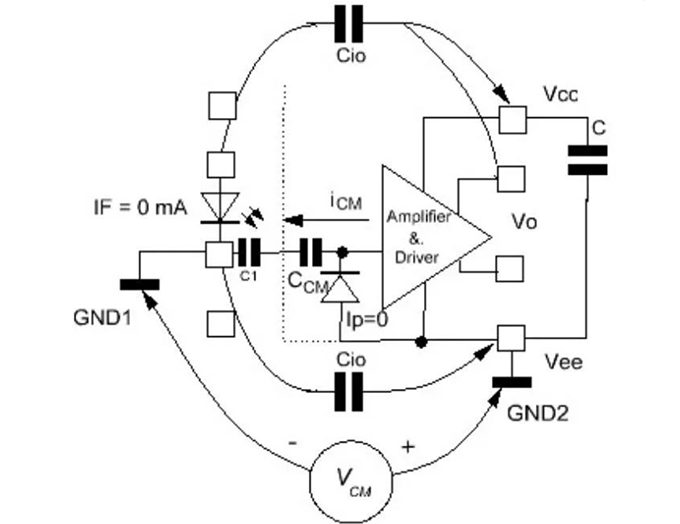

图8 CMTI LED关闭

图8表明,电容耦合了耦合器输入和输出之间的噪声电流。本例中,以耦合器的输出地(GND2)为参考,共模瞬变出现一个负电压摆幅。该瞬变将电流从耦合器的输出引至输入。封装电容CO,在输入和输出之间提供主导耦合阻抗。LED关闭,因此栅极输出处于低电平状态。如果从放大器的输入端引出足够的共模电流icM光放大器将开启。这种噪声电流icM相当小,因为特殊的共模屏蔽阻止了电场变化效应。这种屏蔽导致有效的共模电容耦合低于50 fF。这种共模屏蔽可最小化光放大器的耦合输入或输出。因此,FOD31xx系列抑制了峰值振幅为1.5 kV和压摆率超过15 kV / μs 的正/负共模瞬变。

以下总结了FOD31xx系列共模瞬变( CMT )的影响:

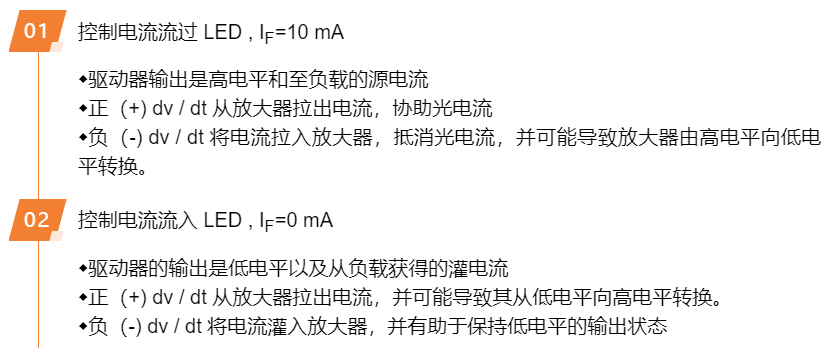

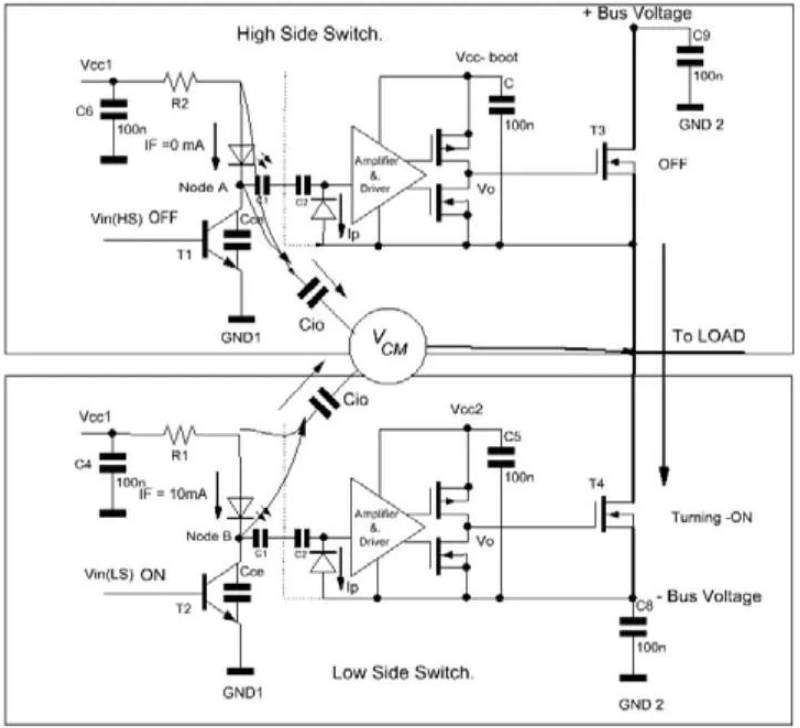

输入共模瞬态抑制性

图9和图10表明,半桥或“ H ”桥式图腾柱配置采用两个功率 MOSFET 。图9表示下桥开关,而图10表示上桥开关。触发操作前,一端是打开的,另一端是关闭的。一旦开关触发操作发生,两个开关都禁用,形成关闭驻留或“死区”时间。

图9 下桥打开、上桥关闭、负CMT

图9表示下桥IGBT所产生的CMT导通。

这种载荷开关动作产生负dv/dt,如H桥式的两个开关。在这种开关动作中没有载荷直通电流发生尤为重要。请注意,输入LED通常是串联转换连接。如果上桥门驱动器瞬时接通下桥开关开启,可能导致直通故障。图10表示CMT引出电流流入上桥LED 。

LED电流的幅度取决于:CMT的 dv / dt 、组件的输入-输出寄生电容以及LED周围阻抗。这些阻抗包括:LED电流设置电阻R2和驱动LEDT1时的CCE。

逆变器用于产生240 VAC电源,可产生脉冲宽度大约为100 ns 、3 mApk的LED电流。该脉宽足以激活上桥驱动器并导致直通故障。通过减少LED周围的断态阻抗可以最大限度地减少该故障的敏感度。这些较低的阻抗为﹣ dv / dt开关动作造成的CMT电流提供备选路径。如图9所示,- dv / dt开关动作产生CMT ,也可通过下桥 IGBT 驱动器看到。此瞬态尝试引出电流流入下桥LED。此瞬态效应最小。LED已经开启,迫使更多的LED电流仅获得正确的下桥开关动作,并且,增量CMT电流通过晶体管T2并联至GND1。

图10 正 dv / dt ﹣高端开关导通

当高端开关导通时将产生正dv / dt 。图10表明,该+ dv / dt 的效果是:关闭低端开关。正CMT能够引出电流流入低端驱动器内的 OFF LED 。如果 dv / dt足够大,该CMT立即迫使低端IGBT驱动器导通。该正CMT也可以通过高端开关看到。该dv / dt通常有助于保持高端驱动器导通。

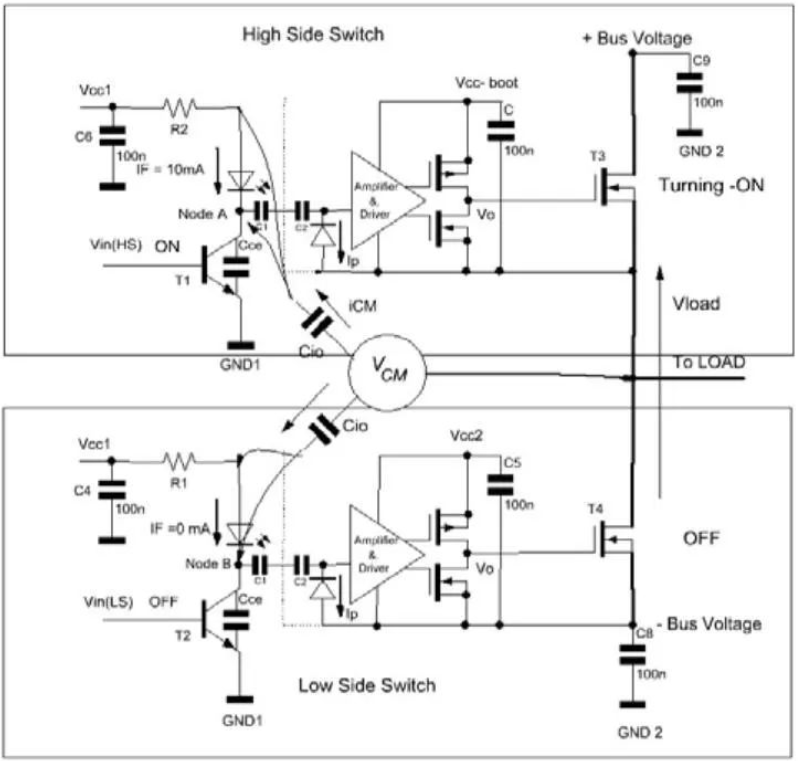

LED并联驱动器最小化开关CMT

当图腾柱半桥电流应用中采用FOD31xx驱动器时,CMTI是必要的。在正常电路工作期间,开关瞬变至关重要,不会导致关闭的栅极驱动器转为导通状态。这种由于半桥式图腾柱操作自诱式导通,需要LET联驱动器改善抗噪声能力。

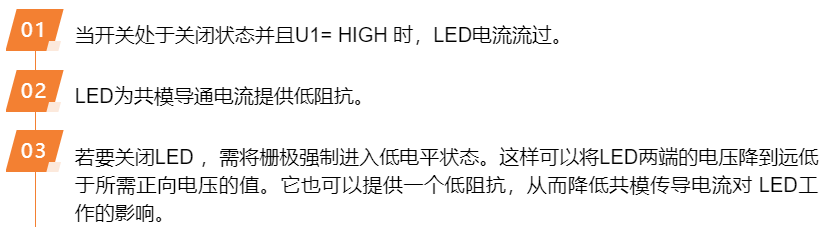

在上个例子中,LED三以串联方式与驱动器配置连接。CMT能通过封装吸收或灌入电流CIO ,导致OFF LED导通。常关LED在关闭状态提供相对较高的阻抗。这种潜在问题,可以通过减小LED关闭状态阻抗来消除。当LED关断时,通过在LED周围提供低阻抗并联路径来解决该问题。图11说明了并联LED驱动器电路。

并联 LED 驱动器

为了提高抗噪声能力,可采用并联LED驱动器。并联LED驱动器的优势如下:

1)在半桥驱动器中改善 CMTI

2)通过封装电容耦合的负载dv / dt ,被耦合至低阻抗(要么导通LED ,要么导通BJT或逻辑门的导通电阻)中。

缺点是效率最低(例如,当LED导通或开启时需要消耗功率)。

图11 并联 LED 驱动器的FOD3182

当 LED 与驱动器开关并联时,将产生电流分流驱动。图11采用开路漏极逻辑门U1,作为驱动器:

外部或自产生的共模和正常模式噪声可以导致操作故障。最小化控制逻辑和功率半导体之间的耦合电容,大大减小了共模噪声瞬态转换为正常模式噪声脉冲。在驱动点采用低的、平衡阻抗来改善抗噪声能力。控制功率MOSFET采用电流隔离驱动器最小化共模的噪声耦合。FOD31xx系列MOSFET驱动器的内部屏蔽最小化驱动器CMTI。采用并联LED驱动器最大化输入网络的CMTI,减少了共模噪声脉冲转换为正常模式LED驱动信号的危险。

如何计算FOD3120功率МOSFET / IGBT栅极驱动光电耦合器的最大开关频率

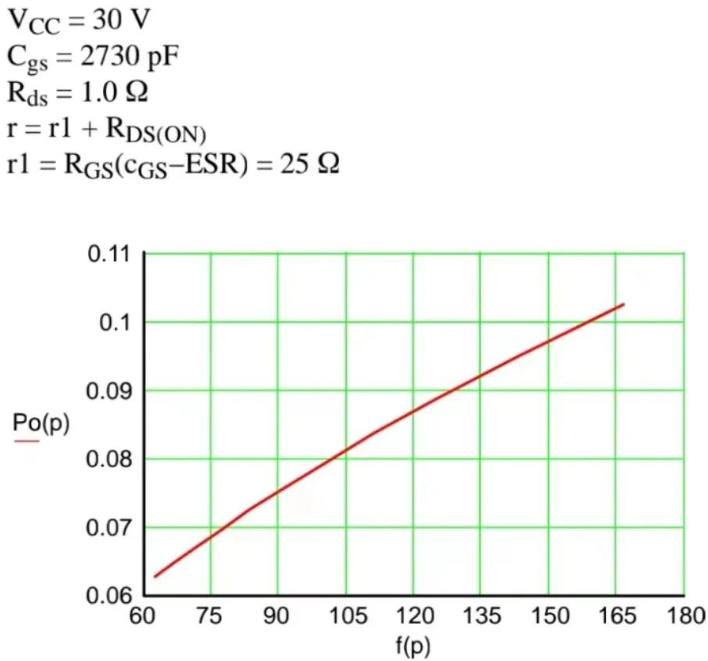

为了计算FOD3120的最大开关频率,采用表1中的变量。

分析

计算最大开关频率的第一个步骤是确定在最大工作日结温125℃和环境温度100C时,FOD3120输出驱动器MOSFET的最大功耗。前一节说明了基于FOD3120稳态热阻,在TA =100℃时,最大功率是210 mW 。

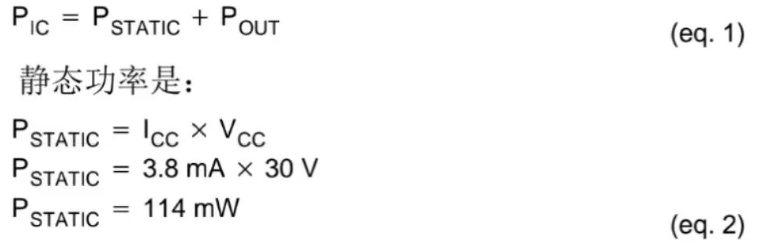

输出IC的最大功率是稳态IC功率与输出功率MOSFET晶体管功耗之和。精确关系如下式(1):

输出晶体管的最大允许功耗POUT,是最大 IC 功率PIC与静态IC 功率PSTATIC的差。

在环境温度100 ℃时,输出晶体管耗散的稳态功率为96 mW 。输出功率耗散在输出 P 沟道和 N 沟道晶体管的漏极至源极的串联电阻 RDS ( ON )上。

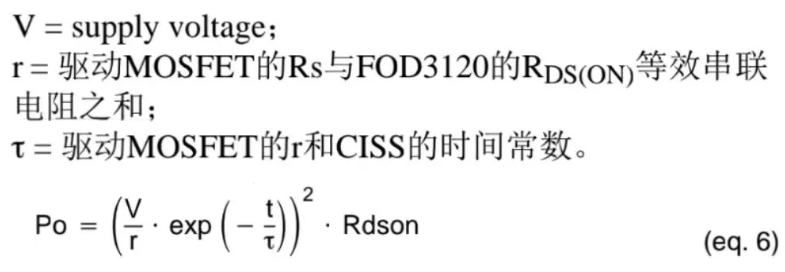

输出功率公式如下:

![]()

图12 FOD3120-MOSFET接口

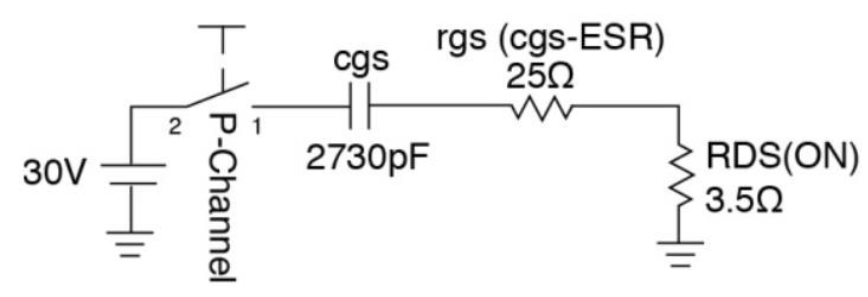

图13 等效电流FOD3120-MOSFET接口

图12显示的是,FOD3120和N沟道功率MOSFET之汇作间的互连。图13提供了用于计算FOD3120输出功率的力器等效电路。P沟道晶体管建模为带有3.5Ω的串联电阻的开关。FQA9N90C_F109的输入建模为串联 RC 电路。电路元件是栅极至源极电容2730 pF 、与25Ω等效力率串联电阻(ESR)串联。

下面将讨论RMS在输出晶体管上的功耗,给出MOSFET栅极充电和放电电流,以及FOD3120晶体管RDS(ON)的电压降。

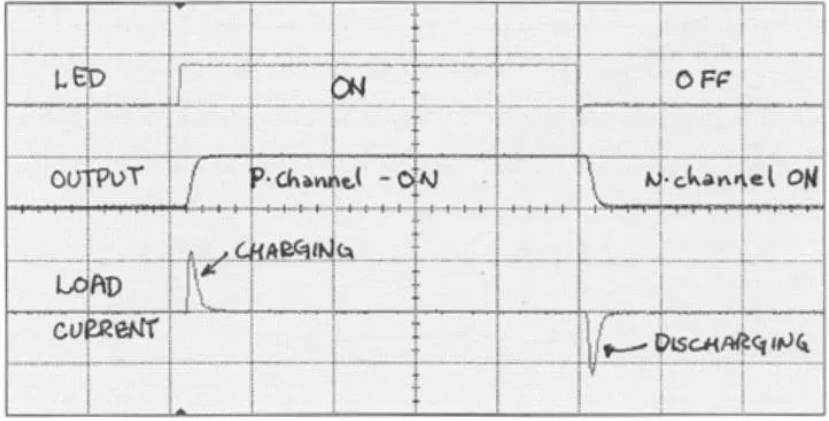

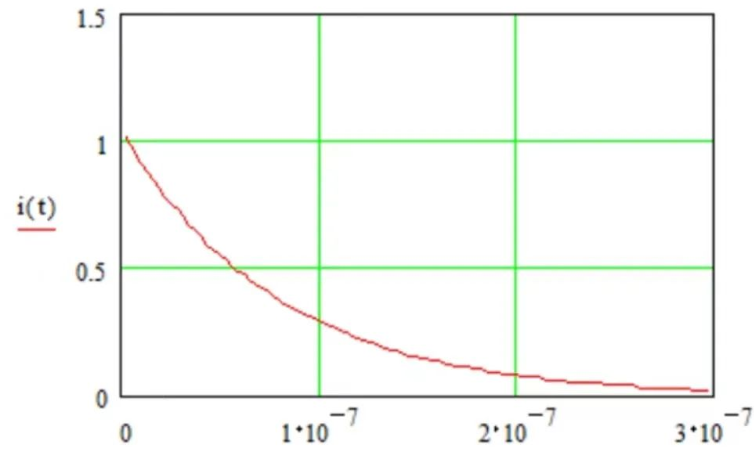

图14 FOD3120输出电流和电压

图14显示的是,当FOD3120驱动功率MOSFET的栅极时,输出电流的波形。再看一下图13,当开关连接至串联电阻RGS、 RDS ( ON)和输入电容 CGS 时,初始充电转换如图所示。当开关打开,电流上升至峰值Vcc / rGS。充电电流呈指数下降由CGS、电阻RGS和RDS(ON)确定。

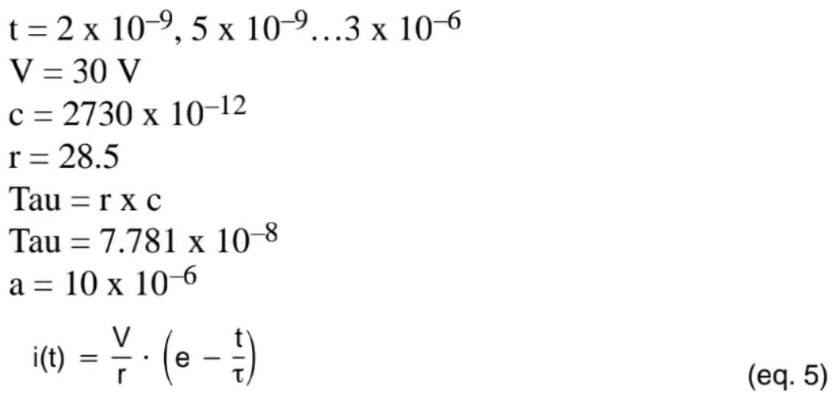

假设:

图15 FOD3120输出电流

FOD3120的MOSFET峰值功耗由峰值电流和指数的延迟时间(t)确定,其中:

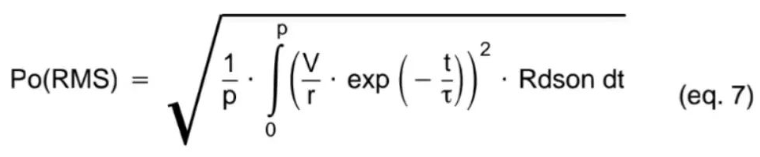

在输出处的结温增加是热阻和输出驱动器的RMS功率产品。在等式(7)中给出计算RMS功率的等式。变量p,是功率脉冲平均期间的时长。图14说明在每个LED转换时,都存在驱动电流脉冲。工作频率定义为1/(2 x p )。该定义通过平衡分析:

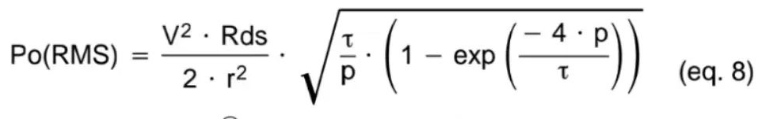

利用等式(8)的初等微积分,求解等式(7), RDS = RDS(ON) 的定积分:

借助数学CADⓇ,利用几何方法求解等式。

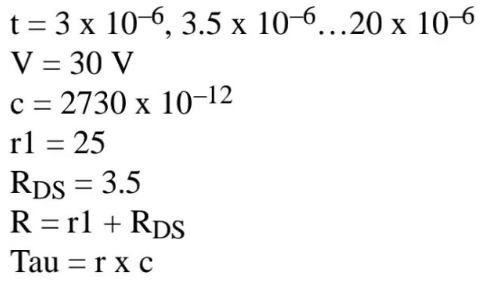

假设:

图16 输出功耗(W)与工作频率(KHZ)

图16表示,在驱动输出功耗96 mW的FQA9N90C_F109时,容许的最大工作频率低于20 kHz 。主要的限制因素是最坏情况下的技术规格﹣输出驱动器的 RDS ( ON )。

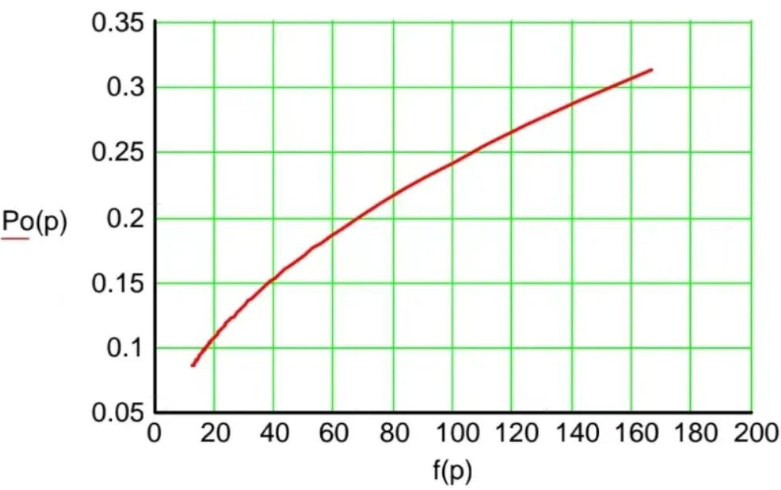

如果部件的最大 RDS ( ON )被指定为:当工作条件 Io图17为1 A 时,其值接近典型值1.0Ω,结果可能如所示。

假设:

图17 输出功耗( W )与工作频率( kHz )

图17说明,如果 RDS(ON) 等于1.0Ω;在100℃和 Vcc =30 V 时驱动FQA9N90C_F109 MOSFET ,开关频率可能为150 kHZ 。

结论

本应用指南重点介绍了隔离门驱动电路的可靠性和性能优化的一些方法。采用通用的公式计算栅极充电传输功率,该功率供应给驱动MOSFET(FQA9N90C_F109)。然而,该分析并没有描述驱动器IC内的功耗。利用等式(8)计算FOD3120的输出功率MOSFET的功耗,是RDS(ON)、 Vcc 、驱动МOSFET的栅极电容和栅极等效串联电阻(ESR)的函数。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。