组合逻辑电路-131页.pptx

相关关键词

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关文章

17个图解数字电路基础知识!!

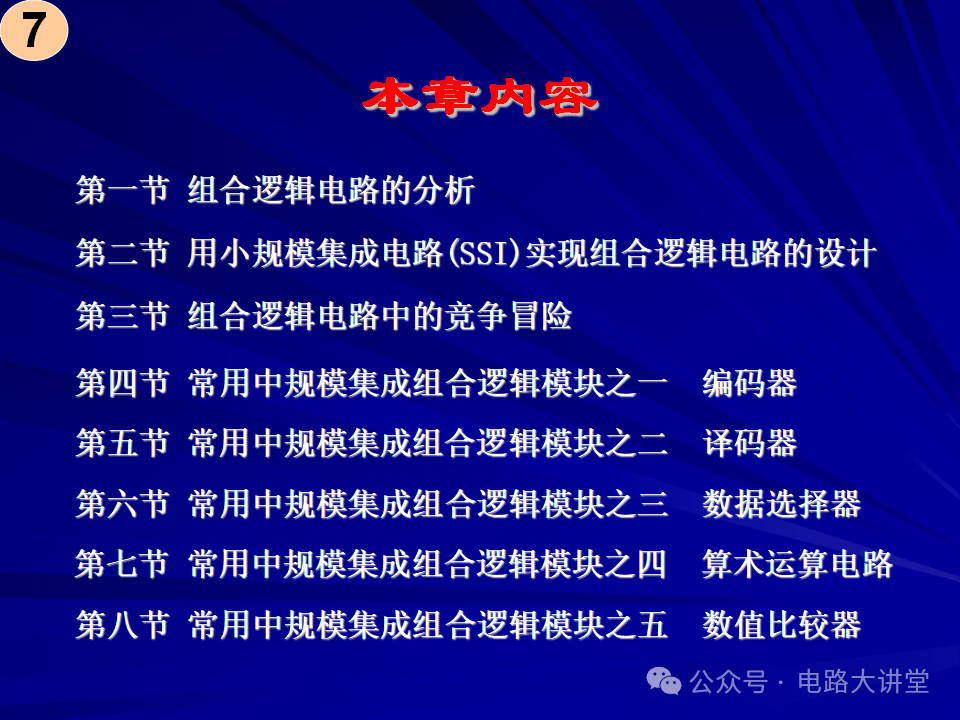

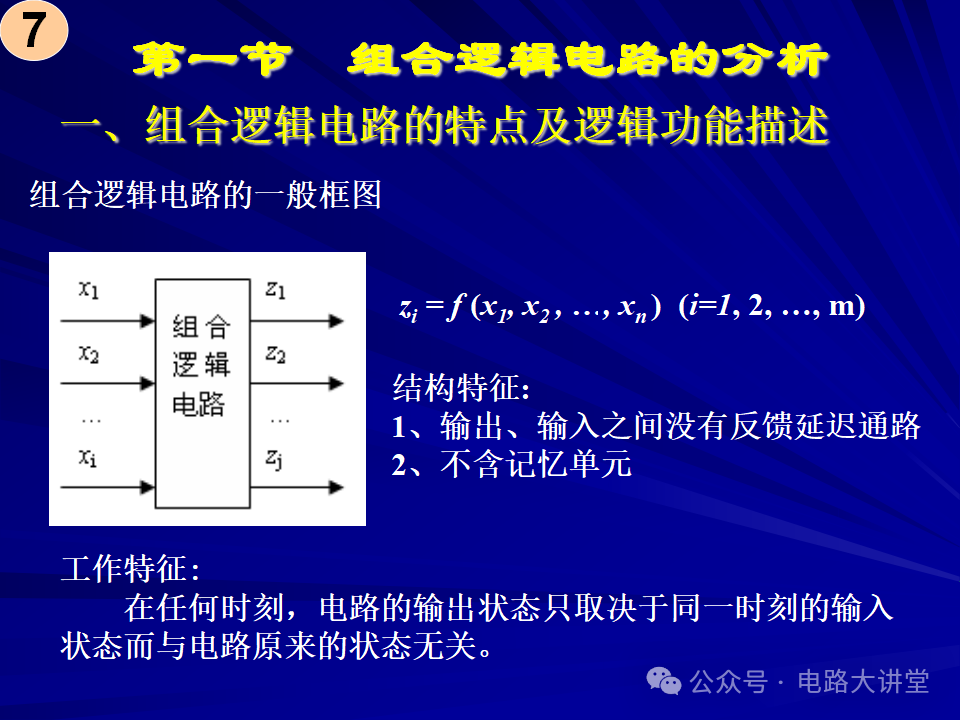

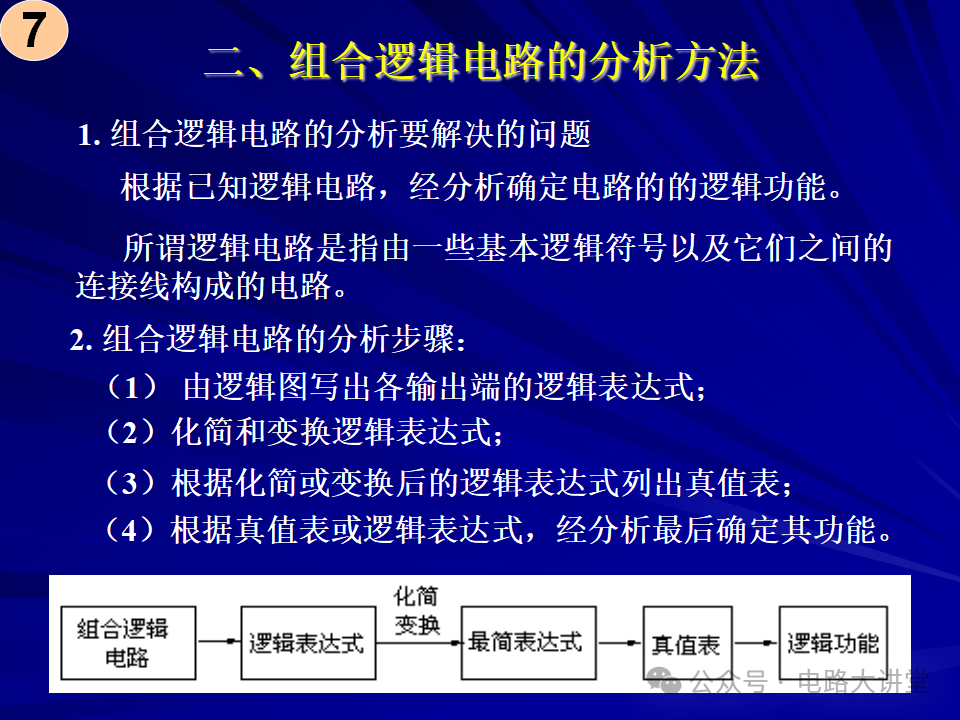

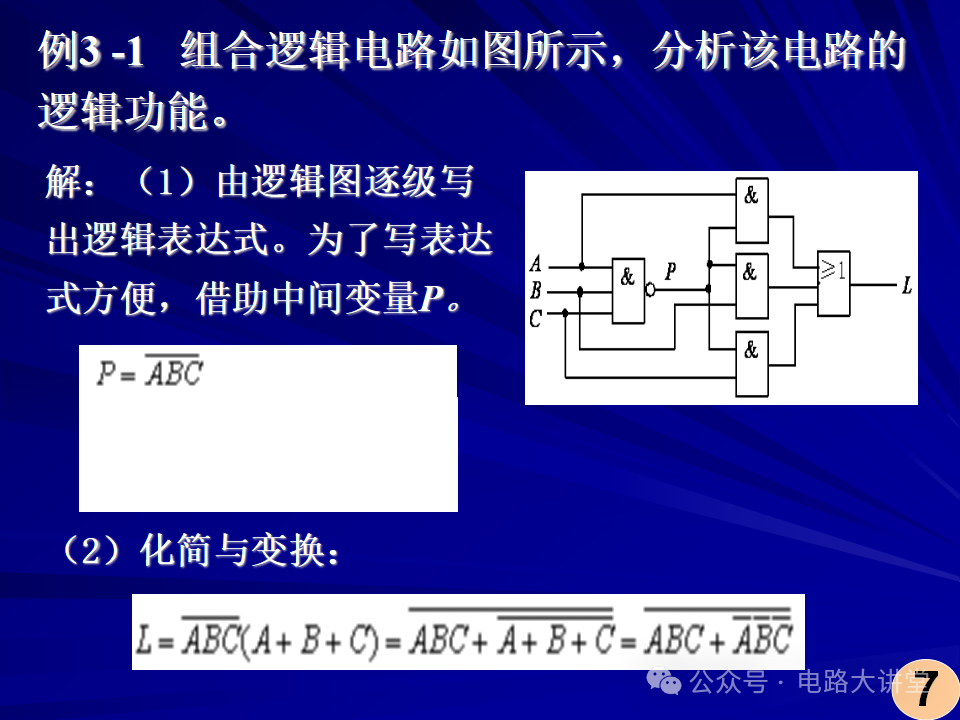

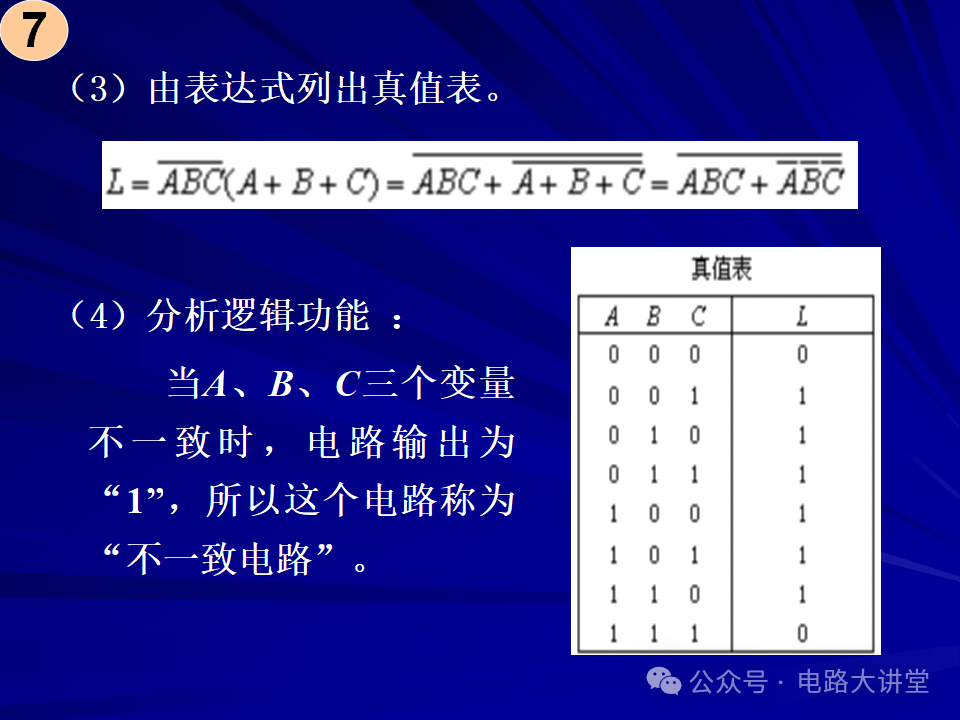

、组合逻辑电路和时序逻辑电路数字电路可以分为组逻辑合电路和时序逻辑电路两种。 (1)组合逻辑电路组合逻辑电路是指输出值仅由输入信号的状态决定的电路...

可创建小型组合与时序逻辑电路的PLU可编程逻辑单元

器之间采用多路复用,如下: 数字逻辑电路分为组合逻辑电路与时序逻辑电路,只有时序逻辑电路需要使用触发器。当使用触发器时,需要外部向PLU_CLKIN提供时钟输入,即使用组合逻辑电路无需外部提供时钟,使用时序逻辑电路...

数字电路中组合逻辑的神奇效应

数字电路中组合逻辑的神奇效应; 在数字电路的世界里,组合逻辑电路就像是一位神奇的魔术师,它能根据输入信号的不同组合,瞬间变幻出各种输出结果。 这种电路...

实验22 4位串行累加器

器是一个具有特殊功能的二进制寄存器,可以存放计算产生的中间结果,省去了计算单元的读取操作,能加快计算单元的速度。串行累加器是由移位寄存器和全加器组成的一个求和电路。由题目给出的要求可以分析组合逻辑电路一是一个全加器电路...

CPLD/FPGA 内部结构与原理

可以看到,LUT具有和逻辑电路相同的功能。实际上,LUT具有更快的执行速度和更大的规模。由于基于LUT的FPGA具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,所以...

详解CPLD/FPGA架构与原理

上,LUT具有更快的执行速度和更大的规模。 由于基于LUT的FPGA具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,所以适用于高速、高密度的高端数字逻辑电路...

FPGA约束、时序分析的概念介绍

知道TINPUT,TINPUT为输入端的组合逻辑、网线和PAD的延迟之和,PAD的延时也根据器件型号也有典型值可选,但是到达输入端的组合逻辑电路和网线的延时就比较难以确定了,只能...

安森美半导体推出两款新的时钟分配集成电路(IC)

用2.5伏(V)及3.3 V供电电压工作,其差分输入集成了通过VT引脚连接的内部50 Ω端接电阻。此功能使这器件能够接受多种逻辑电平标准,包括低压正射极耦合逻辑(LVPECL)、电流模式逻辑(CML)及低...