如何快速实现“QFN封装仿真”?

前言

QFN是一种焊盘尺寸小、封装体积小、以塑封材料组成的表面贴装芯片封装技术。由于其底部中央的一大块裸露焊盘被焊接到PCB的散热焊盘上,使得QFN具有极佳的电热性能。另外,在中央焊盘的封装外围有实现电气连接的导电焊盘,这种封装特别适合任何一个对尺寸、成本和性能都有要求的应用场景,从而被市场上广泛使用。随着目前5G应用的频率逐渐升高,QFN封装中Wirebond结构对电路性能的影响也越来越明显,因此需要借助电磁场仿真技术提前对QFN封装的电性能进行预判。

本文介绍了众多5G基站、移动终端公司正在采用的QFN封装仿真流程,涉及到芯和半导体的Hermes 3D工具。Hermes 3D非常擅长对芯片封装和PCB进行信号完整性分析,评估信号通路中阻抗不连续性结构对通道中信号完整性带来的影响,它支持市面上所有封装和PCB设计文件格式的导入,并利用接近业界黄金标准的FEM3D求解器实现S参数的快速提取和分析,其高效的建模流程和精准的仿真引擎能极大地提高工程师评估封装性能指标优化的效率。

QFN封装三维建模和仿真流程

- 模型导入

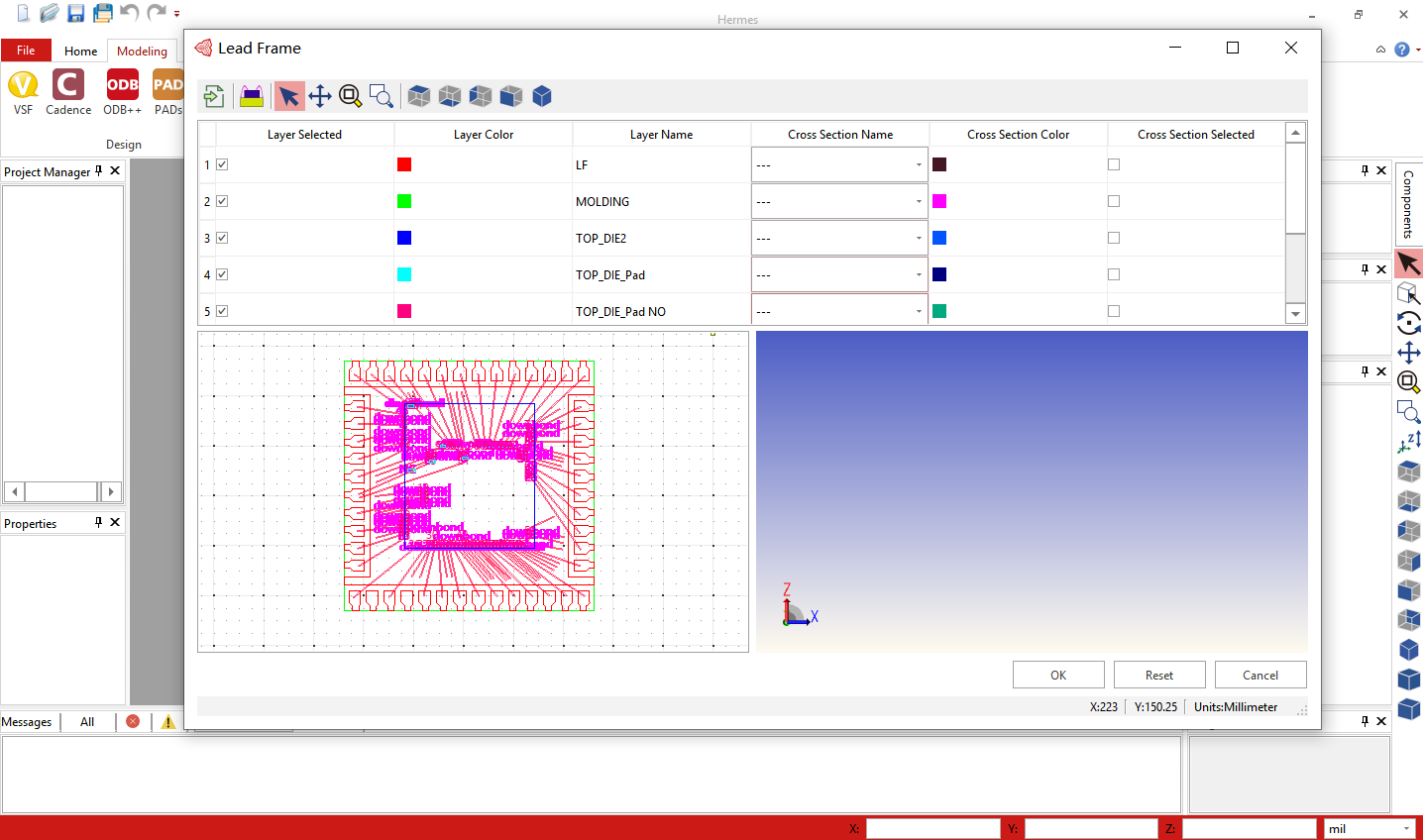

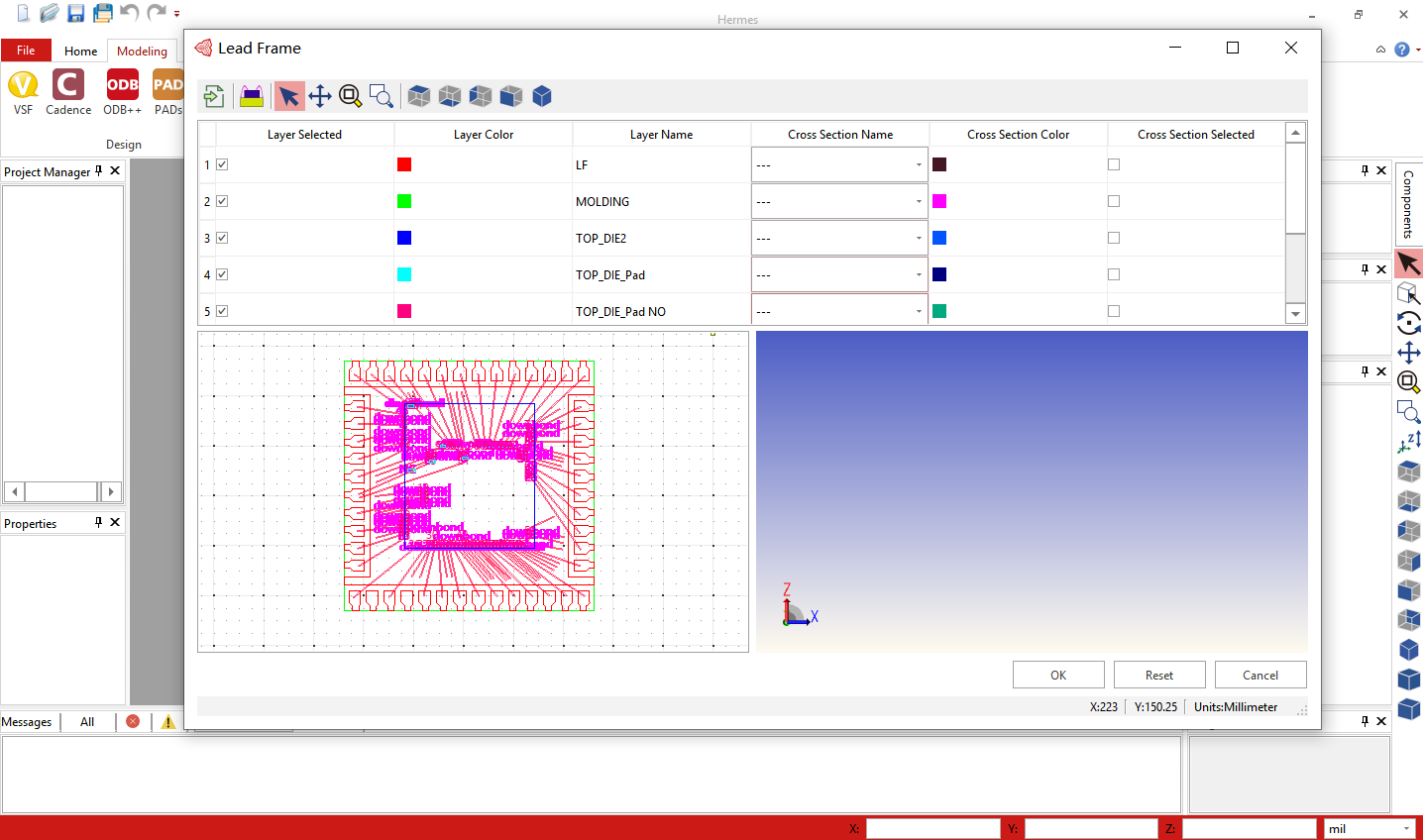

打开Hermes 3D,在Modeling>Design中选择Lead Frame。导入dxf的设计格式文件后进入到Lead Frame配置界面,如图1所示。

前言

QFN是一种焊盘尺寸小、封装体积小、以塑封材料组成的表面贴装芯片封装技术。由于其底部中央的一大块裸露焊盘被焊接到PCB的散热焊盘上,使得QFN具有极佳的电热性能。另外,在中央焊盘的封装外围有实现电气连接的导电焊盘,这种封装特别适合任何一个对尺寸、成本和性能都有要求的应用场景,从而被市场上广泛使用。随着目前5G应用的频率逐渐升高,QFN封装中Wirebond结构对电路性能的影响也越来越明显,因此需要借助电磁场仿真技术提前对QFN封装的电性能进行预判。

本文介绍了众多5G基站、移动终端公司正在采用的QFN封装仿真流程,涉及到芯和半导体的Hermes 3D工具。Hermes 3D非常擅长对芯片封装和PCB进行信号完整性分析,评估信号通路中阻抗不连续性结构对通道中信号完整性带来的影响,它支持市面上所有封装和PCB设计文件格式的导入,并利用接近业界黄金标准的FEM3D求解器实现S参数的快速提取和分析,其高效的建模流程和精准的仿真引擎能极大地提高工程师评估封装性能指标优化的效率。

QFN封装三维建模和仿真流程

- 模型导入

打开Hermes 3D,在Modeling>Design中选择Lead Frame。导入dxf的设计格式文件后进入到Lead Frame配置界面,如图1所示。

图1:Lead Frame配置界面

- Cross Section设置

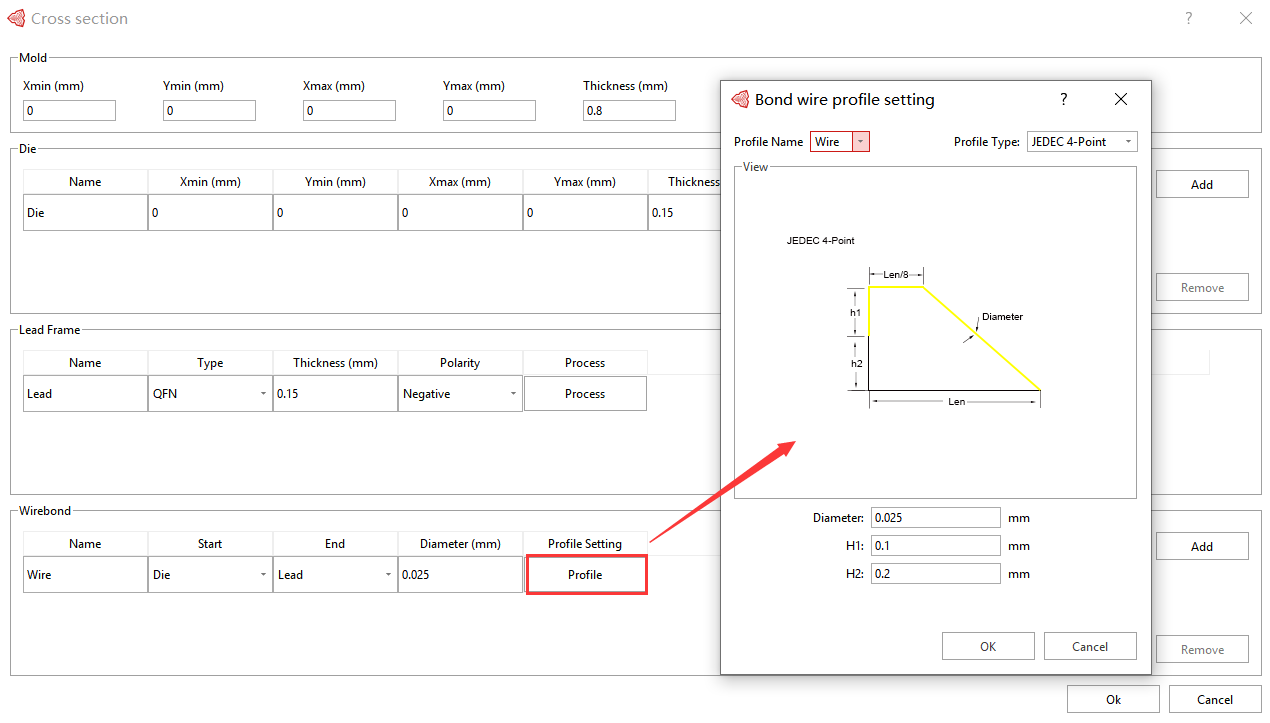

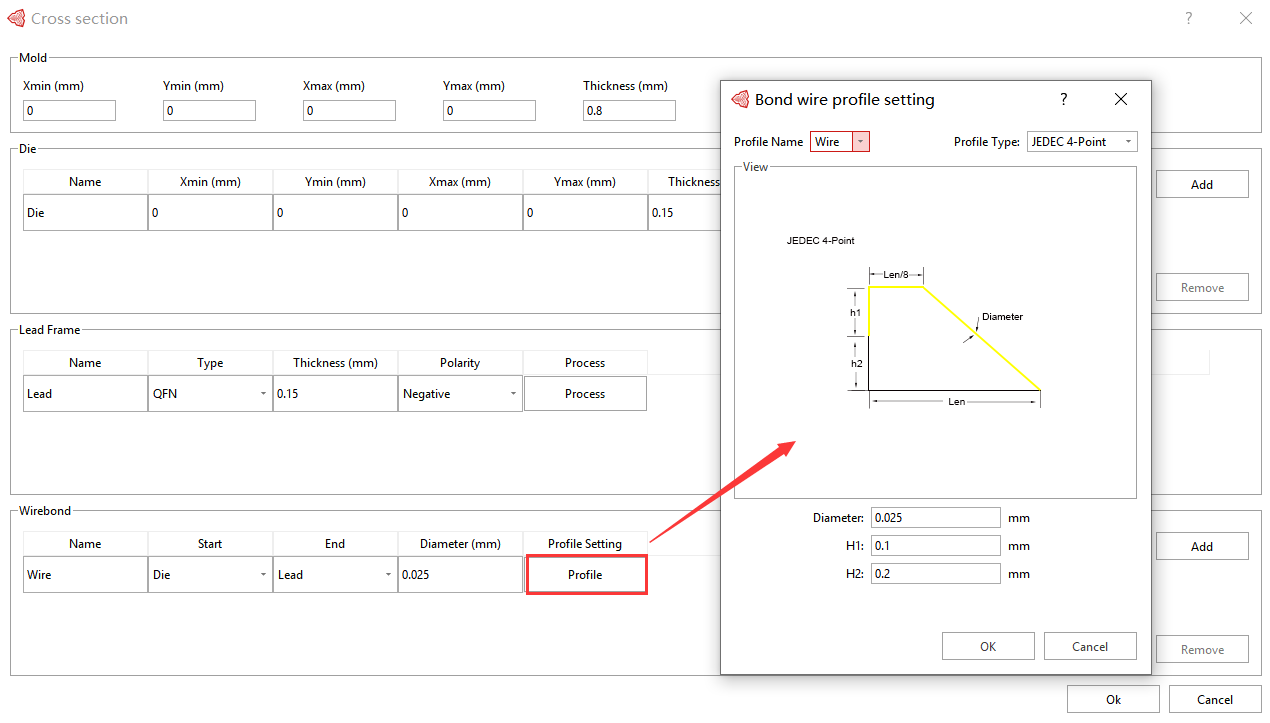

在Lead Frame界面中点击Cross section图标,可以进入到Cross section设置界面。在此设置页面中可以依次对Mold、Die、Lead Frame以及Wirebond结构设定厚度材料等信息,如图2所示。

图2:Cross Section设置

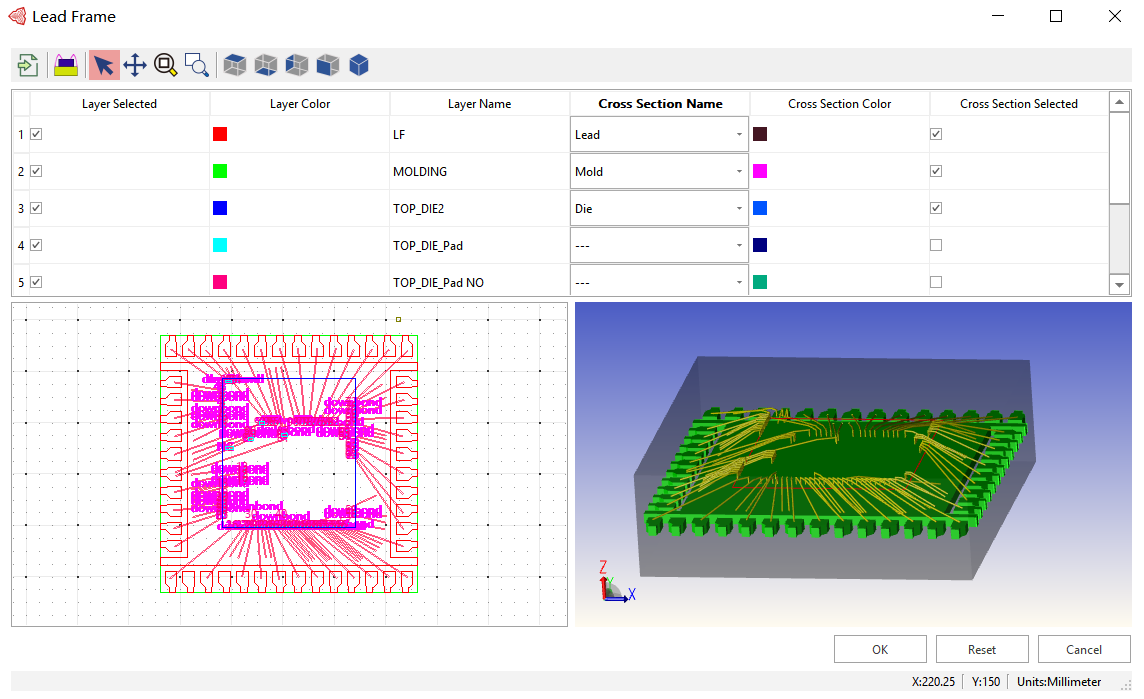

- 建立各层对应关系

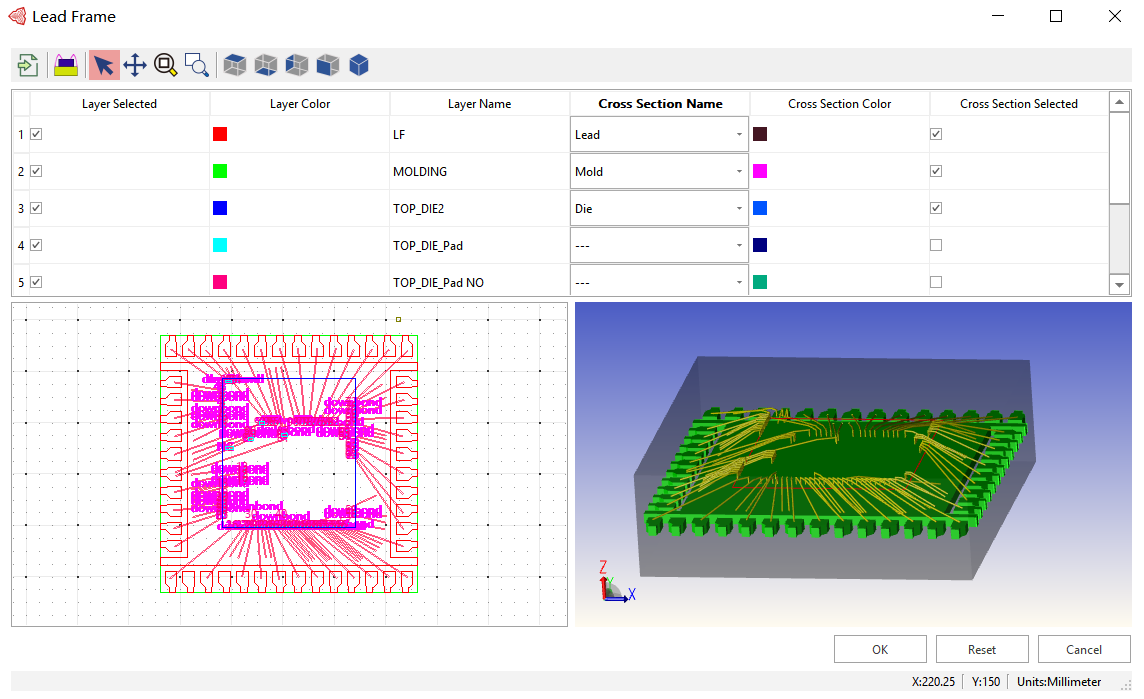

在Cross Section Name栏完成和DXF设计文件中Layer Name的对应层关系,选择对应的Lead Frame结构名称,就可以完成DXF中各个元素的建模。在图3中,从右下角生成的3D结构示意图可以检查生成的模型是否准确无误。

图3:完成QFN封装3维建模

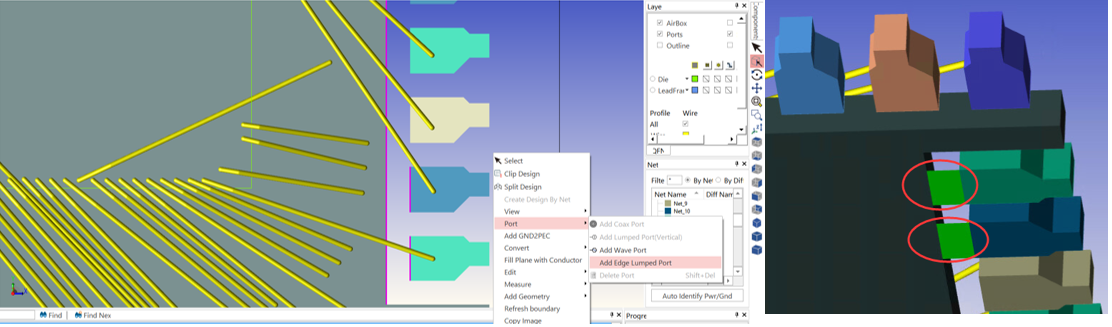

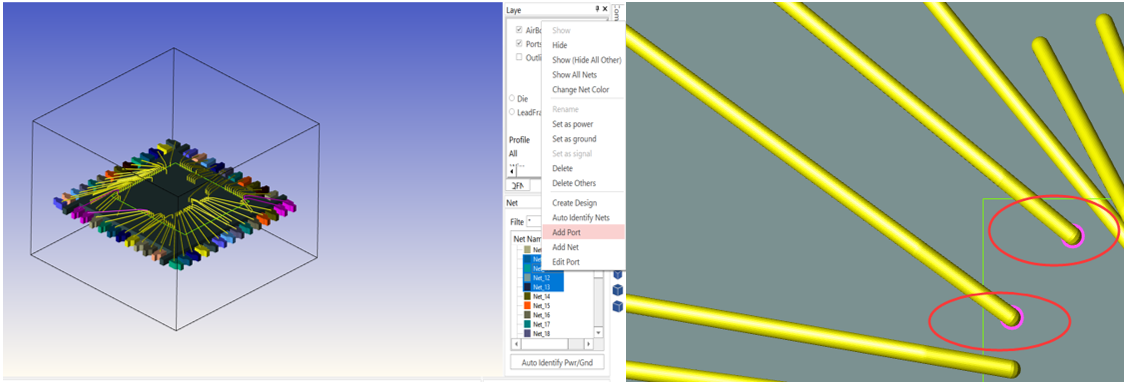

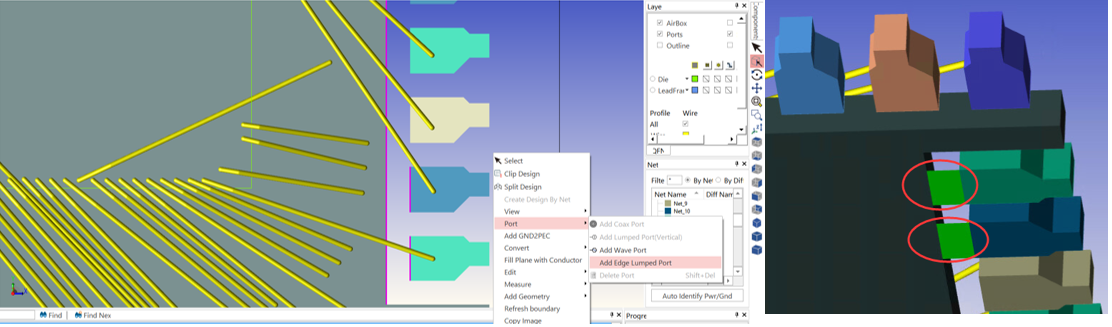

- 添加Port

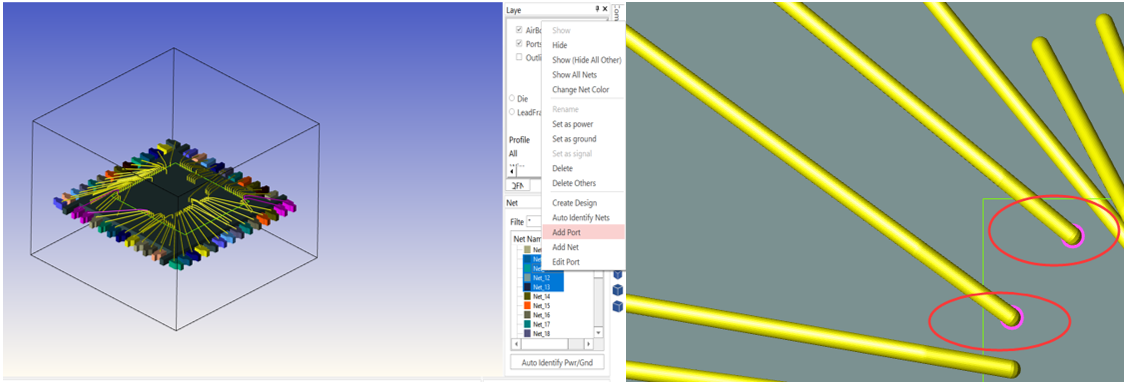

Hermes3D支持用户添加多种类型的port,例如在芯片端添加Annular port;在引线框架上添加lumped port。在右侧nets列表中选择要仿真的网络,右键选择Add Port,弹出Generate Ports窗口,可以在芯片端选择添加Annular port类型,如图4所示。用edge选择模式,在引线框架上选择要创建的信号和参考地的边,点击右键,选择Port->Add Edge Lumped Port;添加好的lumped port如图5中绿色的平面所示。

图4:添加Annular port

图5:添加Lumped port

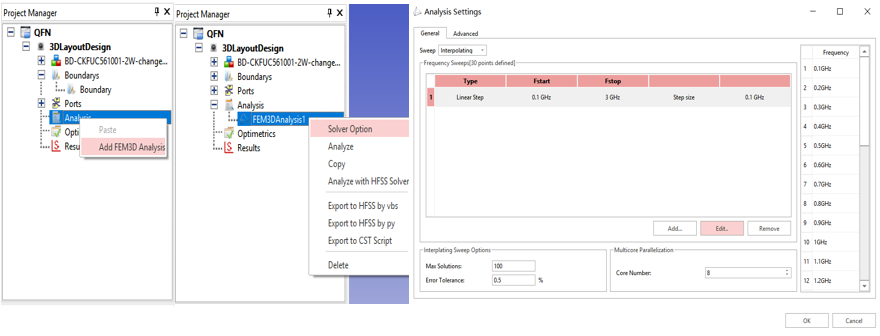

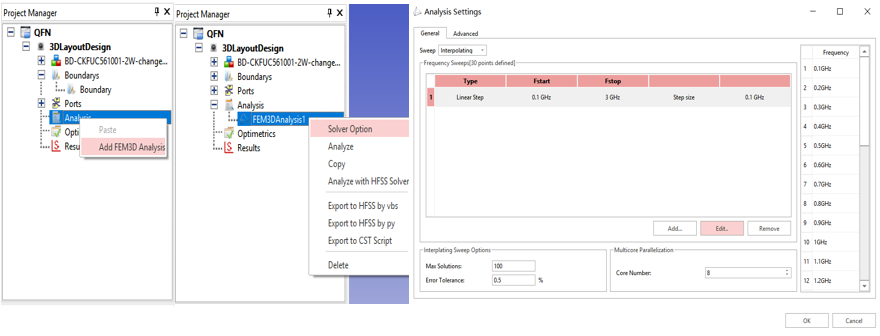

- 添加FEM3D 仿真设置

在工程树形菜单Analysis中右键选择Add FEM3D Analysis,点击Solver Option,可按照如下方式进行求解扫频设置,如图6所示。

图6:仿真设置

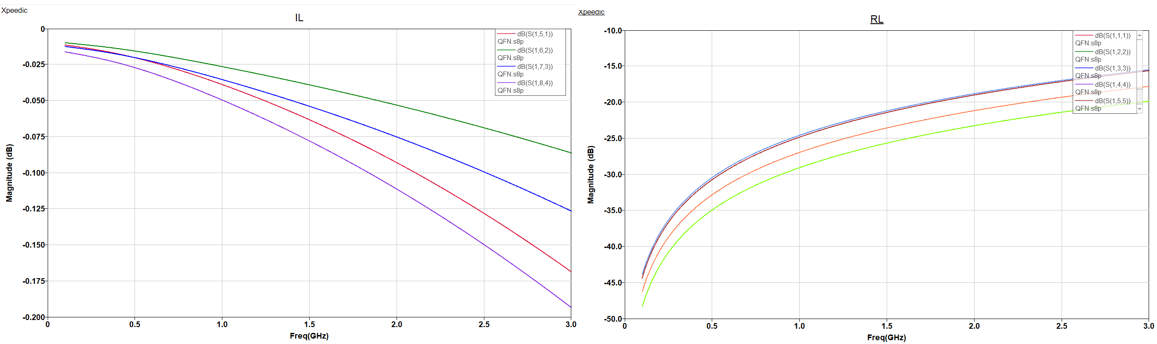

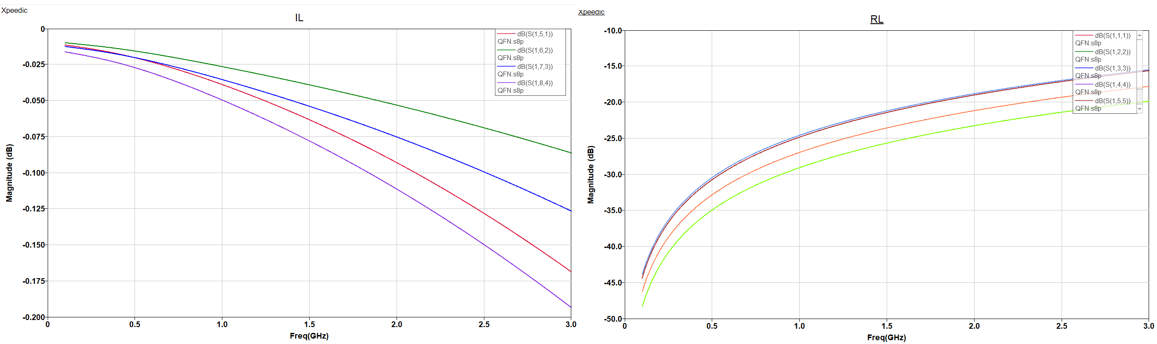

- 查看仿真结果

待仿真结束之后,结果以树型结构的形式呈现在工程树Results菜单下方,并且可以使用SnpExpert工具打开仿真结果,进行查看,如图7所示。

图7:查看仿真结果

总结

由于产品小型化的要求,后摩尔时代,越来越多的芯片企业开始重视封装形式的研发。本文介绍众多5G基站、移动终端企业所采用的QFN封装仿真流程,涉及到芯和半导体的Hermes3D软件。Hermes3D专注于评估在IC和封装以及PCB的互连中的寄生带来的相互作用,其高效的建模流程和精准的仿真引擎能极大地提高工程师评估封装性能指标优化的效率。

芯和半导体EDA介绍

芯和半导体成立于2010年,是国内唯一提供“半导体全产业链仿真EDA解决方案”的供应商。芯和半导体EDA是新一代智能电子产品中设计高频/高速电子组件的首选工具,它包括了三大产品线:

- 芯片设计仿真产品线为晶圆厂提供了精准的PDK设计解决方案, 为芯片设计公司提供了片上高频寄生参数提取与建模的解决方案;

- 先进封装设计仿真产品线为传统型封装和先进封装提供了高速高频电磁场仿真的解决方案;

- 高速系统设计仿真产品线为PCB板、组件、系统的互连结构提供了快速建模与无源参数抽取的仿真平台,解决了高速高频系统中的信号、电源完整性问题。

芯和半导体EDA的强大功能基于:自主知识产权的多种尖端电磁场和电路仿真求解技术、繁荣的晶圆厂和合作伙伴生态圈(芯和半导体EDA在所有主流晶圆厂的先进工艺节点和先进封装上得到了不断验证)、以及支持基于云平台的高性能分布式计算技术,在5G、智能手机、物联网、汽车电子和数据中心等领域已得到广泛应用。

关于芯和半导体

芯和半导体是EDA软件、集成无源器件IPD和系统级封装领域的领先供应商。公司致力于为半导体芯片设计公司和系统厂商提供差异化的软件产品和芯片小型化解决方案,包括射频IC设计、模拟混合信号设计、系统级封装设计和高速数字系统设计等。这些产品和方案在5G、智能手机、物联网、人工智能和数据中心等领域得到广泛应用。

芯和半导体凭借以客户需求驱动发展的理念,赢得了众多客户的青睐。随着公司自有知识产权的不断开发,芯和半导体已经成为中国集成电路自动化软件技术和微电子技术行业的标杆企业。

芯和半导体前身为芯禾科技,创建于2010年,企业总部位于上海浦东张江,并在美国硅谷、中国北京、深圳、苏州、成都、西安设有销售和技术支持中心。如欲了解更多详情,敬请访问 www.xpeedic.cn。

责编:Johnson Zhang

图1:Lead Frame配置界面

- Cross Section设置

在Lead Frame界面中点击Cross section图标,可以进入到Cross section设置界面。在此设置页面中可以依次对Mold、Die、Lead Frame以及Wirebond结构设定厚度材料等信息,如图2所示。

图2:Cross Section设置

- 建立各层对应关系

在Cross Section Name栏完成和DXF设计文件中Layer Name的对应层关系,选择对应的Lead Frame结构名称,就可以完成DXF中各个元素的建模。在图3中,从右下角生成的3D结构示意图可以检查生成的模型是否准确无误。

图3:完成QFN封装3维建模

- 添加Port

Hermes3D支持用户添加多种类型的port,例如在芯片端添加Annular port;在引线框架上添加lumped port。在右侧nets列表中选择要仿真的网络,右键选择Add Port,弹出Generate Ports窗口,可以在芯片端选择添加Annular port类型,如图4所示。用edge选择模式,在引线框架上选择要创建的信号和参考地的边,点击右键,选择Port->Add Edge Lumped Port;添加好的lumped port如图5中绿色的平面所示。

图4:添加Annular port

图5:添加Lumped port

- 添加FEM3D 仿真设置

在工程树形菜单Analysis中右键选择Add FEM3D Analysis,点击Solver Option,可按照如下方式进行求解扫频设置,如图6所示。

图6:仿真设置

- 查看仿真结果

待仿真结束之后,结果以树型结构的形式呈现在工程树Results菜单下方,并且可以使用SnpExpert工具打开仿真结果,进行查看,如图7所示。

图7:查看仿真结果

总结

由于产品小型化的要求,后摩尔时代,越来越多的芯片企业开始重视封装形式的研发。本文介绍众多5G基站、移动终端企业所采用的QFN封装仿真流程,涉及到芯和半导体的Hermes3D软件。Hermes3D专注于评估在IC和封装以及PCB的互连中的寄生带来的相互作用,其高效的建模流程和精准的仿真引擎能极大地提高工程师评估封装性能指标优化的效率。

芯和半导体EDA介绍

芯和半导体成立于2010年,是国内唯一提供“半导体全产业链仿真EDA解决方案”的供应商。芯和半导体EDA是新一代智能电子产品中设计高频/高速电子组件的首选工具,它包括了三大产品线:

- 芯片设计仿真产品线为晶圆厂提供了精准的PDK设计解决方案, 为芯片设计公司提供了片上高频寄生参数提取与建模的解决方案;

- 先进封装设计仿真产品线为传统型封装和先进封装提供了高速高频电磁场仿真的解决方案;

- 高速系统设计仿真产品线为PCB板、组件、系统的互连结构提供了快速建模与无源参数抽取的仿真平台,解决了高速高频系统中的信号、电源完整性问题。

芯和半导体EDA的强大功能基于:自主知识产权的多种尖端电磁场和电路仿真求解技术、繁荣的晶圆厂和合作伙伴生态圈(芯和半导体EDA在所有主流晶圆厂的先进工艺节点和先进封装上得到了不断验证)、以及支持基于云平台的高性能分布式计算技术,在5G、智能手机、物联网、汽车电子和数据中心等领域已得到广泛应用。

关于芯和半导体

芯和半导体是EDA软件、集成无源器件IPD和系统级封装领域的领先供应商。公司致力于为半导体芯片设计公司和系统厂商提供差异化的软件产品和芯片小型化解决方案,包括射频IC设计、模拟混合信号设计、系统级封装设计和高速数字系统设计等。这些产品和方案在5G、智能手机、物联网、人工智能和数据中心等领域得到广泛应用。

芯和半导体凭借以客户需求驱动发展的理念,赢得了众多客户的青睐。随着公司自有知识产权的不断开发,芯和半导体已经成为中国集成电路自动化软件技术和微电子技术行业的标杆企业。

芯和半导体前身为芯禾科技,创建于2010年,企业总部位于上海浦东张江,并在美国硅谷、中国北京、深圳、苏州、成都、西安设有销售和技术支持中心。如欲了解更多详情,敬请访问 www.xpeedic.cn。

责编:Johnson Zhang

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。