ATX-3000线束测试仪的导通测试和电阻测试

1.导通测试

导通测试是线束中必须相连接的点是否准确的连接。通常人们用的方法是线路的一端,施以一定额的电流/' target='_blank' class='arckwlink_none'>电流,并在另一端探查是否有相对应的电流流出,而获知该路径是否接通,再进一步量测两端的电压差,计算该导线的电阻值,此要对线束逐点进行点对点的测试。

在多线束导通测试的过程中,如果有错误发生,不论是断线、短路或接线错误,通常最大的困难就是找到真正的错误,是断线未接,还是连接错误,还是线间短路等等。传统上简单的线束测试器中,通常是一对一的导通测试及一对一的绝缘测试。这种方法对于复杂的线束拓扑结构,经常无法检测涵盖所有错误,即使发现有错误,仍不能很快的掌握实际的状况。

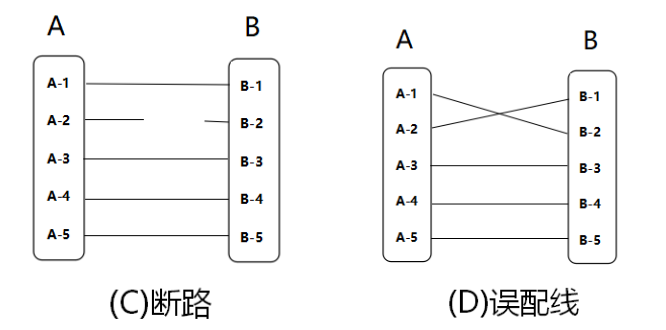

线束的正常连接及常见失效如下图所示:

线束导通测试示意图

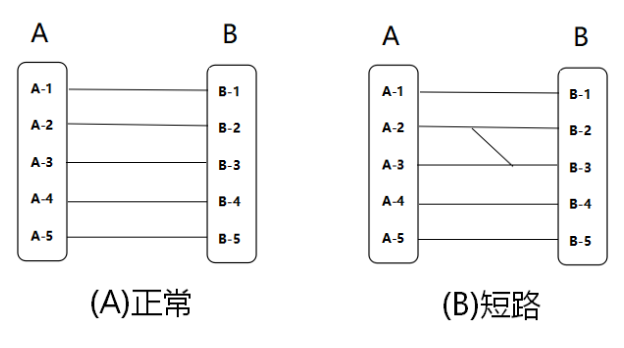

ATX-3000线束测试仪导通测试原理:给需要测试的线束施加一定电流,测量线缆端点处的电压值和电流值,由测试仪内部对测量结果使用欧姆定律进行换算,得出准确的电阻值。用此电阻值与用户设定的电阻值进行比较,判定是否有质量隐患。导通测试原理图如图:

线束测试仪导通测试原理图

该导通测试功能通过快速自学习保存一个正确标准,便可得出未知电缆线束连接关系,省去手工输入接线关系的不便和繁琐工序,判断连接关系是否正确,是否有短路、断路、误配线等质量隐患。

本方案中,线束测试仪主机选用高性能DSP和FPGA核心芯片,FPGA的工作频率由FPGA芯片以及设计决定系统时钟频率较高,CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,确保导通速度不低于0.5S/点,其中具体环节测试时间如下表所示。

2.电阻测试

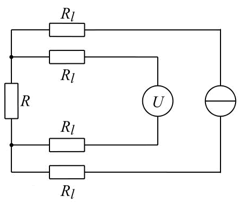

线束测试仪ATX-3000电阻测试基于开尔文电桥的四线隔离法进行测试。四线测试法技术是被高精度电路测量系统所采用的一种电阻测试方法,四线测试方法是利用Kelvin电桥测试法进行电阻测量,并采用24位ADC保证在低电流的情况下满足微电阻的精确度。当被测电阻阻值较小时,利用这种测试方法可获得非常精确的测试结果。此测试法是利用直接从被测电阻两端读取电压的方法,可以消除测试导线带来的误差累积,尤其是在测长距离和多转接终端电阻阻值时,可补偿线束测试仪内部和线间电阻误差。

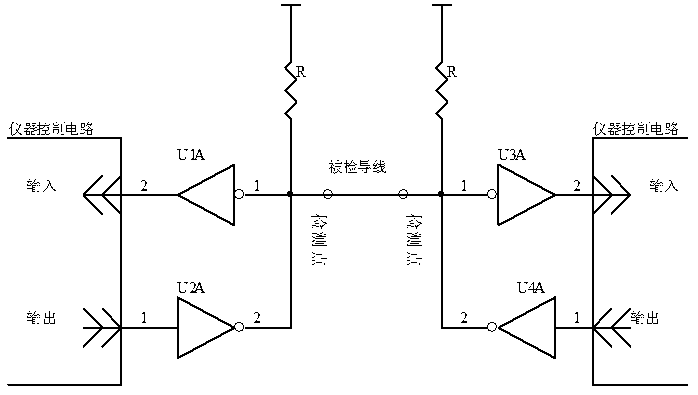

Kelvin电桥测试法原理图

两线制测电阻会引入线上电阻,如图所示:

四线制测电阻电压表的电流保持在最低限度,避免了导线的电阻所引起的误差,提高电阻测量精度,如图所示:

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。