美国积极部署AISS项目,拟将安全性嵌入IC设计过程

美国国防部高等研究计划署(DARPA)正在寻求将安全功能自动导入IC设计流程的方法,让芯片架构师能在进行经济与安全性权衡之同时,也能在整个设备生命周期中确保其安全性。随着美、中“科技冷战”升温,半导体技术可说是这场战役中的一个关键点,因此上述的芯片设计技术变革,代表着美国保卫其电子供应链安全性持续付出的努力之一。

DARPA近日宣布,分别由EDA供货商Synopsys与Northrop Grumman所领导的两支团队,正加速推进在一年前展开的“安全芯片自动化实现”(Automatic Implementation of Secure Silicon,AISS)项目。这两支团队将开发导入用于“安全引擎”的Arm架构芯片,该安全引擎可用来抵御针对芯片的攻击以及逆向工程。此外还有一个可升级的平台将做为基础设施,让规划人员能在整个芯片生命周期中,管理这些经过安全强化的芯片。

AISS专案于2019年4月启动,目标是在保障IC设计流程与芯片供应链安全的前提下,达到安全性与经济考虑的平衡。

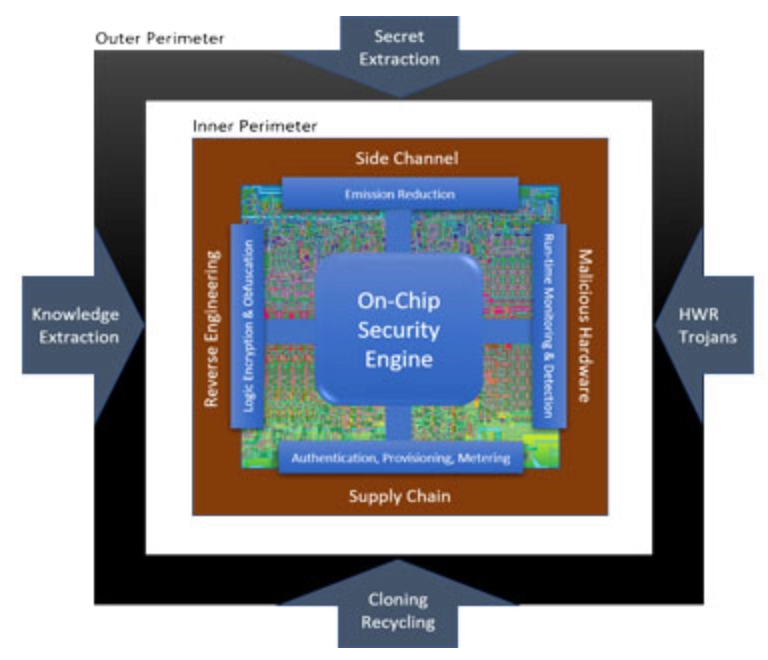

导入安全引擎的芯片架构。(图片来源:DARPA)

由Synopsys率领的团队成员除了Arm之外,还有航天业巨擘波音(Boeing),以及美国佛罗里达大学旗下(University of Florida)的网络安全研究所、德州农工大学(Texas A&M University)、加州大学圣地亚哥分校(University of California at San Diego);英国的嵌入式分析IP供货商UltraSoC也是其中一员。Northrop Grumman所率领的团队成员则包括IBM、美国阿肯色大学(University of Arkansas)以及佛罗里达大学。

该项目将分为两个阶段,第一阶段是开发相互竞争的“安全引擎”方案,以弥补关键芯片的安全弱点如旁路攻击(side channel attack)、硬件木马(hardware Trojans)、逆向工程,以及供应链漏洞等等。旁路攻击手法包括追踪设备功耗以做为窃取密钥的手段。

在第二个阶段,Synopsys的团队将寻求利用EDA工具把安全引擎导入SoC平台的方法,包括利用Arm、Synopsys与UltraSoC的商用IP,开发结合“安全意识”(security-aware)的EDA工具。然后芯片设计工程师可透过所开发的EDA工具,指定芯片在功耗、面积、速度与安全性方面的关键约束,该工具就会根据应用目标自动生成优化的实作。

“AISS项目的终极目标,是加速从芯片架构到完成安全强化(RTL)的时程,从一年缩短到一周,而且大幅降低其成本;”DARPA的AISS项目经理Serge Leef表示,项目的另一个目标是将“可扩展防御机制导入芯片设计”的流程自动化,以捍卫整个半导体供应链的安全。

除了以上项目,为了保障美国芯片供应链的安全,美国国防部的其他相关研发计划包括利用数字双胞胎(digital twin)验证单个设备或一批芯片的完整性。

原文发布于ESM姊妹网站EE Times

(参考原文:,By George Leopold 编译:Judith Cheng 责编:Elaine Lin)

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。