数字电路和模拟电路中的8种触发器有什么不同?

来源: 电路一点通

微信公众号资讯

掌握锁存器原理及应用

-

基本SR锁存器

-

钟控SR锁存器

-

钟控D锁存器

-

钟控D锁存器的动态参数

掌握 触发器 原理及应用

-

主从触发器

-

维持阻塞触发器

-

其它功能的触发器

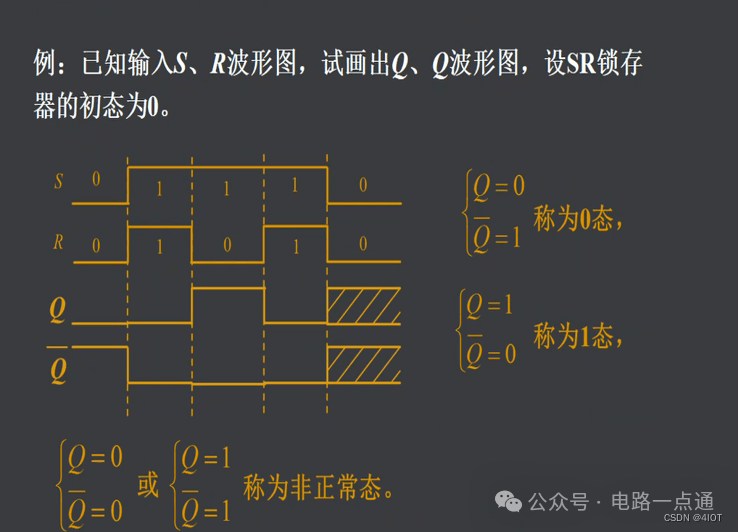

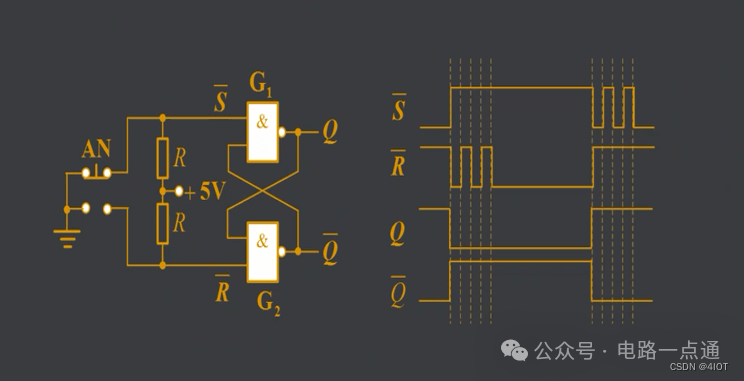

一、基本SR锁存器

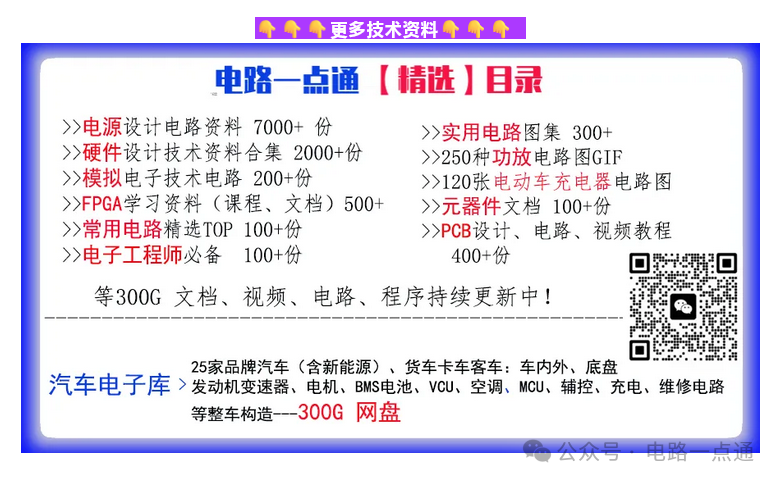

1、双稳态电路(Bistate Elements)

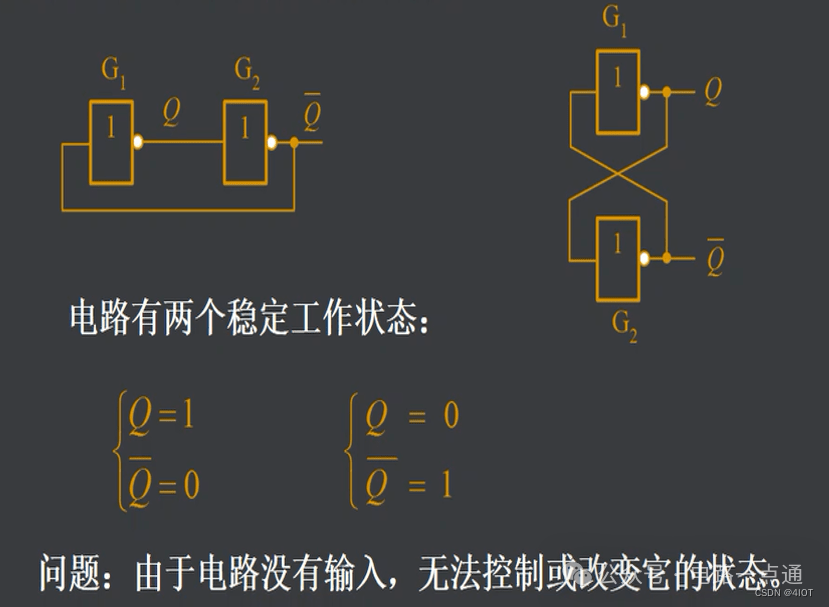

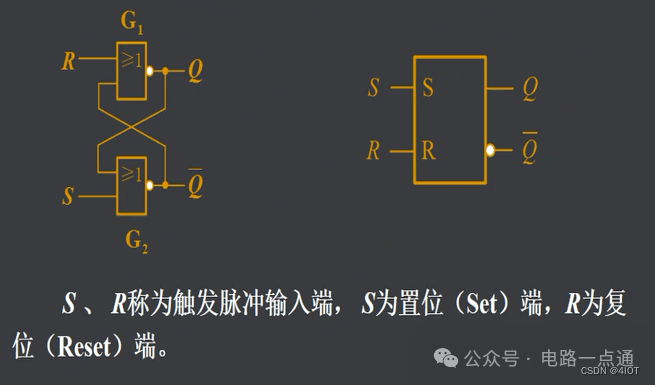

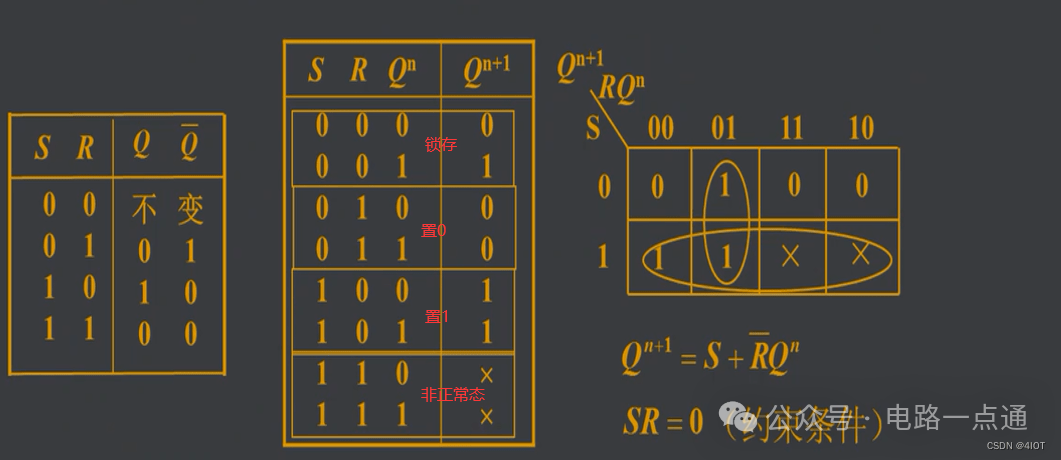

2、由或非门构成的基本SR锁存器

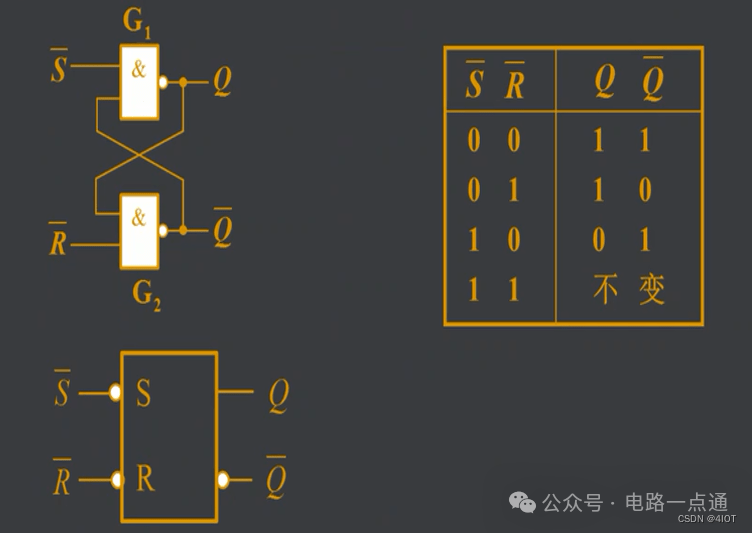

3、由与非门构成的基本SR锁存器

4.锁存器的特性表和特性方程

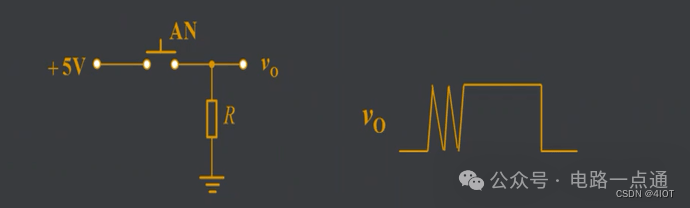

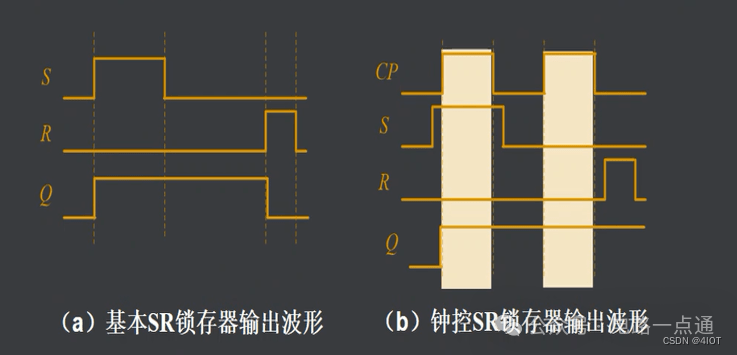

5、基本SR锁存器的应用

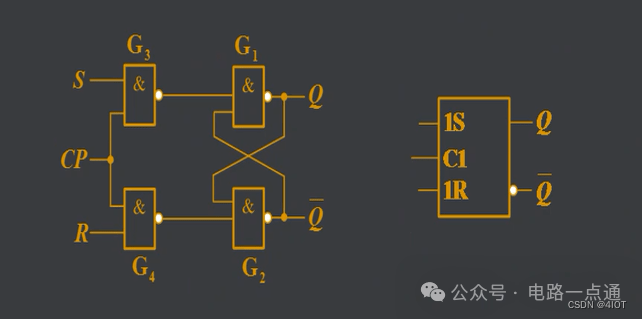

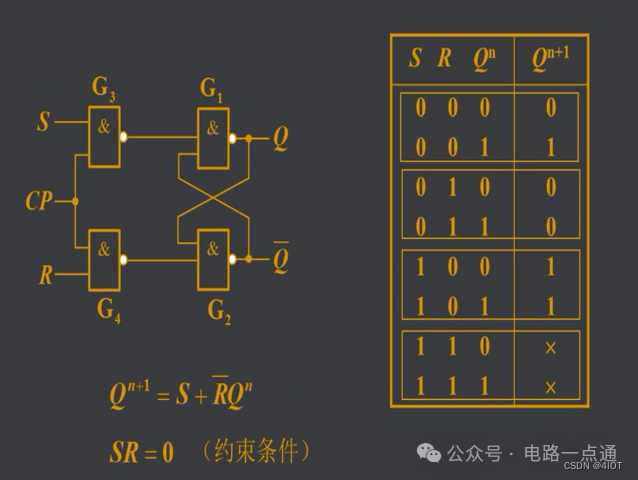

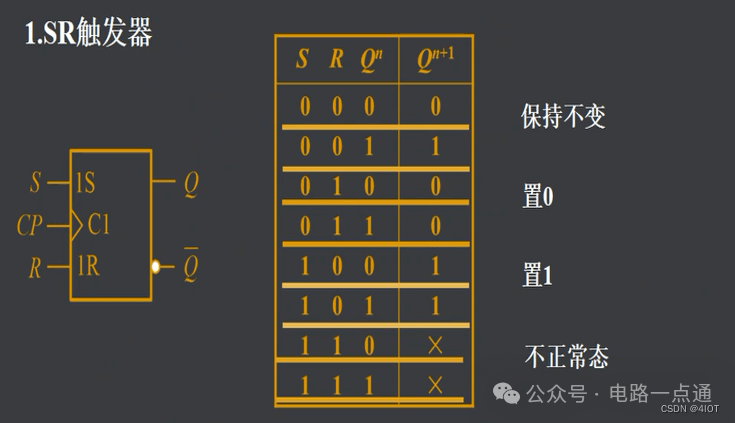

二、钟控SR锁存器

1、电路结构和逻辑符号

-

CP=0:基本SR锁存器输入端均为1,状态保持不变,锁存状态 -

CP=1:S、R通过与非门作用于基本SR锁存器 -

一是锁存器的抗干扰能力下降; -

二是限制了锁存器的使用范围。 -

主从触发器 -

维持阻塞触发器 -

利用传输延迟触发器 -

SR触发器 -

D触发器 -

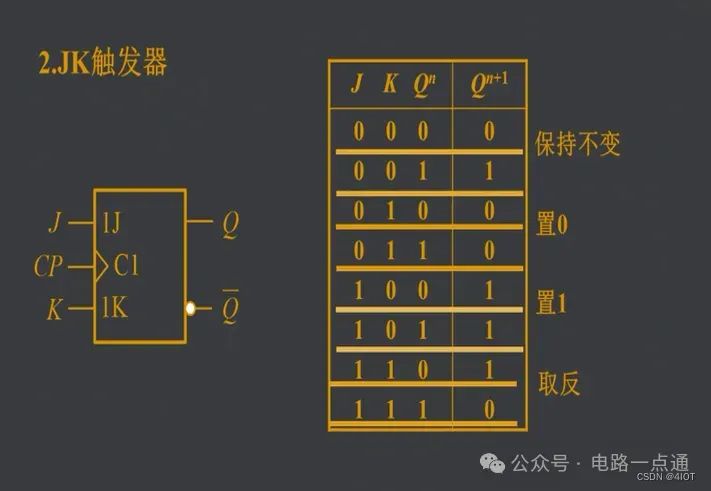

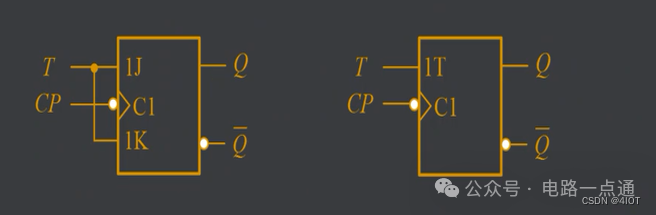

JK触发器 -

T触发器 -

T'触发器

2、逻辑功能

3、基本SR锁存器与钟控SR锁存器的区别

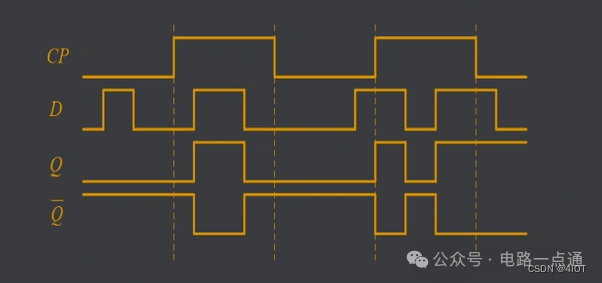

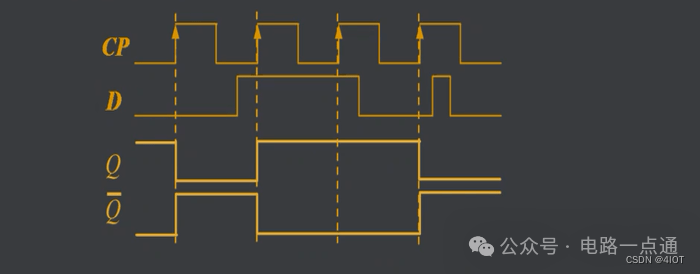

三、钟控D锁存器

1、电路结构和逻辑符号

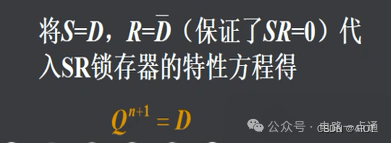

2、特性方程

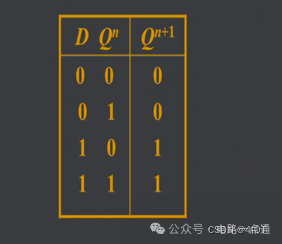

3、特性表

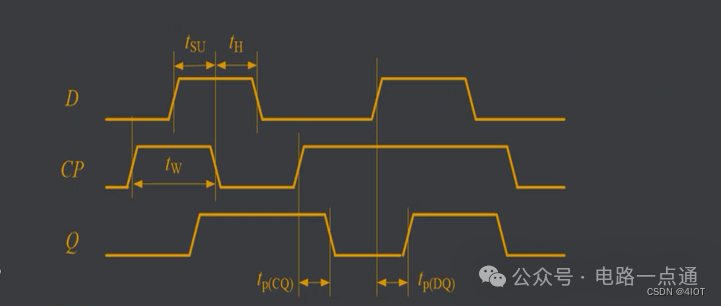

4、钟控D锁存器的动态参数(重点)

数据信号D在时钟信号CP下降沿到来之前应稳定的最小时间

数据信号D在时钟信号CP下降沿过去以后应稳定的最小时间

相对于CP信号由低电平变为高电平的时刻,Q的变化将会有一定的延时。

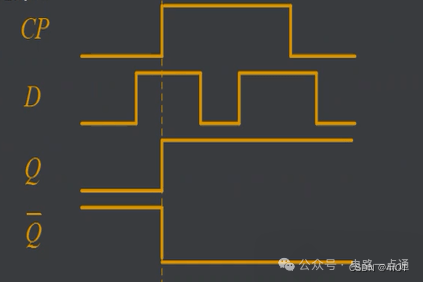

5、钟控锁存器存在的空翻现象(缘由)

6、为什么钟控锁存器会存在空翻现象?

触发器采用了不同的电路结构,只有 在CP脉冲的上升沿或下降沿时刻接收输入信号(Q才会动) ,一个周期内最多翻转一次,防止了空翻现象。

四、触发器的分类

3种不同结构的触发器

5种不同功能的触发器

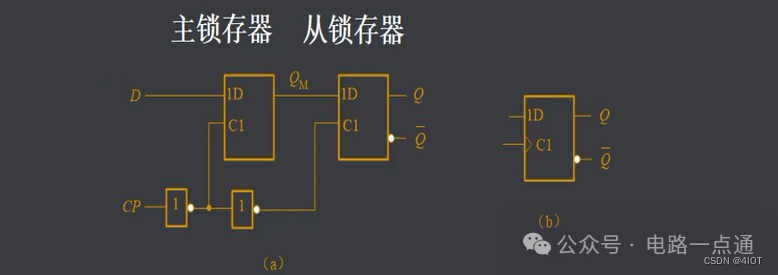

五、主从D触发器

1、主从D触发器电路结构及逻辑符号

2、工作原理

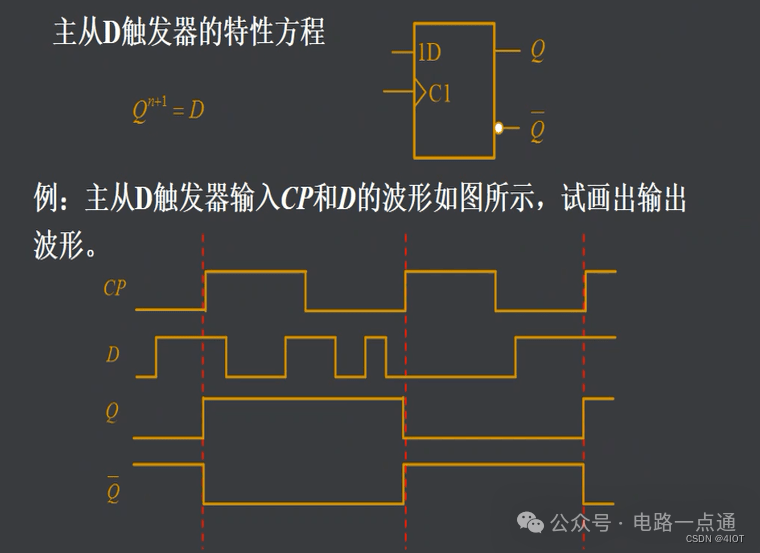

3、主从D触发器的特性方程

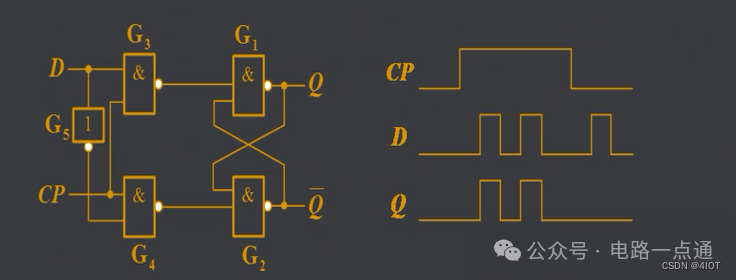

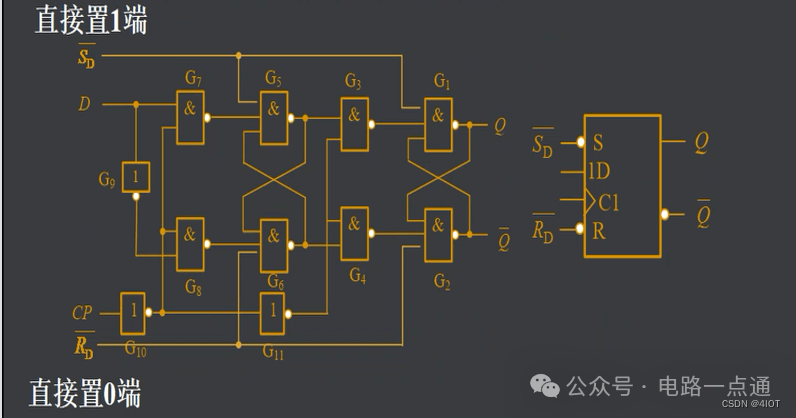

六、维持阻塞D触发器

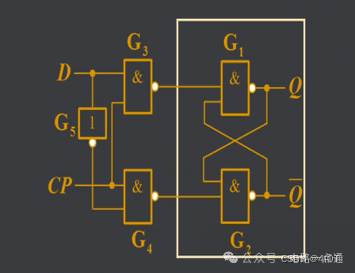

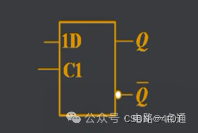

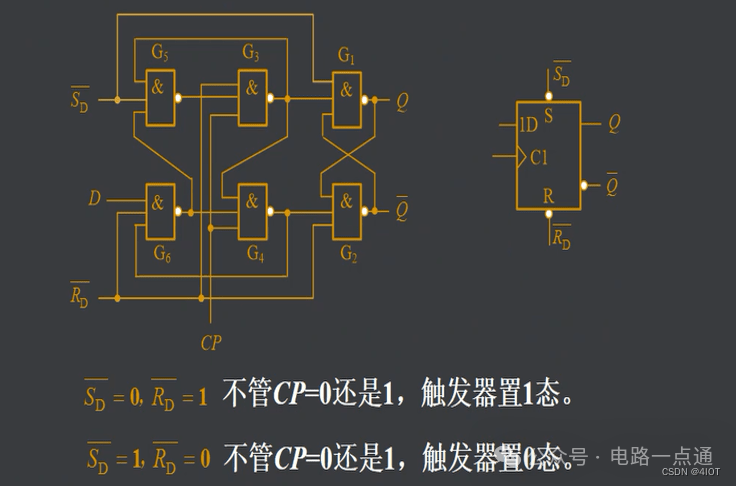

1、电路结构和逻辑符号

G3、G4、G5、G6构成了D信号的输入通道。

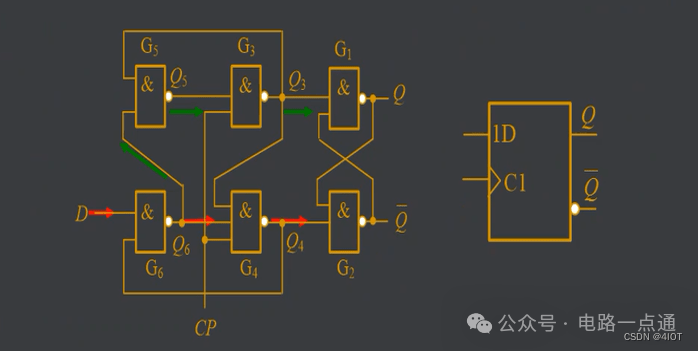

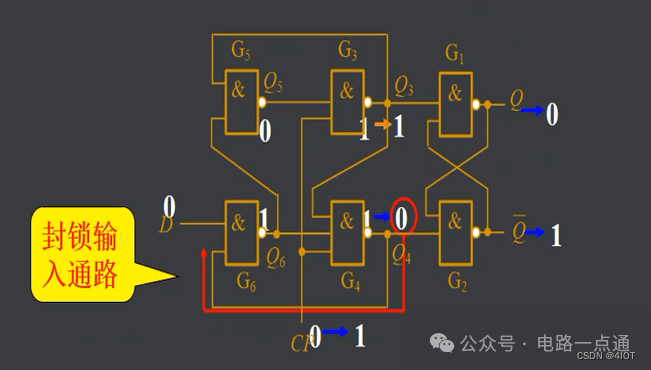

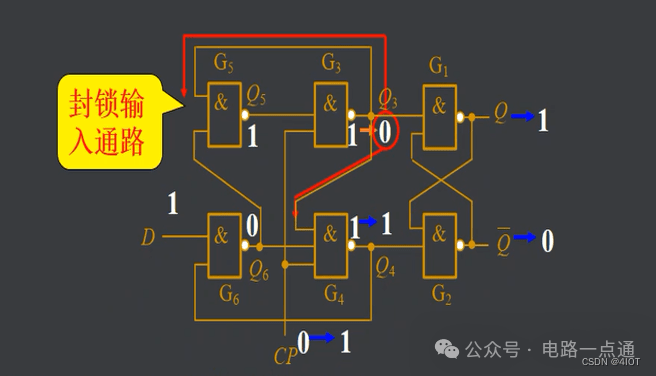

2、工作原理分析

(1)触发器维持原状态不变;

(2)输入信号D到达G4、G3的输入端,等待送入。

Q^(t+1)=D=0,并立即封锁输入通路。

则Q^(n+1)=D=1,并立即封锁输入通路。

3.具有异步置位、复位端的维持阻塞D触发器

七、五种不同功能的触发器

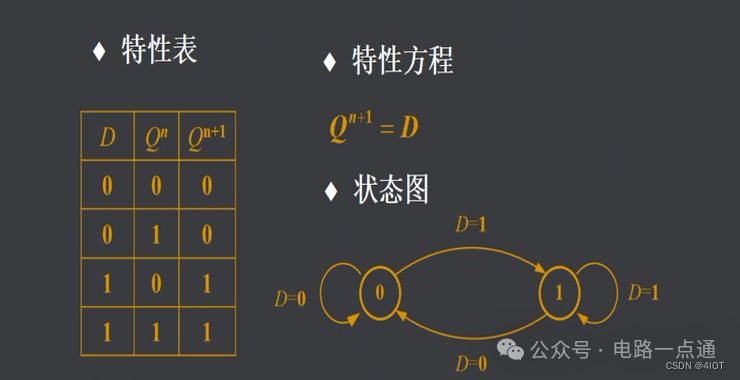

1、D触发器

2、SR触发器

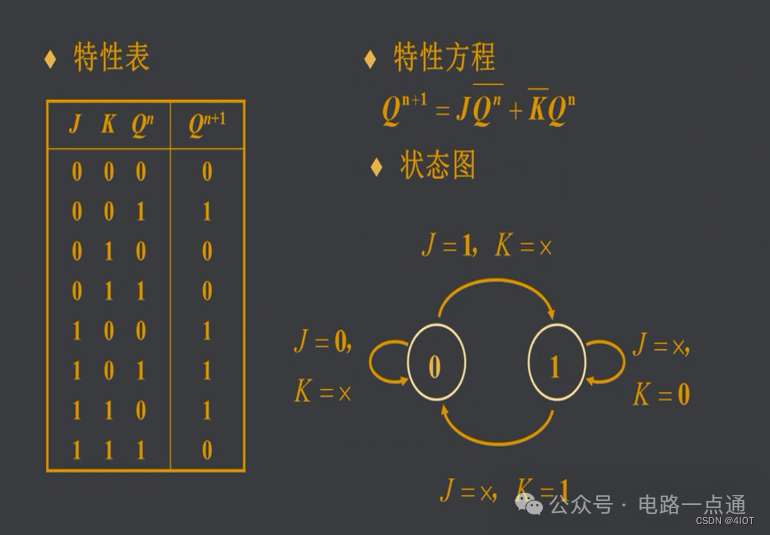

3、JK触发器

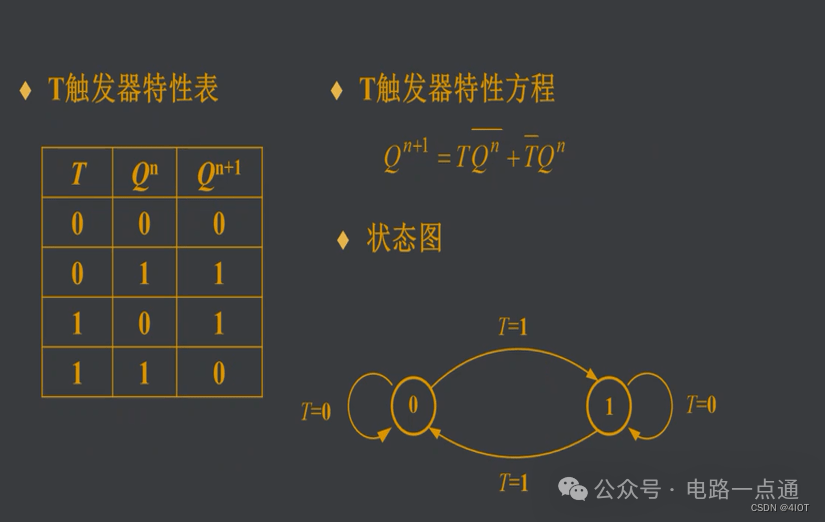

4、T触发器

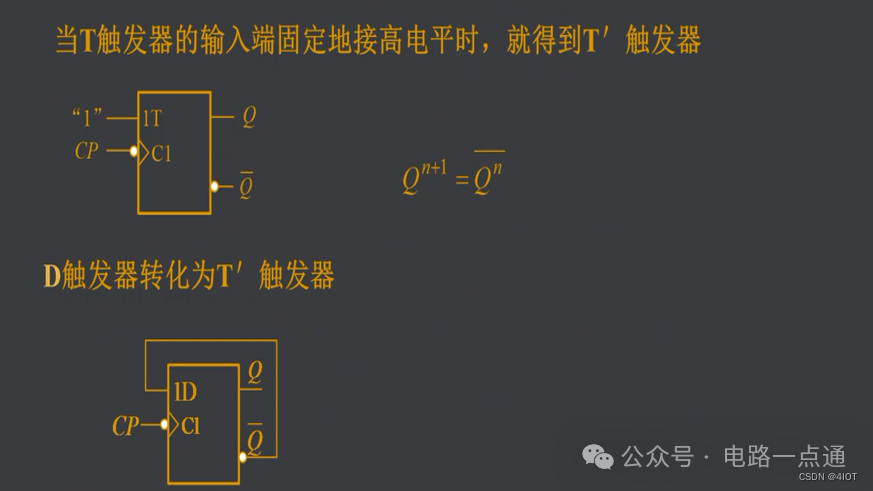

5、T'触发器

本文链接:https://blog.csdn.net/m0_60718520/article/details/127701668

进大家庭⭕圈探讨回复: 交流

分享

文章来源于: 电路一点通原文链接

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。