英特尔下场辟谣

近日行业内有消息称,英特尔已暂停部分其在马来西亚槟城的新芯片封装和测试项目,该项目是三年前宣布的70亿美元(约合人民币500亿元)投资的一部分。

对此,英特尔发言人近日正式回应表示,其在马来西亚扩展业务未有任何变化,即该项目照常推进中。

官方资料显示,英特尔于2021年宣布建设槟城新项目,承诺在10年内投资70亿美元。当时报道称,这项投资将在该国创造4000多个英特尔工作岗位以及5000多个建筑工作岗位。据悉,英特尔扩建槟城业务的目的是将其打造成美国境外首个先进3D芯片封装工厂,将聚焦最先进的3D IC封装Foveros,预计会在2024或2025年启用。

公开资料显示,英特尔的两大主要专业封装技术是EMIB和Foveros。其中,Foveros是一个希腊语单词,意为“独特的,特殊的”。该技术是英特尔发明的一种高性能三维集成电路(3D IC)面对面堆叠封装技术,于2019年面世。

今年1月,英特尔宣布3D Foveros先进封装技术已在美国新墨西哥州Fab 9开始大规模生产。从英特尔先进封装布局情况来看,该公司除了在美国奥勒冈州有相关研发与产能之外,包括新墨西哥州及上述提及的马来西亚槟城新厂,3个据点的3D先进封装产能相加,将于2025年时增加四倍,不过未透露厂区的产能。

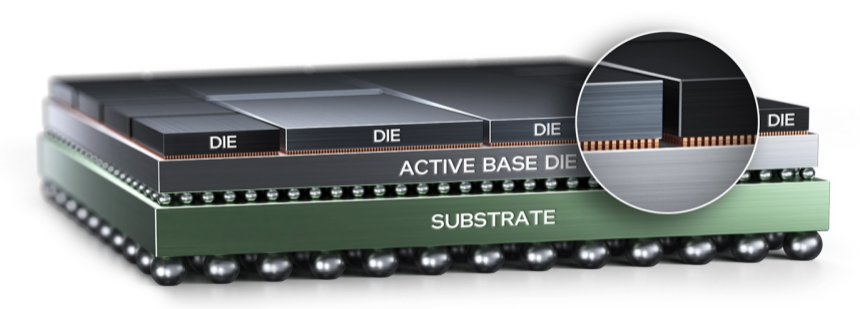

Foveros技术旨在将两个或多个芯片组装在一起,进行横向和纵向之间的互连,进一步降低凸点间距。但实际上,Foveros的逻辑芯片3D堆叠并不是一种芯片,而是逻辑晶圆3D堆叠技术,也就是把chiplet/die面对面叠起来。该技术通过巧妙的设计,可以通过将存储堆叠在活动组件之上来显著改善某些组件的延迟和带宽。产品可以分成更小的小芯片 (chiplet) 或块 (tile),其中 I/O、SRAM和电源传输电路在基础芯片中制造,高性能逻辑小芯片或块堆叠在顶部。

图片来源:英特尔

Foveros在芯片内实现极低功耗和高密度的芯片间连接,最小化了分区的开销,能够为每个区块选择理性的芯片工艺,并保障了成本和性能提升,简化了SKU(库存量单元)的创建,更容易定制且更快速地上市。不同的技术版本包含Foveros Omni、Foveros Direct。

英特尔第一代Foveros是采用10nm工艺推出,功耗极低,为每比特0.15皮焦耳,带宽是同类2.5D Si中介层的2-3倍,功率可从3W扩展到1千瓦,当时凸点间距为50微米。

Foveros Omni允许芯片分离,灵活性强,可以在混合芯片节点上将多个顶芯片块和多个基块混合在一起,为芯片到芯片互连和模块化设计提供了性能3D堆栈技术。

Foveros Direct则是Foveros Omni的补充,是支持直接连接一个或多个小芯片至作用中底层芯片,以创造复杂系统模组。据英特尔指出,“直接”连接是透过将个别小芯片的铜线以热压缩方式与晶圆连接,或是直接让整个晶圆彼此堆叠连接。此连接技术可以是“面对面”或是“面对背”,并纳入来自不同晶圆代工的芯片或晶圆,提高产品架构弹性。而连接频宽由铜线间距(以及产生的密度) 决定。第一代Foveros Direct 3D会使用9um的间距连接铜线;第二代则会缩小到间距只有3um。该技术实现了10微米以下的碰撞间距,提高了3D堆栈的互连密度,为功能芯片分区开创了过去无法实现的新概念。

Foveros Direct 3D在堆叠芯片之间支援高频宽且低延迟的互连(图片来源:英特尔)

英特尔曾强调,随着整个半导体产业进入在单个封装中集成多个小芯片(Chiplets)的异构时代,英特尔的3D Foveros 和2.5D EMIB等先进封装技术将可以达成在单个封装中整合一兆个电晶体,以便在2030年之后继续持续推动摩尔定律的前进。

EMIB技术也在持续升级,今年5月末,AMD和Intel公布了3.5D封装。值得关注的是,英特尔的EMIB 3.5D是在一个封装中嵌入多晶粒互连桥接和Foveros 技术,适合需要在一个封装中组合多个3D堆栈的应用。其Data Center GPU Max Series SoC,使用 EMIB 3.5D,打造出英特尔有史以来大批量生产的最复杂的异构芯片,该芯片拥有超过1000亿个晶体管、47个活动磁贴和5个工艺节点。

封面图片来源:拍信网

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。