如何降低EMI,有源技术和无源技术哪些最有效?

电源电路设计的电磁干扰(EMI)降低技术分为两类:有源技术和无源技术。无源技术的重点是通过各种滤波技术、足够的屏蔽、牢固的接地和正确的PCB布局来降低 EMI 水平。

有源方法将重点关注修改脉宽调制 (PWM) 控制信号形状,以降低 EMI 或将信号能量分布在较宽的频率范围内。

同步半桥降压转换器的 EMI 分析

通过分析一个非隔离、同步、半桥、降压转换器,该转换器具有基于片上零电压开关 (ZVS) 检测的栅极驱动器,该驱动器采用扩频调制控制。

降低降压转换器软开关半桥中的传导 EMI

电路设计师一直在努力减少电路板设计中的传导电磁干扰。这种 EMI 挑战在开关电源 (SMPS) 中尤其明显。作为设计人员,在许多情况下,我们倾向于使用 SMPS 而不是线性电源。这是由于 SMPS 具有尺寸更小、效率更高、重量更轻以及能够将输出电压升压的优点。

SMPS设计确实有一个主要弱点——噪声。高 di/dt 和 dv/dt 的存在是晶体管开关动作的结果。因此,电路设计者必须使用以下技术来减轻这种噪声:

降低开关转换速度

寻找对设计中其他电路影响较小的开关频率

高 dv/dt 缓冲

最大限度地减少高 di/dt 的电流环路区域

如果这些方法不起作用,设计人员应考虑采用扩频频率抖动 (SSFD) 技术。

降低 EMI 以实现最佳信号完整性

PCB设计和布局注意:

PCB 走线必须短且在 PCB 边缘的 5 个线宽范围内。

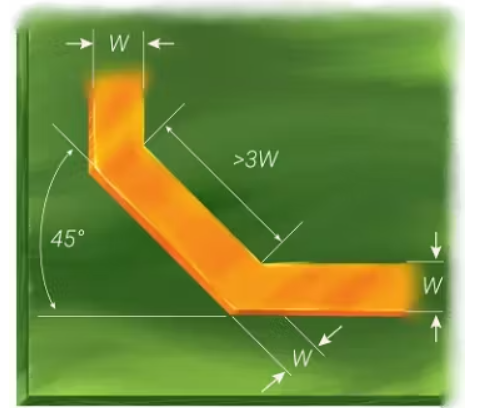

设计人员应使用 45 度弯曲以及带状线(避免微带线)。

避免层变换。

不要通过插槽传输任何高速信号。

使用三端电容器来减少电感效应。

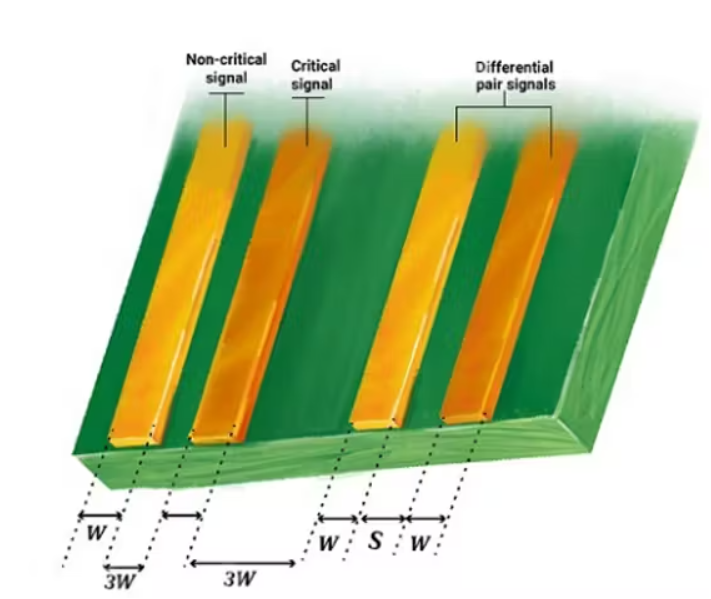

保持差分走线紧密间隔。

将所有其他走线排列成彼此间隔三个走线宽度

使用45度转弯

将相邻走线间隔3个线宽。

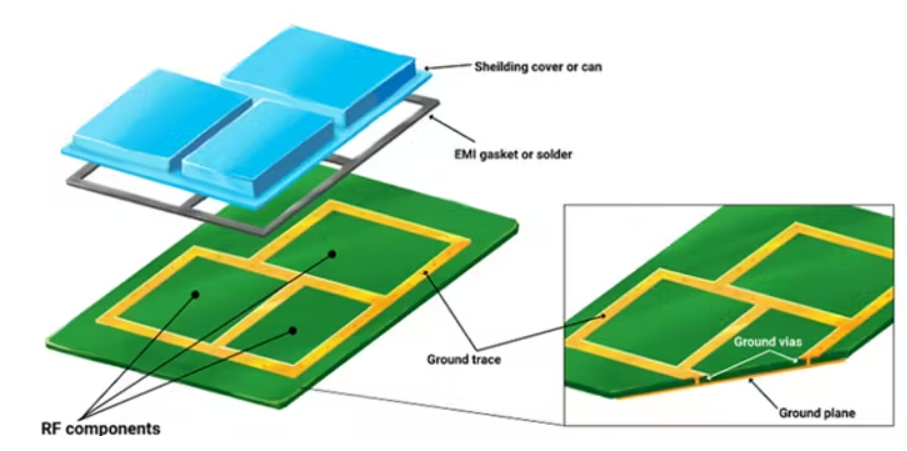

使用EMI屏蔽

通过使用 EMI 屏蔽罩住 PC 板并使用屏蔽电缆,可以最大限度地减少 EMI。

扩频频率抖动

Texas Instruments 的 TPS23730 以太网供电 (PoE) IC 具有软关断功能,可降低开关功率管上的压力并确保关断过程的可预测性,同时降低FET的BOM成本。可编程扩频频率抖动 (SSFD) 是另一个出色的功能,可以最大限度地减小 EMI 滤波器的尺寸并降低成本。

该设计还具有启用时用于过载保护的打嗝模式,并确保满足 802.3bt 启动要求。

知名女演员海蒂·拉玛 (Hedy Lamarr) 于 1942 年与乔治·安泰尔 (George Antheil) 一起申请了“秘密通信系统”专利。这种频率切换系统有助于改进鱼雷的无线电制导。 五十年后,即 1992 年,弗吉尼亚州布莱克斯堡的理工学院的一些研究人员在电源中使用了扩频技术,减少了噪声传播能量以及与 SMPS 相关的谐波峰值。

设计人员使用正确的扩频技术,可以成功将这些技术应用到系统中,从而改善噪声特征,实现更高水平的电磁兼容性。

双随机扩频 (DRSS)

扩频方法通常用于开关模式转换器和控制器,以减少开关产生的 EMI。 双随机扩频 (DRSS)采用数字算法,能够在多个频段中扩频频谱发射,同时不会牺牲这些频段的性能。

扩频方法(也称为抖动)可以减少基波开关频率下的固定频率开关及其谐波产生的 EMI。

总结

PCB 设计和布局必须使用可靠的 EMI 缓解技术来消除传导和辐射 EMI,同时也可以利用诸如DRSS 和 SSFD 等芯片技术降低 EMI。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。