PCIe 7.0 VIP如何解锁万亿参数AI模型的高性能计算潜力?

在近期的博文《新思科技率先推出PCIe 7.0 IP解决方案,加速HPC和AI等万亿参数领域的芯片设计》中,新思科技宣布推出综合全面的PCIe Express® Gen 7(PCIe 7.0)验证IP(VIP)解决方案,以支持高性能计算设计中人工智能(AI)应用所需的高速度和低延迟。

在《PCIe 7.0数据速率的光传输首秀,一睹为快!》一文中,可查看业界首个PCIe 7.0光传输Demo。

PCI Express的演进

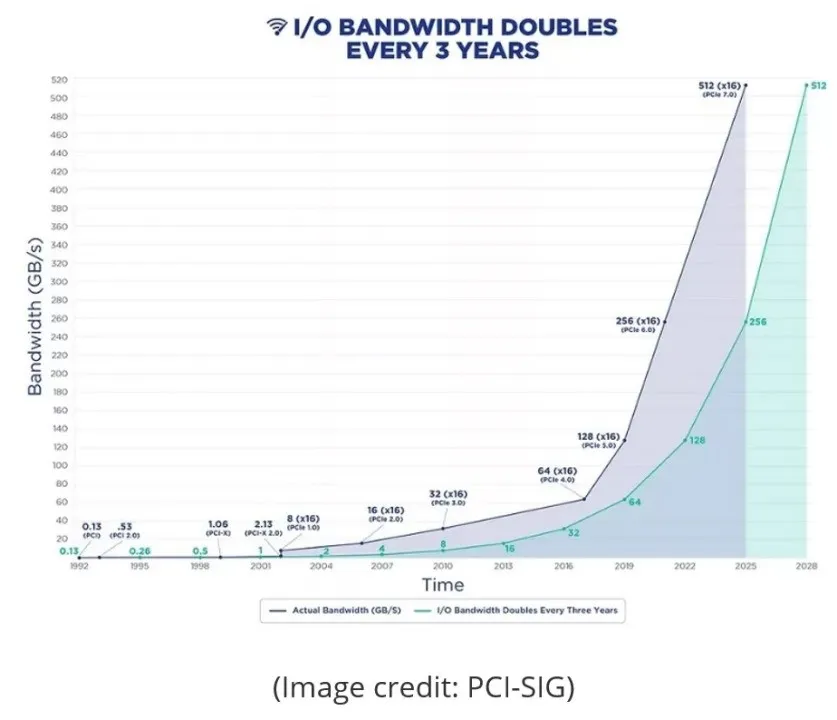

自2003年推出以来,PCI Express在技术、规格和传输速度方面不断进步,成为了一项成功的标准化计划倡议和数据传输协议。PCIe 5.0为云计算资源提供32G传输速度和CXL一致性;而在流量控制单元(FLITS)和PAM4调制的加持下,PCIe 6.0将性能提高至64G传输速率,实现了高效率、低延迟的通信和一致性。PCIe 7.0的加载-存储功能和高达512 GB/s的安全数据传输带宽,让连接多个加速器并高效处理大型复杂人工智能和机器学习模型成为可能。

PCIe 7.0规范新增了哪些内容?

PCIe 7.0规范中包含以下特性:

经由x16链路,数据速率达128 GT/s,经由x16链路,双向最高可达512 GB/s

PAM4信令

1b/1b FLIT模式编码

前向纠错(FEC)

更出色的功耗和成本效率

采用IDE协议,确保数据安全

向后兼容PCIe规范的早期版本

包含睡眠状态,以提供灵活性和低功耗

新思科技PCIe 7.0验证IP(VIP)的特性

新思科技PCIe验证IP可对基于各种PCIe规范(PCIe 1.0至7.0)的设计实现方案进行验证,可用于SoC和系统级设计,以加速验证收敛。

新思科技PCIe验证IP解决方案支持PCIe 7.0,并利用了以下特性来解决设计验证的复杂性:

支持每条通道最高128.0 GT/s的数据速率,同时保持RC和EP设备的向后兼容性,进而推动从PCIe 6.0无缝过渡到PCIe 7.0。

原生System/Verilog UVM架构,有助于轻松集成到仿真环境中并加快测试平台开发。

集成验证计划、测试套件和功能覆盖率,可加快验证过程并赢取竞争优势。

基于IDE的数据完整性和安全保护,可防止数据和系统泄露。

丰富的可配置选项和内置的协议检查,有助于在已采用协议开发的市场中保持竞争力。

新思科技正在与早期客户和伙伴合作,整合最新规范中提供的新功能,助其增强下一代设计的标准架构。

新思科技VIP原生集成了Verdi®协议分析器调试解决方案和Verdi®性能分析器。

要在SoC上运行系统级有效载荷,速度更快且基于硬件的流片前解决方案必不可少。基于新思科技IP的新思科技事务处理器、内存模型、混合和虚拟解决方案可在高速的验证硬件,新思科技ZeBu®硬件加速解决方案和新思科技HAPS®原型系统上实现丰富的验证工作和验证用例。

文章来源:新思科技

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。