本文从软件工程师角度对HDMI spec进行解析,基于的spec版本为1.4,也是设备支持最多最成熟的版本,目前最新版本为2.0。

1 概述

HDMI(High-Definition Multiface Interface)是Hitachi, Panasonic, Philips, SiliconImage, Sony, Thomson, Toshiba几家公司共同发布的一款音视频传输协议,主要用于DVD, 机顶盒等音视频source到TV,显示器等sink设备的传输。传输基于的是TMDS(Transition Minimized Differential Signaling)协议。此外,使用TMDS也是DVI标准的主要特点 。

2 物理结构

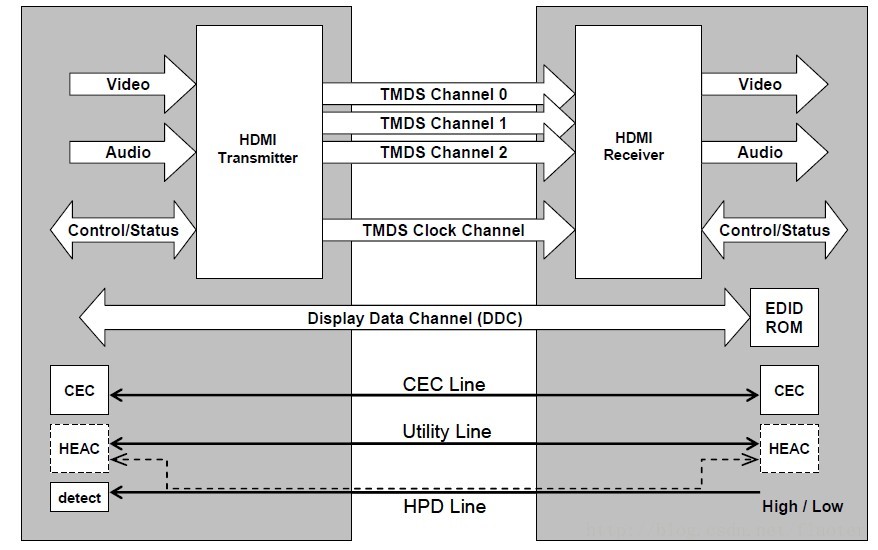

上图是HDMI block结构图,可以看出HDMI用于audiovisual source和sink之间的连接,HDMI cable由3组差分信号传输TMDS数据,1组差分信号传输clock。此外,HDMI还有一个DDC的通道连接到sink的EDID。CEC和HEAC都是HDMI的可选协议。

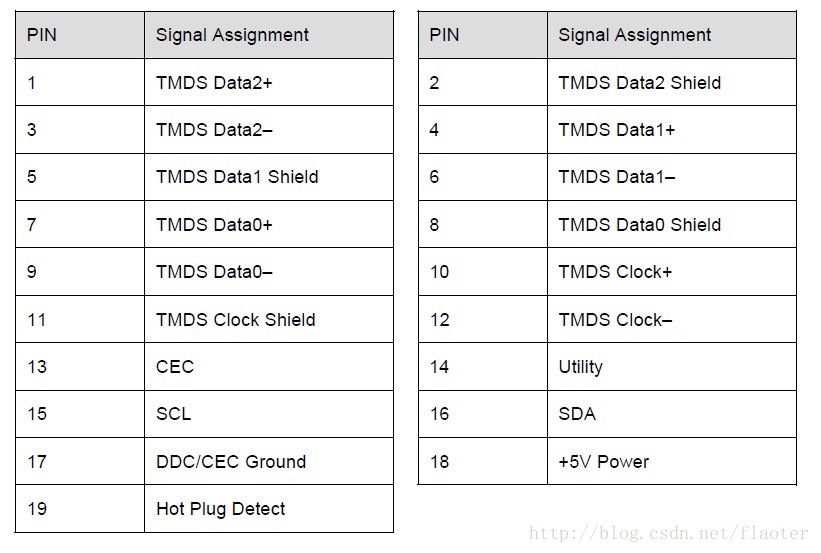

HDMI定义了五种类型的connector,上图是最常见的type A。

1-9是TMDS data传输用到的引脚,共有三组;

10-12是TMDS clock传输用到的引脚,共有一组,TMDS clock就是pixel clock;

13是CEC引脚,一种消费电子兼容的传输协议;

14是保留引脚;

15,16是DDC的引脚,DDC是基于I2C协议传输,故引脚为SCL和SDA;

17是接地;

18是+5V power;

19是HPD引脚,用于建立连接。

3 传输

概述

HDMI传输由三组TMDS通道和一组TMDS clock通道组成,TMDS clock的运行频率是video信号的pixel频率,在每个cycle,每个TMDS data通道发送10bit数据。

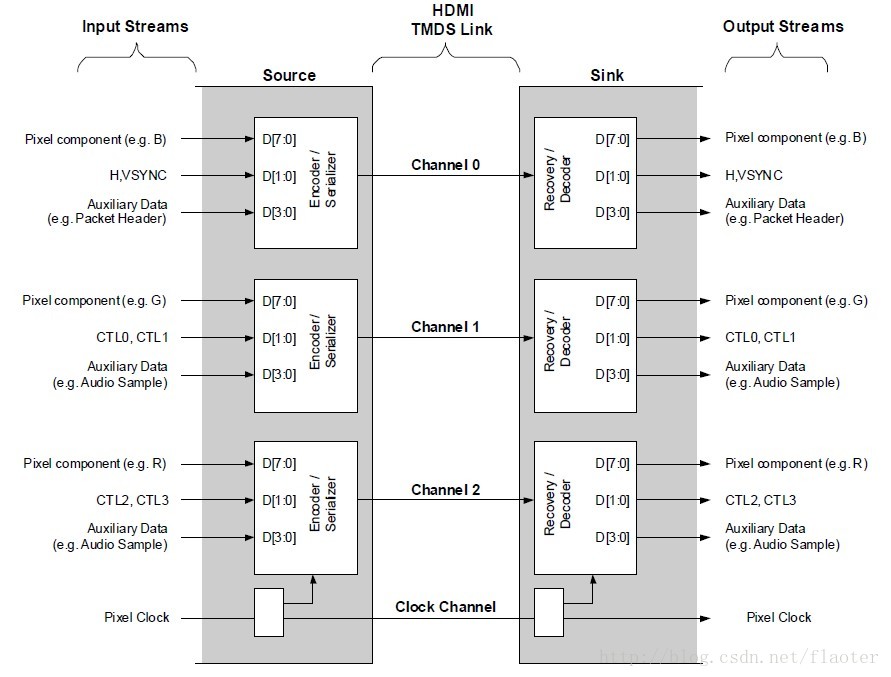

上图是HDMI传输的示意图,从图中可知,HDMI传输如下四种类型数据:

(1)Preamble控制信息,图中的CTLx,可用来表示后面传输的是data island还是video data。通过channel1和2的D[1:0]传输,占用4bit。

(2)Data Island,即数据包,如Audio数据包。通过3个channel的D[3:0]传输,占用12bit。

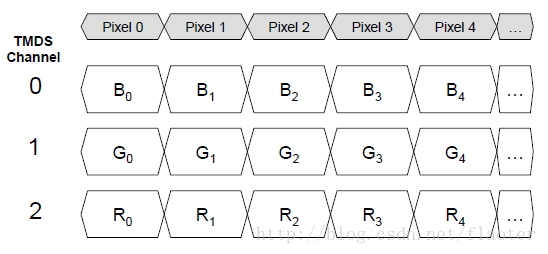

(3)Video Data,视频数据。示意图中传输的是RGB格式图像,R,G,B分别通过channel2,1,0传输,每个颜色8bit,共24bit。

(4)HSYNC, VSYNC。使用channel0的D[1:0]传输,占用2bit。

8bit的数据在source经过TMDS encoder后得到10bit数据,经过serializer后串行输出;在sink端先进行复原成10bit的数据,再通过TMDS decoder得到8bit的源数据。

此外,HDMI视频是stream式的传输,不涉及packet式的传输。

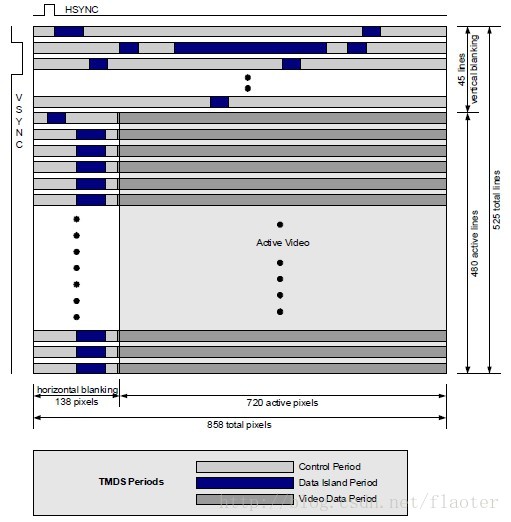

上图是传输720x480p video的hdmi timing图。

在video data period,有效的video数据进行传输;

在data island period,audio和auxiliary数据以包的形式进行传输;

在control period,CTLx和HSYNC, SYNC进行传输。

data island period和control period都是在消隐区进行。图中行消隐占用138像素,场消隐占45行。

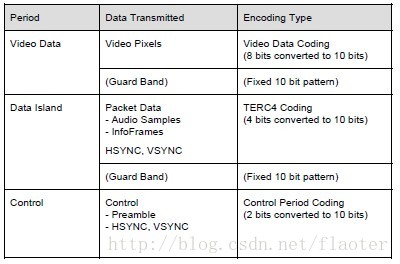

上图中是对时序图中描述的三种period分别传输的数据和编码类型进行说明。video数据从8bit/channel encode后变为10bit/channel, data island的packet数据从4bit/channel encode后为10bit/channel, control数据从2bit/channel encode为10bit/channel。

Control Period

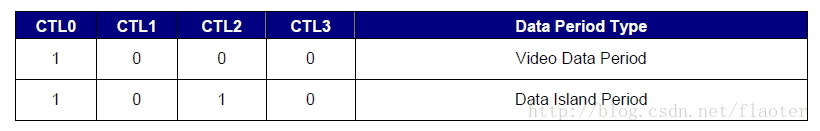

只有两种类型的preamble信息组合,CTL0:3=1000代表接下来的是video data period,CTL0:3=1010代表接下来的是data island period。HSYNC, VSYNC此时也有可能发生变化。

Video Data Period

video data period以2个字符(pixel)长度的leading gurad band开始,guard band如下:

ch0: q_out[9:0] = 0b1011001100

ch1: q_out[9:0] = 0b0100110011

ch2: q_out[9:0] = 0b1011001100

Data Island Period

data island period传输audio数据和辅助数据,辅助数据包括Infoframe和其他用于音视频信息描述的数据。data island period以2个字符长度的leading guard band开始,并以2个字符宽度的trailing guard band 结束。guard band如下:

ch0: q_out[9:0] = n.a

ch1: q_out[9:0] = 0b0100110011

ch2: q_out[9:0] = 0b0100110011

data island传输的packet类型和格式详见spec说明。

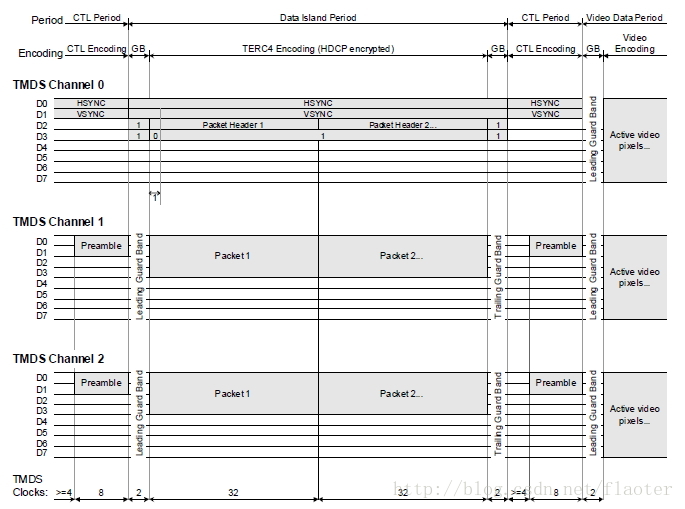

三个传输阶段的过渡过程如下图所示:

(1) 左一是control period, 分别占用三个channel的D[1:0],channel 0传输HSYNC, VSYNC, channel1,2 传输Preamble

(2) 左二是data island period,分别占用了三个channel的D[3:0],channel 0的D[1:0]传输HSYNC, VSYNC, channel0的D[3:2]传输packet header, channel 1,2的D[3:0]传输packet。并且两端以guard band隔离

(3)右二接下来又是control period

(4)右一是 video data island, 占用了全部三个通道,并且开始以guard band 隔离

4 Video

支持三种pixel encoding:RGB4:4:4, YCbCr4:4:4, YCbCr4:2:2

video format除了CEA-861-D中格式外,还会支持一些较特殊的格式

color depth可支持一个像素24, 30, 36和48bits

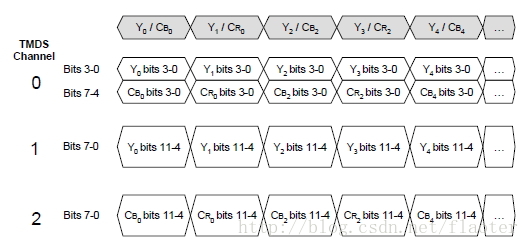

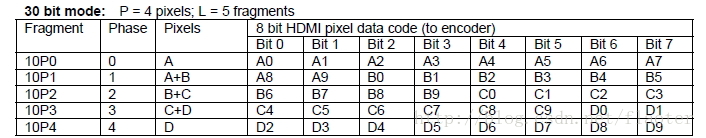

下面分别是24bit/pixel的RGB444, YCbCr422, YCbCr444的pixel encoding示意图。RGB444每个颜色占8bit, YCbCr422中Y占12bit,C占12bit,YCbCr444中Y,Cb,Cr都占用8bit。

Deep Color模式

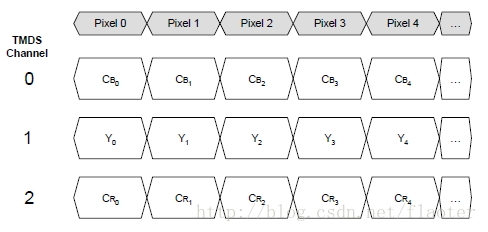

Pixel Packing

24 bit mode: 1 pixel/group, 1 fragment/group

30 bit mode: 4 pixel/group, 5 fragment/group

36 bit mode: 2 pixel/group, 3 fragment/group

48 bit mode: 1 pixel/group, 2 fragment/group

1fragment/TMDS clock, 如30bit下的4pixel,需要5次传输完成,每次1个fragment。

5 Audio

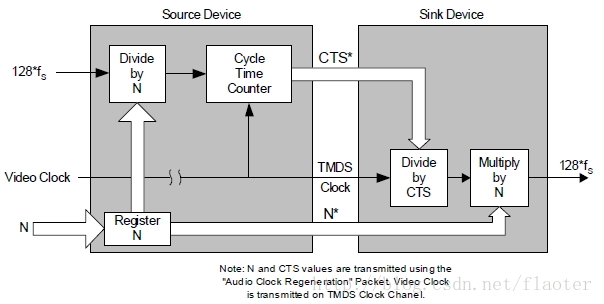

Audio数据以Audio Sample Packet或High Bitrate Audio Stream Packet的形式传输,但是HDMI没有传输audio clock,因此sink设备需要进行audio clock regeneration。原理如下:

128∗fs=N×fTMDS/CTS

N和CTS会在Audio Clock Regeneration Packet中进行传输,TMDS clock可通过硬件获取,因此sink端可算出source传输的audio clock。

6 Control

InfoFrame

Infoframe以Infoframe packet的形式传输,它的大小不超过30字节加上一个checksum字节。具体infoframe的格式及内容需要查看spec。

AVI(Auxiliary Video Information) Infoframe

Audio Infoframe

HDMI Vendor Specific Infoframe, 传输4kx2k或3D格式时需要发送此packet

EDID & DDC

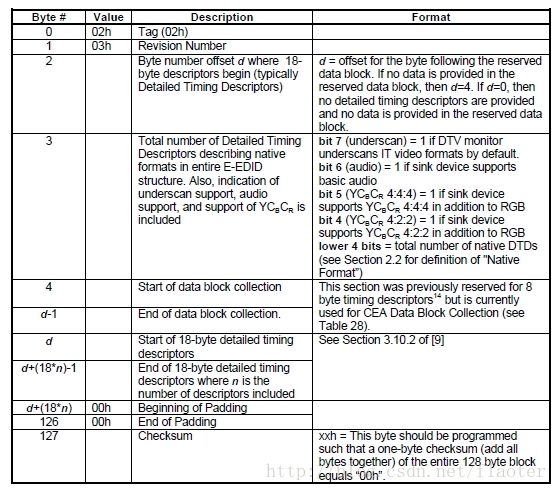

sink设备在ROM中存放EDID信息,source在收到HPD后会通过DDC通道读取EDID得到显示设备的属性。EDID包含两部分,前128字节符合EDID1.3数据结构,128字节的扩展EDID,符合CEA extension verison3。CEA extension verison3如下图所示。

HDMI VSDB

HDMI sink设备在第一个扩展EDID中包含HDMI VSDB,source在读取EDID后会根据是否有此block来判断设备是HDMI还是DVI。

Hotplug

source会监测HPD pin的状态,当source和sink连接后,如果HPD为高电平,说明sink设备正常可以工作,source可通过DDC读取EDID,如果为低电平,说明sink已断开。

sink可通过拉低HPD超过100ms来向source表明EDID发生了变化,此时source会重新读取EDID。

HDCP

涉及内容较多,会在单独章节中讲解。