据外媒消息,英特尔副总裁兼亚太区总经理Steven Long表示,目前英特尔正在马来西亚槟城兴建最新的封装厂,强化2.5D/3D封装布局。这将是继英特尔新墨西哥州及奥勒冈厂之后,首座在美国之外采用英特尔Foveros先进封装架构的3D封装厂。

英特尔表示,其规划到2025年3D Foveros封装的产能将达到当前水平的四倍,届时槟城新厂将会成为英特尔最大的3D先进封装据点。此外,英特尔还将在马来西亚另一居林高科技园区兴建另一座组装测试厂。未来英特尔在马来西亚的封测厂将增至六座。

结合此前英特尔在先进制程上一系列动态,外界预期,英特尔将结合先进制程与先进封装两条线,希冀在晶圆代工领域实现“1加1大于2”的效果。在2022年末举行的英特尔On技术创新峰会上,英特尔CEO基辛格便表示,英特尔代工服务将开创“系统级代工的时代”。不同于仅向客户供应晶圆的传统代工模式,英特尔还提供硅片、封装、软件和芯粒等服务。

当然,发力先进制程、先进封装的不只有英特尔,台积电、三星两位强敌也丝毫不懈怠,三者在晶圆代工市场之中的硝烟渐浓,谁又将祭出新一代最具竞争力的产品?

No.1

英特尔先进封装工艺

英特尔方面,除了上述封装厂扩产新建消息外,其在封装技术上的进步也引起业界关注。

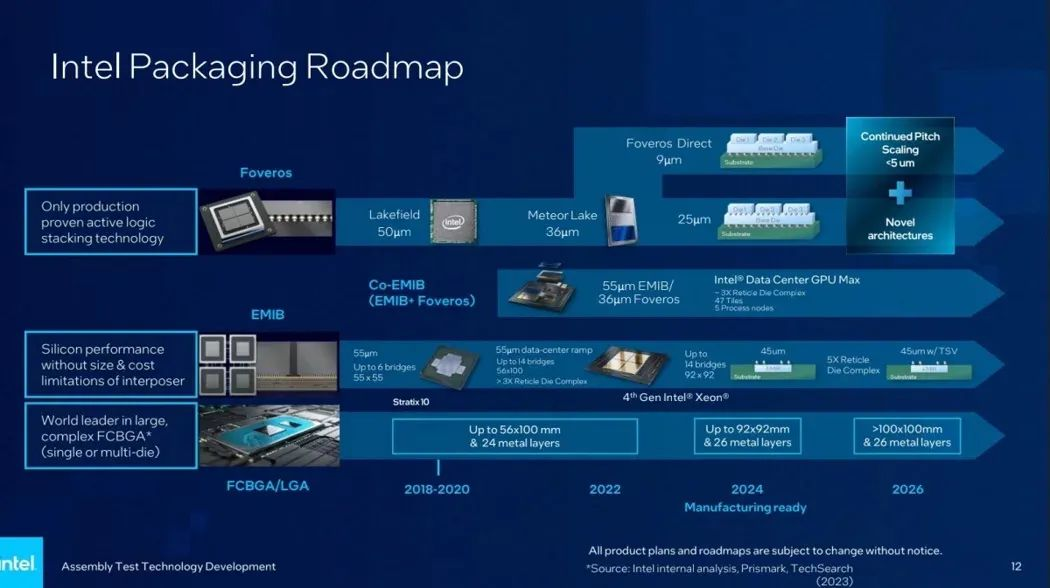

通过多年研究探索,英特尔目前压注的主要是2.5D EMIB、3D Foveros等几种先进封装技术,力图通过2.5D、3D和埋入式等多种异构集成形式实现互连带宽倍增与功耗减半的目标。

2017年始,英特尔开始导入EMIB封装,第其一代Foveros封装则于2019年推出,当时凸点间距为50微米。英特尔预计将在今年下半年稍晚推出的最新Meteor Lake处理器,将利用第二代Foveros封装技术,使凸点间距进一步缩小为36微米。

据英特尔官网今年5月19日消息,英特尔发布了先进封装技术蓝图。在蓝图中,英特尔期望将传统基板转为更为先进的玻璃材质基板。从英特尔PPT中看到,英特尔为此开发了共同封装光学元件技术,通过玻璃材质基板设计,利用光学传输的方式增加信号交换时的可用频宽。英特尔称,这一设计也使得芯片可以支持热插拔使用模式。

图片来源:英特尔官网截图

今年7月,英特尔再宣布计划推出Foveros Direct,实现了向直接铜对铜键合的转变,通过HBI(Hybrid Bonding)技术以实现10微米以下的凸点间距,让不同芯片之间可实现10倍以上的互联密度提升。这就使得晶圆制造与先进封装之间的界限不再那么泾渭分明,但其对先进封装工厂要求也大幅提升。

英特尔并未透露现阶段其3D Foveros封装总产能,仅强调除了在美国奥勒冈州与新墨西哥州之外,在未来的槟城新厂也有相关产能建置,这三个据点的3D封装产能合计将于2025年时增为目前的四倍。英特尔副总裁Robin Martin 22日受访时强调,未来槟城新厂将会成为英特尔最大的3D Foveros先进封装据点。

英特尔二年前宣布投资35亿美元扩充新墨西哥州的先进封装产能,至今仍进行中。至于槟城新厂,该公司表示,兴建进度符合计划,外界推估,该新厂可能于2024年稍晚或2025年完工运作。

No.2

三星先进封装

近日外媒消息显示,三星将为AMD提供封装服务。据悉三星电子第四代HBM(HBM3)以及封装服务已经通过AMD品质测试。AMD的Instinct MI300系列AI芯片计划采用三星HBM3及封装服务,该芯片结合中央处理器(CPU)、图形处理器(GPU)及HBM3,预计今年第四季发布。

业界消息显示,由于三星是目前唯一能同时提供先进封装解决方案及HBM产品的企业,AMD原本考虑使用台积电的先进封装服务,但因其产能无法满足需求,最终只能改变计划。

事实上,由于台积电CoWoS先进封装技术的领先性,三星在当前的先进封装之争中并不占优势,为了争夺未来先进封装市场份额,三星正在开发更先进的 I-cube 和 X-cube 封装技术。此外,三星近期宣布,将在2025年推出全球首款使用闸极全环晶体管 (GAA) 制程3D先进封装,提供客户从代工生产到先进封装完整解决方案。目前,产业界尚未尝试结合GAA制程与3D先进封装,因两种制程复杂性都很高。

三星2020年首次推出7纳米EUV制程的3D先进封装X-Cube,领先台积电。2022年三星率先量产3纳米GAA制程,半导体业务部门另组先进封装(AVP)团队,加速下代半导体后段制程研发,三星预估2027年如期量产1.4纳米先进制程。

No.3

台积电先进封装

台积电方面先进封装CoWoS封装技术在近两年一直遥遥领先。台积电于2012年首次引入CoWoS技术,此后该技术持续迭代升级。

今年上半年业界消息显示,作为突破最大可制造芯片尺寸界限的努力的一部分,台积电正在研究其新的 Chip-On-Wafer-On-Substrate-L (CoWoS-L) 封装技术,该技术将使其能够构建更大的超级载体中介层。针对2025年的时间跨度,下一代TSMC的 CoWoS 技术将使中介层达到 TSMC 最大reticle的六倍,高于其当前中介层的3.3倍。这种强大的系统级封装 (SiP) 旨在供对性能要求很高的数据中心和 HPC 芯片使用。

目前,台积电凭借其领先的先进封装技术吃尽红利,英伟达、苹果和AMD的旗舰产品都离不开台积电及其先进封装技术的支持。今年6月,苹果新款Mac Pro换上了M2 Ultra,这颗苹果有史以来面积最大的SoC,由两颗M2 Max芯片“缝合”而成,晶体管数量直接翻倍,达到了1340亿颗,其所启用的便是台积电的先进封装技术——UltraFusion。这也表明台积电彻底将英特尔从苹果的Mac产品线挤出。

据TrendForce集邦咨询研究显示,产能方面,当前台积电CoWoS封装技术为目前AI服务器芯片主力采用者。集邦咨询估计在高端AI芯片及HBM强烈需求下,TSMC于2023年底CoWoS月产能有望达12K,其中,英伟达在A100及H100等相关AI Server需求带动下,对CoWoS产能较年初需求量,估提升近5成,加上AMD、Google等高端AI芯片需求成长下,将使下半年CoWoS产能较为紧迫,而此强劲需求将延续至2024年,预估若在相关设备齐备下,先进封装产能将再成长3-4成。

目前台积电面临的问题主要是产能供应不足,在2023年第二季度线上法说会上,台积电表示,到2024年CoWos产能将扩充2倍以上。台积电总裁魏哲家表示,与AI芯片相关的一些高级封装可能在2024年底之前仍然供应紧张。因此,需求可能在相当长的时间内持续超过供应,因为AMD和英伟达将无法扩大生产至某个点,尽管某些4nm和5nm的产能是可用的。

除了CoWoS技术外,台积电在先进封装上从不松懈。据 LexisNexis 的数据,台积电开发了最广泛的先进芯片封装专利库,目前台积电拥有 2,946 项先进封装专利,并且质量最高,衡量标准包括这些专利被其他公司引用的次数。在专利数量和质量方面排名第二的三星电子拥有 2,404 项专利。英特尔排名第三,其先进封装产品组合拥有1,434项专利。

No.4

结语

为了适配高性能运算、AI、5G等应用的最新需求,封装形态从2D迈向2.5D、3D的进程不可避免,目前在先进封装的市场争夺中,OSAT企业、晶圆代工厂、IDM、Fabless公司等均加入了其中,且斥资巨大。不同厂商对“先进封装”概念的理解直接影响着其技术产品布局,所导致的结果便是行业内各类产品还存在着较大差异性,最为直面的表现便是‘先进封装’与‘传统封装’之间的定义尚存争议。

这一背景下,不少业界人士认为,先进封装技术的优化还需要行业统一标准。英特尔制造、供应链和营运集团副总裁、战略规划部联席总经理卢东晖此前就强调,为使生态系统能从先进封装中获益,不断降低成本,英特尔呼吁建立新的行业标准和测试程序。

封面图片来源:拍信网