DS12C887电子万年历设计与制作详解

1、设计方案

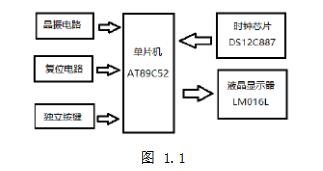

以单片机AT89C52为主控芯片,外围采用时钟芯片DS12C887,单片机P0口接DS12C887,P1.0口至P1.3口接按键,P1.4口至P1.7口分别接DS12C887的CS口、AS口、RW口、DS口。P2口接液晶显示器LM016L的D0至D7口,P3.3口接DS12C887的IRQ口,P3.4口、P3.5口分别接LM016L的E口和RS口。

2、系统总体框图

3、整体功能说明

本设计方案基于时钟芯片DS12C887做万年历设计。当程序执行后,LCD显示即时时间、年月日、星期、温度。设置4个按键,S1:设置键S2:上调键;S3:下调键;S4:复位键。操作按键可以重新设置时间、星期、日期。

基于DS12C887电子万年历的制作

所需的元器件介绍

一、单片机AT89C52介绍

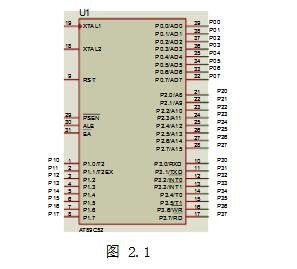

AT89C52是美国ATMEL公司生产的低电压,高性能CMOS 8位单片机,片内含8k的可反复擦写的只读程序存储器(PEROM)和256 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052产品引脚兼容,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大AT89C52单片机适合于许多较为复杂控制应用场合。引脚功能如图2.1所示

AT89C52单片机功能特性概述

AT89C52提供以下标准功能:8K字节Flash闪速存储器,256字节内部RAM, 32个I/O口线,3个16位定时/计数器,一个6向量两级中断结构,一个全双工 串行通信口,片内振荡器及时钟电路。同时,AT89C52了降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。掉电方式保存RAM中的内容。但振荡器停止工作并禁止其他所有部件工作直到下一个硬件复位。

AT89C52单片机主要引脚功能介绍

AT89S52单片机共有4个双向的8位并行I/O端口(Port),分别记作P0-P3,共有32根口线,各口的每一位均由锁存器、输出驱动器和输入缓冲器所组成。这四个口除了按字节寻址以外,还可以按位寻址。由于它们在结构上有一些差异,故各口的性质和功能有一些差异。

P0口:P0口是一组8位漏极开路型双向I/O口,也即为地址/数据总线复用口。作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口P0写“1”时,可作为高阻抗输入端用。在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

P1口:P1是一个带内部上拉电阻的8位双向I/O口,P1的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口。作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流。P1.0和P1.1还可分别作为定时/计数器2的外部计数输入(P1.0/T2)和输入(P1.1/T2EX)。

P2口:P2是一个带有内部上拉电阻的位双向I/O口,P2的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口。作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流。

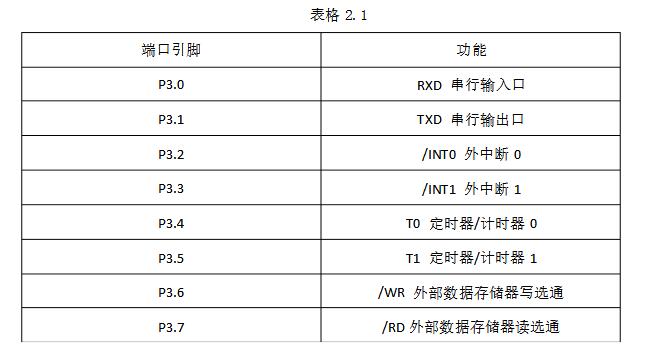

P3口:P3是一个带有内部上拉电阻的位双向I/O口,P3的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。对P3口写入“1”时,它们被内部上拉电阻拉高并可作为输入端口。此时,被外部拉低的P3口将用上拉电阻输出电流。其最重要的用途是它的第二功能。其主要第二功能如表格2.1所示。

/EA/VPP:外部访问允许。欲使CPU仅访问外部程序存储器,/EA端必须保持低电平(接地)。

XTAL1:振荡器反相放大器及内部时钟发生器的输入端。 XTAL2:振荡器反相放大器的输出端。

二、时钟日历芯片DS12887

能够自动产生年、月、日、时、分、秒等时间信息,芯片内部带有锂电池,外部掉电时,其内部时间信息能够保持10年之久;有12小时制和24小时制两种工作模式;时间的表示方法有两种:二进制数表示和BCD码表示。用户可对DS12887进行编程以实现多种方波输出,用户可对其内部的三路中断通过软件进行屏蔽。 2.2.1 引脚说明

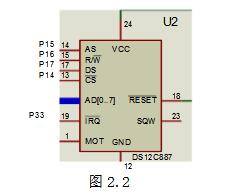

DS12C887引脚图如图2.2

1、Vcc:直流电源+5V输入

当Vcc输入为+5V时,用户可以访问DS12887内RAM中的数据,并可对其进行读、写操作;当Vcc的输入小于+4.25V时,禁止用户对内部RAM进行读、写操作,此时用户不能正确获取芯片内的时间信息;当Vcc的输入小于+3V时,DS12887会自动将电源切换到内部自带的锂电池上,以保证内部的电路能够正常工作

2、GND:地

3、MOT:总线模式选择。当MOT接Vcc时选用Motorola总线模式,当MOT接GND时选用Intel总线模式。

4、SQW:方波输出。当供电电压Vcc大于4.25V时,SQW脚可进行方波输出,此时用户可以通过对控制寄存器编程来得到13种方波信号的输出。

5、AD0~AD7:双向地址/数据总线。

6、AS:地址有效输入。

7、DS/RD:数据选通/读允许。当MOT接Vcc时作为数据选通;当MOT接GND时,作为读允许输入。

8、R/W:读/写允许输入。若MOT接Vcc,该引脚为高电平时读操作,为低电平时写操作;若MOT接GND,该引脚作为写允许输入。

9、CS:片选输入。低电平有效。 10、IRQ:中断请求输出。低电平有效。

11、RESET:复位端。低电平有效,复位操作不影响时钟日历工作。

12、NC:空引脚。 2.2.2 存储器分配与设置

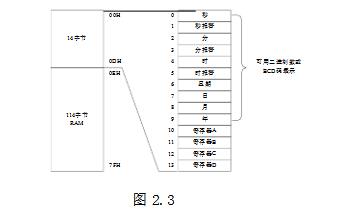

DS12887片内RAM与寄存器地址分配见图2.3。

DS12887带有128字节片内RAM:

1、10字节的时标寄存器:用来存储时间信息,地址00H~09H。CPU可以通过读取时标寄存器获得时间与日历值,也可以编程设置其初值,时标寄存器的值可以用二进制或BCD码表示。4字节的控制寄存器:用来存储控制信息,地址0AH~0DH。用户可通过对控制寄存器编程实现从SQW引脚输出多种不同频率的方波,并可对其内部的三路中断通过软件进行屏蔽。114字节作为通用RAM供用户使用,地址为0EH~7FH

2、UIP:更新周期标志。

当UIP=1时,表示芯片正处于或即将开始更新周期,在此期间不允许读写时标寄存器;当UIP=0时,表示没有更新周期,此时可读时标寄存器。

3、DV2~DV0:芯片内部振荡器RTC控制位。当芯片复位后500ms开始第一个更新周期。将这3位设置成010,可使芯片以内置的32.768kHz的振荡频率工作。

4、RS3~RS0:周期中断可编程方波输出速率选择位。

5、SET:允许更新周期位。可读/写,不受信号的影响。当SET=0时,芯片处于正常更新状态;当SET=1时,芯片正常更新被禁止。

6、PIE、AIE、UIE:分别为周期中断、闹钟中断、更新周期结束中断允许位。各位分别为“1”时允许发出相应的中断,由端输出。其中,UIE位在复位或设置SET为1时清零。

7、SQWE:方波输出允许位。当SQWE=1,按寄存器A输出速率选择位所确定的频率输出方波;当SQWE=0,SQW脚保持低电平。

8、DM:时标寄存器格式选择位。DM=0,为BCD码;DM=1,为二进制码。

9、24/12:24小时或12小时模式设置位。24/12=1,选择24小时工作模式;24/12=0,选择12小时工作模式。

10、DSE:夏令时允许标志位。当DSE=1时,夏时制设置有效。在四月的第一个星期日的1:59:59 AM,调到3:00:00 AM;在十月的最后一个星期日的1:59:59 AM,调到1:00:00 AM;当DSE=0无效。寄存器C 为中断标志位寄存器。

11、IRQF:中断申请标志位。

该位逻辑表达式为:IRQF = PF · PIE+AF · AIE+UF · UIE。当IRQF=1时,IRQ引脚将输出低电平。PF、AF、UF:这三位分别为周期中断、闹钟中断、更新周期结束中断标志位。只要满足各中断的条件,相应的中断标志位将置“1”。 10、 VRT:芯片内部RAM与寄存器内容有效标志位。该位为“1”时,表示芯片内部RAM和寄存器内容有效。读该寄存器后,该位将自动置“1”。

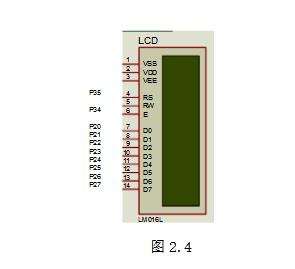

三、液晶显示器LM016L

LM016L引脚 第1脚:VSS为地电源。

第2脚:VDD接5V正电源。

第3脚:VL为液晶显示器对比度调整端,接正电源时对比度最弱,接地时对比度最高,对比度过高时会产生“鬼影”,使用时可以通过一个10K的电位器调整对比度。

第4脚:RS为寄存器选择,高电平时选择数据寄存器、低电平时选择指令寄存器。

第5脚:R/W为读写信号线,高电平时进行读操作,低电平时进行写操作。当RS和R/W共同为低电平时可以写入指令或者显示地址,当RS为低电平R/W为高电平时可以读忙信号,当RS为高电平R/W为低电平时可以写入数据。

第6脚:E端为使能端,当E端由高电平跳变成低电平时,液晶模块执行命令。

第7~14脚:D0~D7为8位双向数据线。

第15脚:背光源正极。

第16脚:背光源负极

引脚图如图2.4

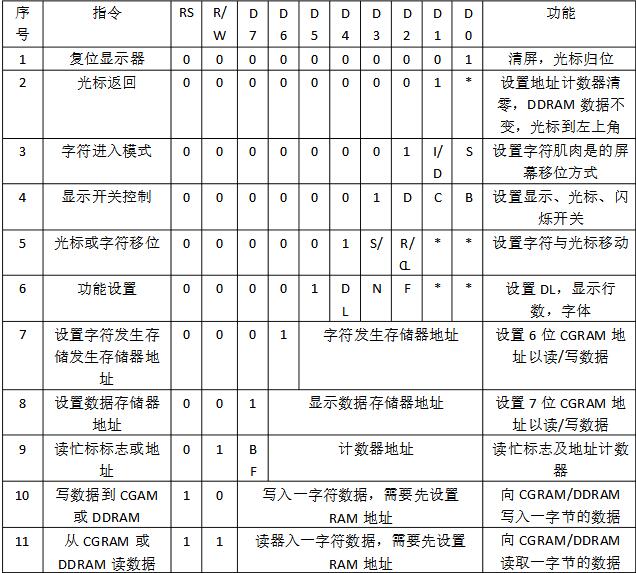

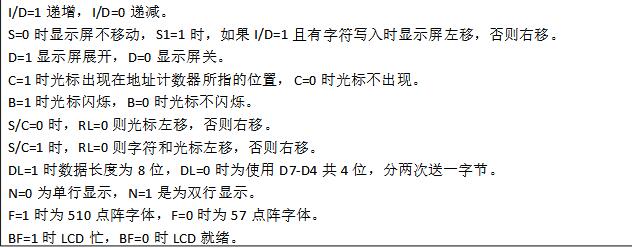

控制命令如表格2.2

硬件电路设计

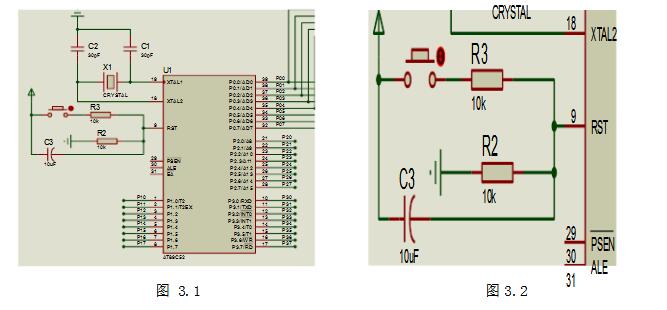

单片机最小系统

本系统以AT89C52单片机为核心,本系统选用12MHZ的晶振,使得单片机有合理的运行速度。起振电容30pF对振荡器的频率高低、振荡器的稳定性和起振的快速性影响较合适,复位电路为按键高电平复位。AT89C52单片机最小系统电路设计如图3.1所示:

复位电路

单片机复位的条件是当单片机振荡器工作时,RST引脚上出现持续两个机器周期的高电平,从而实现复位操作,使单片机回复到初始状态。上电时,考虑到振荡器有一定的起振时间,RST引脚上高电平必须持续10ms以上才能保证有效复位。 STC89C52的复位是由外部的复位电路来实现的。电路图如图3.2。

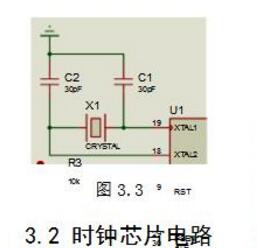

晶振电路

晶振的作用是为系统提供基本的时钟信号。晶振电路中接在晶振旁的两个电容,叫负载电容。一般单片机的晶振工作于并联谐振状态,也可以理解为谐振电容的一部分。电容值无严格要求,但电容取值对振荡频率输出的稳定性、大小、振荡电路起振速度有少许影响,C2、C3可在30pF时振荡器有较高的频率稳定性电路图如图3.3。

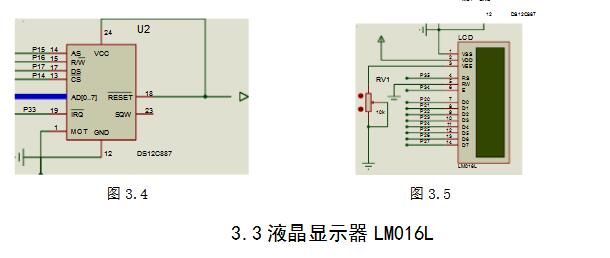

本系统采用DS12C887时钟芯片定时及计时功能,DS12C887时钟芯片共需要13条信号线。GND、 VCC:直流电源,其中VCC接+5V输入,GND接地,当VCC输入为+5V时,用户可以访问DS12C887内RAM中的数据,并可对其进行读、写操作;当VCC的输入小于+4.25V时,禁止用户对内部RAM进行读、写操作,此时用户不能正确获取芯片内的时间信息;当VCC的输入小于+3V时,DS12C887会自动将电源发换到内部自带的锂电池上,以保证内部的电路能够正常工作 MOT:模式选择脚。SQW:方波输出脚,当供电电压VCC大于4.25V时,SQW脚可进行方波输出。AD0~AD7:复用地址数据总线,该总线采用分时复用技术,在总线周期的前半部分,出现在AD0~AD7上的是地址信息,可用以选通DS12C887内的RAM,总线周期的后半部分出现在AD0~AD7上的数据信息 AS:地址选通输入脚。DS/RD:数据选择或读输入脚,该引脚有两种工作模式,当MOT接VCC时,选用Motorola工作模式,在这种工作模式中,每个总线周期的后一部分的DS为高电平。

在读操作中,DS的上升沿使DS12C887将内部数据送往总线AD0~AD7上,以供外部读取在写操作中,DS的下降沿将使总线 AD0~AD7上的数据锁存在DS12C887中。当MOT接GND时,选用Intel工作模式,在该模式中,该引脚是读允许输入脚 R/W:读/写输入端,该管脚也有2种工作模式,当MOT接VCC时,R/W工作在Motorola模式CS:片选输入,低电平有效 IRQ:中断请求输入,低电平有效,该脚有效对DS12C887内的时钟、日历和RAM中的内容没有任何影响,仅内部的控制寄存器有影响,在典型的应用中,RESET可以接VCC,这样可以保证DS12C887在掉电时,其内部控制寄存器不受影响。

DS12C887电路如图3.4所示:

液晶显示器LM016L的VSS脚接地,VDD脚接电源,VEE脚接一可变电阻接地,RS脚接单片机P3.5脚,E脚接单片机P3.4脚,D0至D7脚接单片机的P2.0至P2.7脚。液晶显示器LM016L电路图如图3.5。

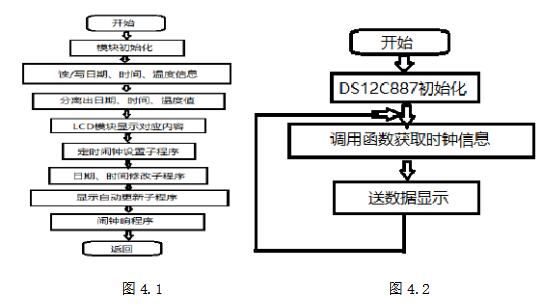

软件体统设计

主程序流程图如图4.1

DS12C887程序流程图如图4.2。

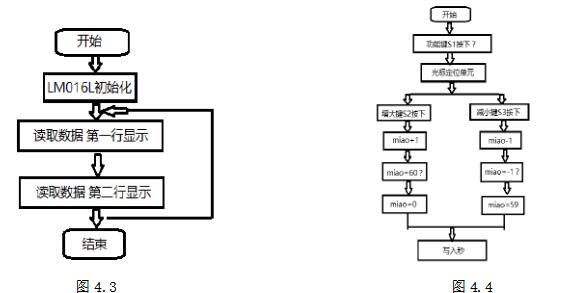

LM016L程序流程图如图4.3

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。