引言

电缆故障是通信行业中的常见故障,电缆测距是排除故障的前提条件,准确的电缆测距可以缩短发现故障点的时间,利于快速排除故障,减少损失。窄脉冲时域反射仪利用时域反射技术TDR(Time-Domain Reflectometry)测定电缆断点位置,它可以同时检测出同轴传输系统中多个不连续点的位置、性质和大小。为了实时高效地处理测试数据,多次重复信号的采集显得尤为重要。当对高频信号进行记录测量时,由于所需采样速率较高,传统的数据采集已经不能满足系统要求,本文介绍的单路多次高速数据采集方案硬件结构简单,成本低廉,能够有效满足系统设计要求。

1 系统设计背景的脉冲波型特点和处理要求

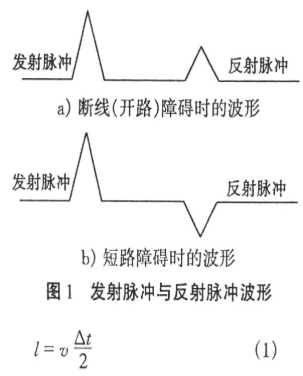

根据电磁波理论,电缆即为传输线,假若在电缆的一端发送一探测脉冲,它就会沿着电缆进行传输,当电缆线路发生障碍时,会造成阻抗不匹配,电磁波会在障碍点产生反射。在发射端由测量仪器将发送脉冲和反射脉冲波形记录下来。实际测试中具体障碍的波形有所差异:断线(开路)障碍反射脉冲与发射脉冲极性相同,而短路、混线障碍的反射脉冲与发射脉冲极性相反。波形如图l所示。

其中:v为脉冲波在电缆中的传输速度;L为电缆故障点与脉冲波送入端的距离。

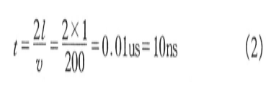

由以上分析可知,在对同一个固定障碍的线路上多次送入同一脉冲电压,其反射脉冲将f司样地在同一位置多次出现。高速数据采集系统把信号接收电路送来的模拟信号变为数字信号,对数字信号进行取点抽样,转换成数字量进行存储。仪器要求的分辨率较高,要实现1m的测距分辨率,在波速200m/us的情况下,有

即要求抽样的时间分辨率为10ns,对应的数据采集系统频率要求高达100MHz。

2 硬件设计

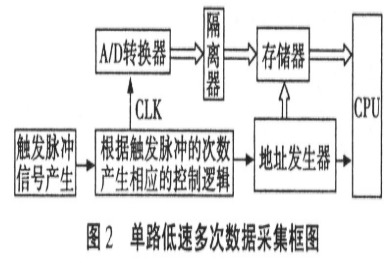

采集系统的硬件电路由CPU、A/D转换器、隔离器、存储器、地址发生器及相应的控制逻辑组成,其结构如图2所示。

脉冲波形产生和反射波形的形成,在同一测试电缆线上是多次可重复出现的,只要发射脉冲产生一次,反射脉冲就会产生一次,而且波形是相似的,当要求对波形进行100MHz的数据采集时,只要使用转换速率为25MHz的A/D转换器进行四次采集转换,每次的间隔是10ns就可以达到lOOMHz的时间分辨的效果,因此可以采用该方案进行数据采集,将系统设计的成本降到最低,满足电缆测试的高精度。

2.1 主要元器件的选择

由于单片机价格低廉,功能优越,因此,CPU使用ATB9C5l,它的指令系统与MCS-51完全兼容。为了用最低的价格获得高的存储深度,有最高的(单位速度×单位存储深度)/价格比,本设计选用8位128k容量的高性能COMS静态存储器CY7C109/CY7C1009,将存储器的地址端A0~A16对应地连接到逻辑控制电路中生成的地址信号QO~Q16上,将使能端和写有效端给单片机和控制逻辑进行控制,就可以进行对应的存储数据和读取数据操作。系统中最高的采样频率为25MHz,为了实现这样的高速采集,我们选择了TI公司的A/D转换器TLC5540,其最高采样速率可以达到40MHz。

2.2 单片机及其控制设计

单片机控制部分包括系统清零和读出数据,其主要作用是:①负责A/D转换过程的启动及完成控制;②对自动存储于存储器内的采集数据进行处理。其中Pl口做数据线,P0.0为系统清零位(包括地址以及控制逻辑部分),P0.1控制A/D与存储器的连接和断开,P0.2为采集完成位,P0.3读出数据地址信号控制,P0.4完成对存储器的读写控制。单片机首先控制A/D直接和存储器连接,接着给出系统清零信号,将地址和控制逻辑中的计数器清零,等待触发脉冲的到来。开始数据采集后,单片机查询采集是否完成,采集完成后,系统再一次清零,断开A/D和存储器的连接,控制地址发生器将存储在里面的数据读出,一次采集就完成了。

2.3 专用控制逻辑的设计及其CPLD实现

窄脉冲时域反射仪要求的分辨率较高,所以要求的采样频率相当高,例如要实现1m的测距分辨率,在波速200m/ns的情况下,要求波形抽样的时间分辨率约为10ns,对应的数据采集频率达100MHz。

逻辑控制要实现对一固定波形多次采样并进行波形拼凑,实现高速数据采集电路,即将需一次完成的100MHz高速采样转换为相应的较低频率的多次采样,将各次采样的结果进行重新组合,以拼凑出一个完整的100MHz采样波形。系统的实际数据采集速度是25MHz,采样时间间隔40ns,每完成一次波形测试,仪器要连续发射四次脉冲,数据采集电路起动四次,由于障碍点是固定的,每次发射脉冲时,仪器接收到的脉冲反射波形是相似的,只不过发射脉冲的时刻与起动采样的时刻延时分别从0ns依次以10ns的间隔增加到40ns。

本设计选用CPLD器件MAX7128S实现对高速数据采集系统的控制,硬件框图如图3所示。

虚线框内的是硬件逻辑控制模块,该模块可以完成我们所设计的高速数据采集所需的A/D转换器和存储器的控制信号。

2.3.1 控制逻辑的实现

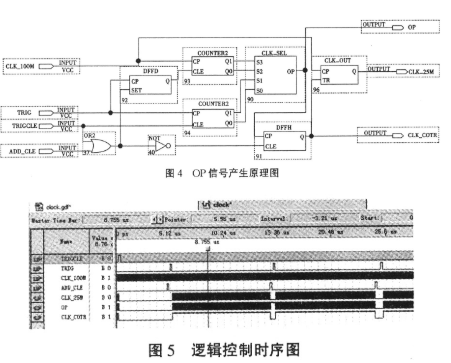

高速数据采集控制逻辑的实现主要是通过两个两位的计数器来实现的,连接TRIG(触发启动信号)的计数器(启动计数器)是判断当前是第几个脉冲,它的状态过程是:00→0l→10→ll,连接100MHz晶体振荡器的计数器(晶振计数器)来统计10ns的个数,就是说当连接触发启动信号的计数器从00→0l时,晶振计数器是00状态,这时后面的状态选择输出一个由低到高的跃变OP,控制后面25MHz数据采集开始,当启动计数器又有一个触发过来,它就从0l→10,这时晶振计数器就开始从00→0l,也就是统计一个10ns,统计完了以后,后面的状态选择又输出一个由低到高的跃变OP,开始25MHz数据采集。以后依次类推,分别是延迟20ns和30ns开始数据采集。

原理图如图4所示。

2.3.2 地址的生成

在逻辑控制设计完成后,将最后得到的25MHz的时钟输入17位计数器,每次上升沿到来,地址加1,生成的地址信号使得采集的信号存入对应的地址单元。使用Q9位是为了让输出端可以产生低电平,从而在采集的数据到达所需个数时有一个上升沿来触发其所控制的触发器,使得数据采集暂停,等待下一次采集;12作反馈,它指示的是数据采集到了4k,通过它进行反馈,用它停止A/D芯片的工作,同时将地址计数器清零,准备数据读出;最后,存储够了4k的数据,AD_0E输出高电平,用于控制A/D芯片和内部地址计数器,可以看到地址计数器在数据采集到达4K后也清零,在初始的位置等待数据的读出。系统控制原理图如图6所示。系统仿真结果(仿真图略)表明,该设计可以满足本系统要求。

3 总结

本系统是一种在单片机控制下完全靠硬件通过多次低速数据采集,然后进行波形拼凑,实现达到100MHz频率的高速数据采集与存储的系统,采集数据最多可达到128k,具有硬件成本低廉,性能价格比较高的优点,该系统的数据采样频率完全不受单片机速度的影响,而只取决于所选用的A/D转换电路的速度和控制逻辑的设计,其测量结果准确度高,对温度、湿度等环境指标要求不高,环境实用性强,在生产实践中可有效解决电缆断点测定的难题。