台积电:2nm 制程 2025 年量产,N3P 2024 年下半年量产

美国当地时间 4 月 26 日,台积电在美国加州圣塔克拉拉市举办北美技术论坛,公布了其 3nm 工艺的最新进展和路线图。其中,最引人关注的是 N3X 工艺,将在 2025 年投入量产,为高性能计算(HPC)领域提供最强的芯片制造能力。

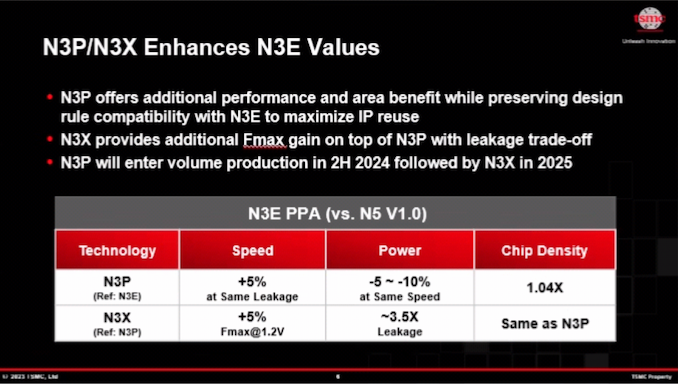

从台积电官方获悉,台积电的 3nm 工艺家族包括四个版本,分别是基础的 N3、成本优化的 N3E、性能提升的 N3P 和高压耐受的 N3X。其中,N3E 和 N3P 都是基于 N3 的光学缩小版,可以降低复杂度和成本,同时提高性能和晶体管密度。而 N3X 则是专为 HPC 领域设计的工艺,可以支持更高的电压和频率,从而实现更强的计算能力。

根据台积电的数据,与 5nm 工艺相比,N3E 可以在相同频率下降低 32% 的功耗,或者在相同功耗下提高 18% 的性能。而相较于 N3E,N3P 则可以在相同功耗下提高 5% 的性能,或者在相同频率下降低 5%~10% 的功耗。同时,N3P 还可以将晶体管密度提高 4%,达到 1.7 倍于 5nm 工艺的水平。

而 N3X 则是台积电 3nm 工艺家族中最强悍的版本,它可以在相同功耗下比 N3P 提高 5% 的性能,达到 1.2 伏特以上的电压水平。这对于一个 3nm 级别的工艺来说是非常极端的,也意味着会有很高的功耗和发热问题。因此,这个工艺只适合用于 HPC 级需要极致性能的处理器,并且需要芯片设计者采取有效的措施来控制温度和功耗。

台积电表示,N3E 将在 2023 年下半年开始量产,而 N3P 和 N3X 则分别在 2024 年下半年和 2025 年投入量产。这些工艺都将采用 FinFET 结构,也就是金属氧化物半导体场效应晶体管(MOSFET)结构。这种结构已经被台积电使用了多年,并且有着成熟和稳定的特点。

不过,在 2nm 级别以下,台积电将采用新型的 GAAFET 结构,也就是门全包围场效应晶体管(Gate-All-Around FET)结构。这种结构可以进一步提高晶体管密度和性能,并且降低功耗和泄漏。台积电称,2 纳米制程在良品率和元件效能进展良好,将如期于 2025 年量产。台积电介绍称,相较于 N3E 制程技术,2 纳米在相同功耗下,速度最快将可增加 15%;在相同速度下,功耗最多可降低 30%,同时晶片密度增加逾 15%。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。