索尼CMOS大升级,完爆竞争对手

版权声明:本文内容来自cnbeta,如您觉得不合适,请与我们联系,谢谢。

随着工程和制造水平的日新月异,我们得以在更小的尺寸里放下更多的东西,智能手机就是一个极具代表性的例子。虽然小巧,但其处理性能已经与许多入门级笔记本相当。另一方面,其摄像头传感器也取得了长足进步,但在像素数朝着几千万普及、以及 4K 视频录制的巨量数据需求下,影像处理器(ISP)也遇到了瓶颈压力。

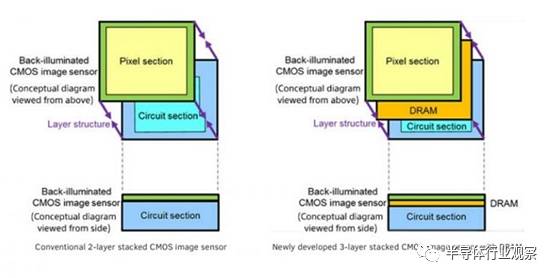

好消息是,索尼已经将相机传感器技术提升到了新的水平。在其最新披露的面向智能机的 3 层 BSI(背照式)CMOS 传感器设计中,我们发现它已经内嵌了 DRAM 缓存。

随机存储器(RAM)的速度很快,但也有着易失的缺点,因此其主要作为存储设备和处理器之间的数据枢纽。

DRAM 被嵌在了传感器的像素层与电路层之间

但是现在,索尼将动态随机存取器(DRAM)的优势,用到了提升影像传感器的速度上。不仅如此,它还极大地压榨了自身所占用的空间。

这一设计的原理是,RAM 可以加快影像传感器的数据读出(虽然 RAM 是最快的数据存储 / 访问类型之一,但成本也属于大头)。

ISP 读速快的好处之一,是更少的失真(上图左为 1/30s,右为 1/120s)

作为一个“等候区”,DRAM 可以将数据快速传递给(运行速度稍慢的)处理器,1/120s 内即可记录 1930 万像素的信息(对照组需要 1/30s 才能完成)。

除了静态拍摄的提升,新技术也能够以高达 1000 fps 的帧率,录制下 1920×1080(全高清)分辨率的视频。

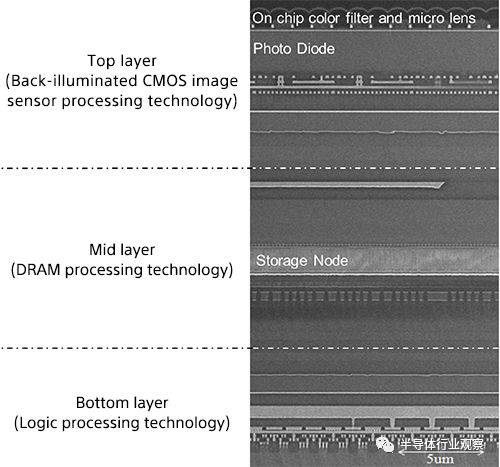

带 DRAM 的 3 层 堆栈式 CMOS 影像传感器剖面图:

PS:传感器物理像素为 2120 万,能够录制 4K @ 60 fps(或者 1080p @ 240 fps)的视频。

传感器中嵌入的 DRAM 容量为 1 Gigabit(似为 1000 进制),换算后约为 125 MB(似为 1024 进制)。

索尼暂未透露首批搭载该传感器的智能机的上市时间,但今年下半年发布的 Xperia 旗舰机型有望第一个吃到螃蟹。

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。