1、TI TVC系列(转换钳位电压)

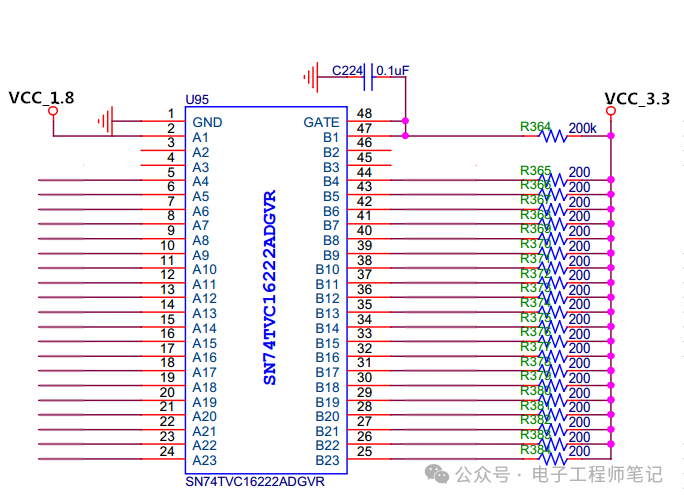

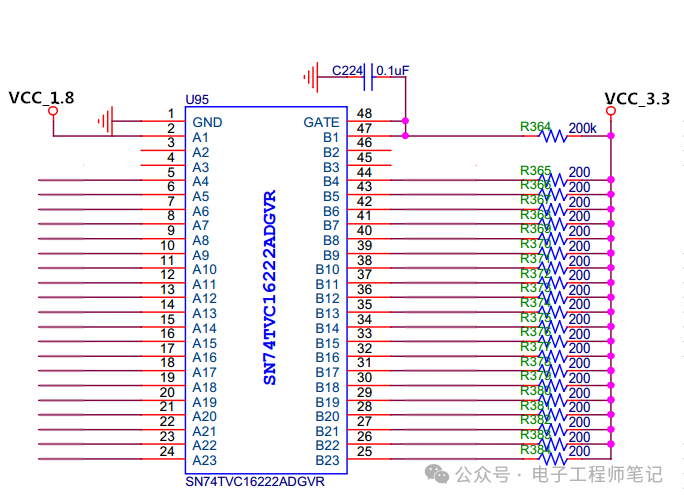

利用TI的22通道电平钳制芯片SN74TVC16222A进行电平转换,优点是速率可以做快一些。

1.1、TVC原理

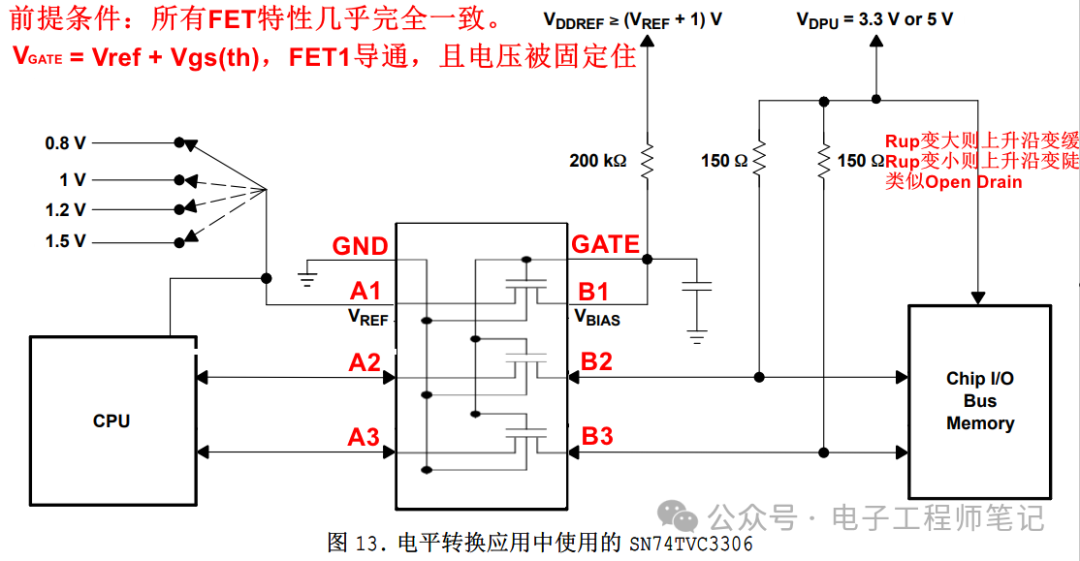

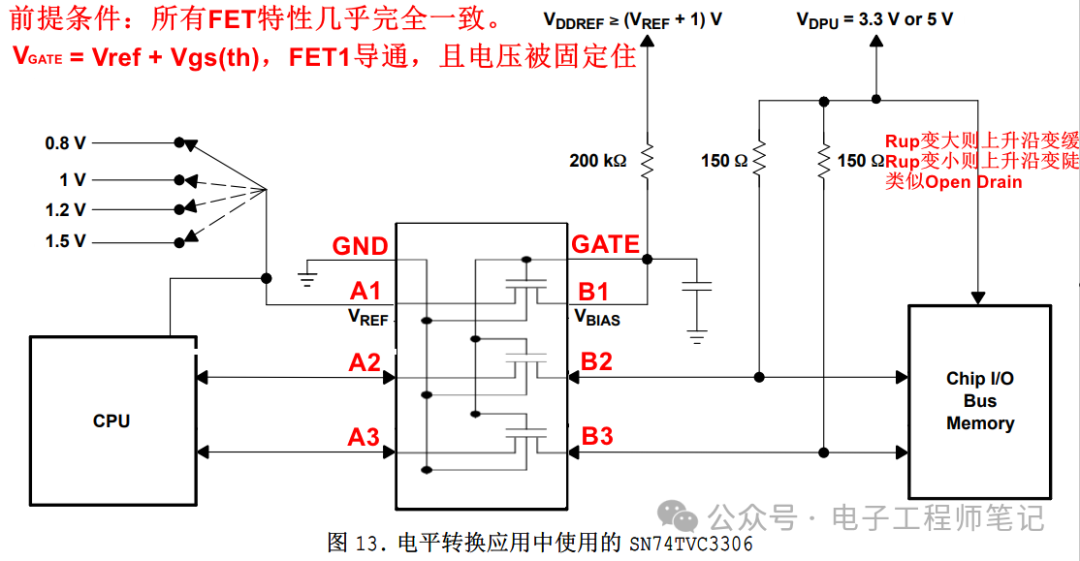

这些TVC器件可用于晶体管阵列转换。器件

不需要方向控制信号

。每个TVC器件包含一个N沟道导通晶体管阵列,它们的门在内部连接在一起。

在转换应用中,将连接其中一个 FET 作为参考晶体管,其他晶体管导通晶体管。

每个导通晶体管的低端上的最大正电压限制由参考晶体管设置的电压

。晶体管中的所有晶体管电气特性相同;因此它们中的

任何一个都可用于参考晶体管

。晶体管是廉价制造的,且 I/O 信号是通过每个 FET 的,因此每个端口的任一端口连线均可用于低压端。参考晶体管的漏极必须经过一个电阻后再连接到 VDDREF,

VREF必须低于或等于 (VBIAS - 1)

以便将参考晶体管偏置到导通状态。参考晶体管的偏置连接到它的漏极以便使晶体管处于导通

状态。

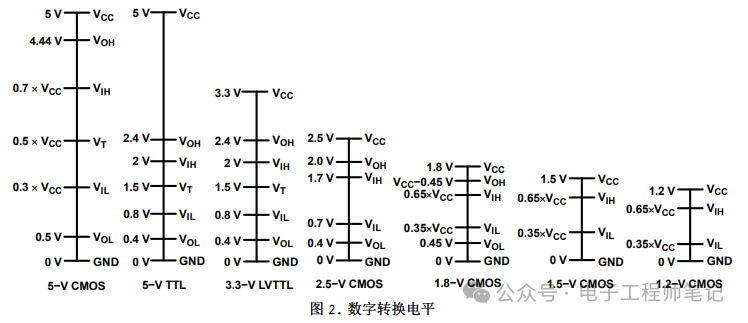

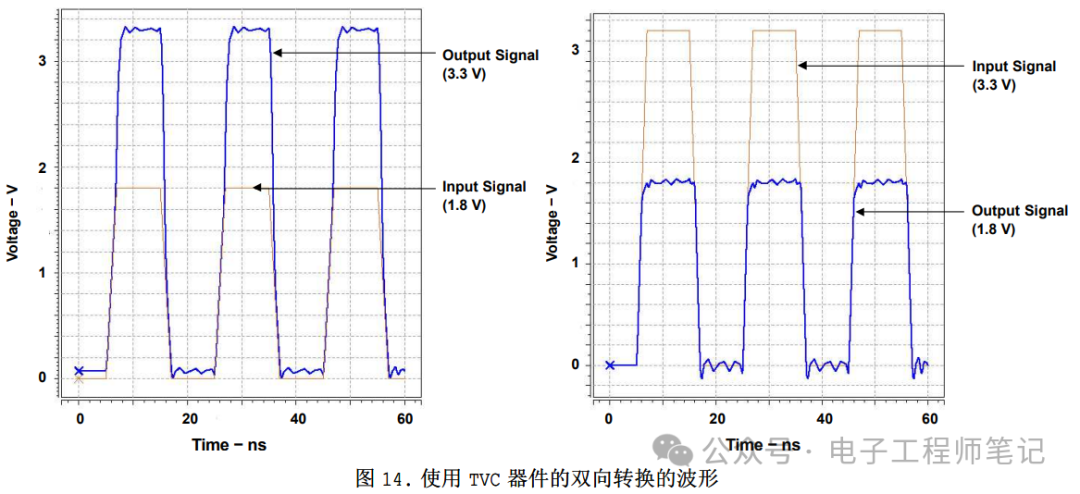

A端(低电压)VREF设置为等于CPU的I/O电压电平,而VDPU设置为B端(高电压)上所需的电压电平。

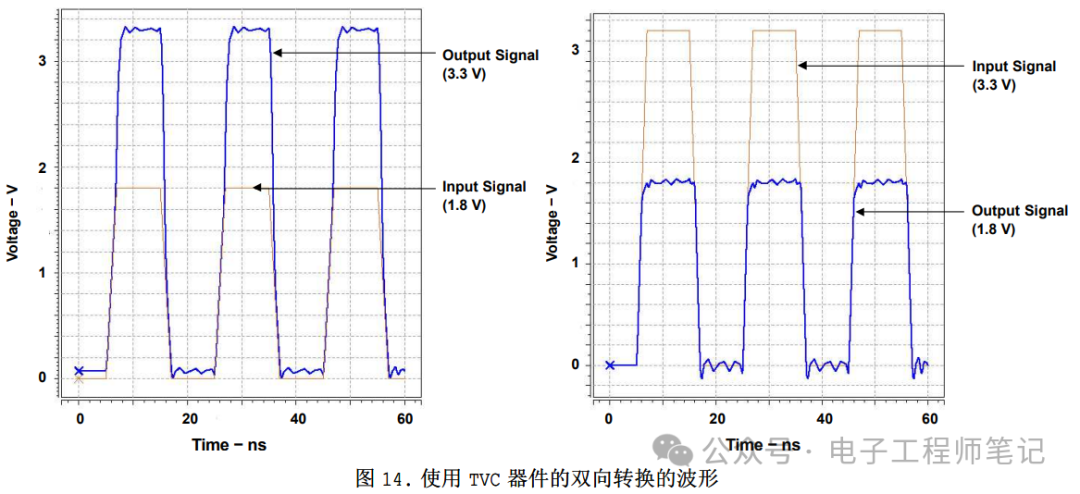

当从B端上升转换到A端时,A端上的电压被钳位在VREF,因为VGATE被固定住了,假设VA2大于VREF,则FET关闭,所以VA2只能被钳位在VREF。

当从A2(A3)上升转换至B2(B3)时,在A端上的电压达到VREF时,A2(A3)与B2(B3)之间的导通

晶体管关闭

,且B2(B3)上的电压通过150Ω上拉电阻上拉至VDPU(类似Open Drain)。

上个例子,VDDREF的200KΩ上拉电阻会影响所有晶体管的驱动能力,如果要求上升沿/下降沿比较陡,则减小这个上拉电阻?

疑问:如果A端IO电平不足VREF电压,则B端电压升不起来,那么设计的时候VREF就不能是IO的最高输出电压,应该是A端IO的VOH?

SN74TVC3306 数据表

描述:

PCA9306(属于TVC)Datasheet

也有关于MOS管上拉电阻和Ibias选择的一些描述。

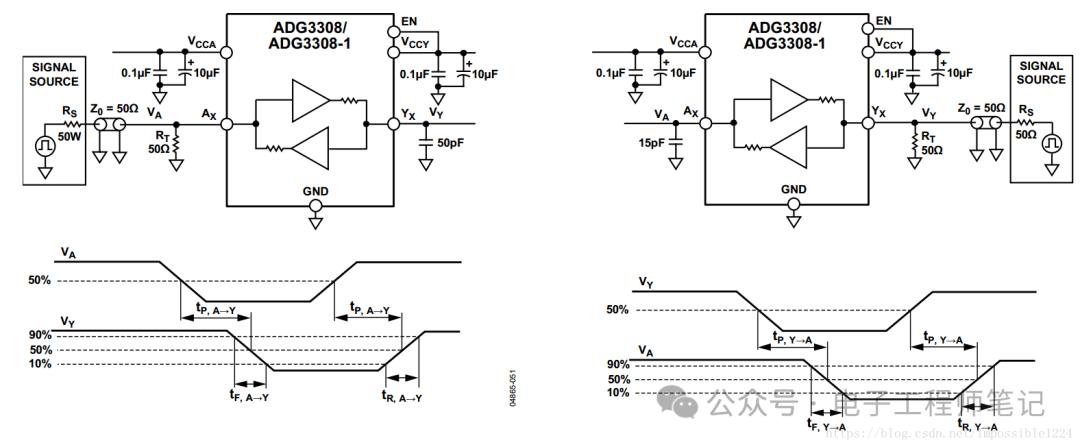

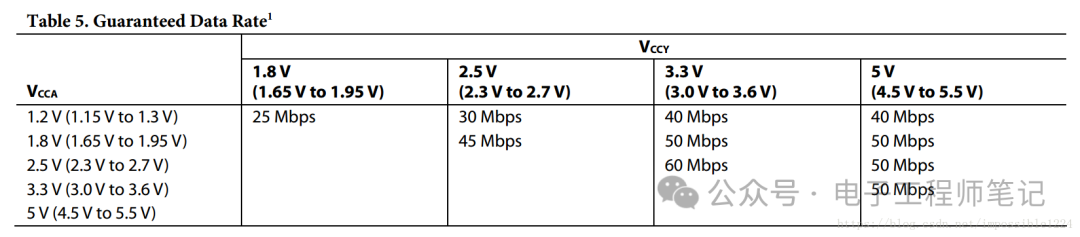

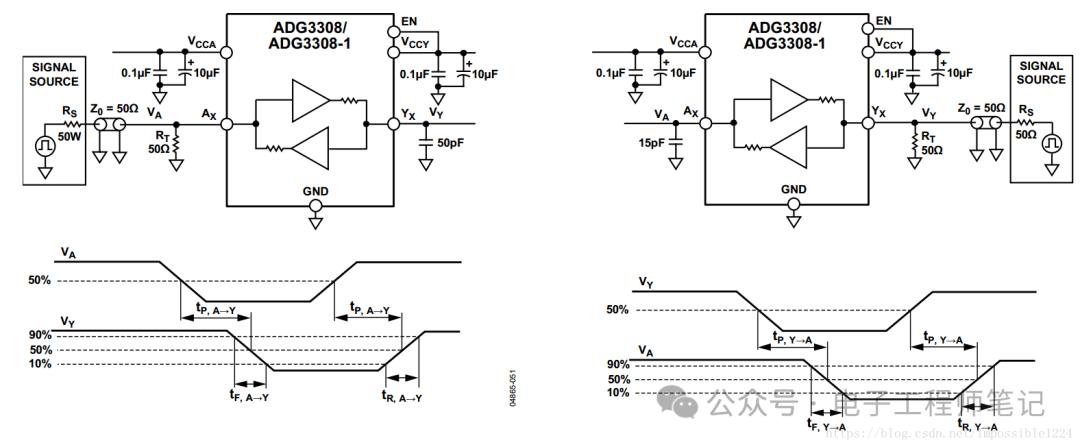

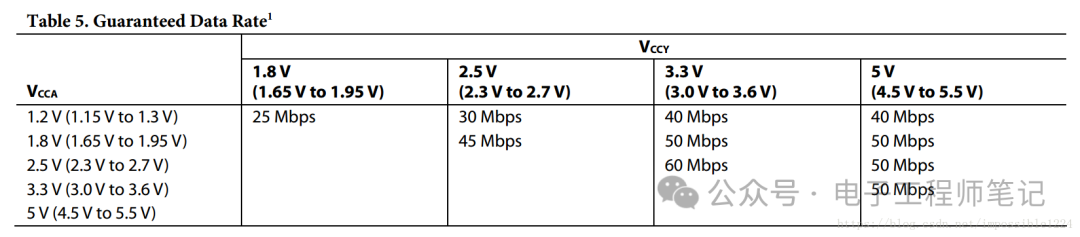

利用AD的8通道真空液体转换器ADG3308,速度可以达到很多。