AXI总线已经是AMBA总线中最常见,使用最频繁的总线,并且没有之一。

可以说AXI总线已经成为了片上总线中最重要的协议,本篇文章打算花一些篇幅,帮大家总结一下AXI总线的学习重点、学习难点,以帮助大家更好更快的掌握AXI总线。

一、什么是总线(Bus)

1.1、什么是片上总线

要理解AXI总线,首先要理解什么是总线。大家刚接触总线的时候千万不要纠结于具体的概念,可以简单的理解成几根线按照规定的方式通信即可。

-

对于芯片设计而言,可以简单的理解,总线就是一组通信规范,允许系统中不同组件之间进行传输。

-

AMBA总线,包括AXI属于片上总线(On-chip Bus),它用于芯片内部中各个模块之间的通信。

总线可以简单的分为设备之间的总线和片上总线。其中设备之间的总线有时候也可以叫做传输接口,比如最常见的UART串口,硬盘的PCIE、SATA接口。显示器的HDMI接口,电脑的USB、Type-C接口等。这些传输接口往往更注重设备的电气特性、稳定性。这是另外一套大的话题,后面可以单独开个专题讲一些常见的传输接口。

而另外一种总线就是我们今天要聊的话题,片上总线。所谓片上总线。顾名思义,就是同一个芯片上(一般指SoC系统),各个模块(IP核)之间的数据通信方式。比如大家都设计好了自己的模块,要集成在一个芯片上。如果都能满足类似的通信方式或者接口,那集成起来就非常的方便,其实片上总线的规范制定也是考虑到可扩展性。一般片上总线要满足以下的标准:

-

对频率和数据吞吐量有较高的要求

-

扩展性强,能够很方便扩展更多模块

-

常见的片上总线有Wishbone(部分MIPS芯片使用)、Avalon(Altera芯片会使用)、Tilelink(UCB用在其RISC-V项目中)、AMBA(绝大多数SoC会使用)。

1.2、总线中常见的名词和组件

接下来我们谈谈总线中常见的组件。以下说的这些概念和机制对任何常见的片上总线都是成立的。

首先是Master和Slave。前面已经说到了,总线是用来进行数据传输用的,那么既然是数据传输,必然有发起方和接收方。一般我们称之为Master和Slave。

对于命令而言,是由Master发给Slave,而数据可以是双向传输的。比如可以是Master写给Slave,也可以是Slave返回数据给Master,甚至还可以是两者都有。Master和Slave的区分关键在于命令(这次传输)是谁发起的。

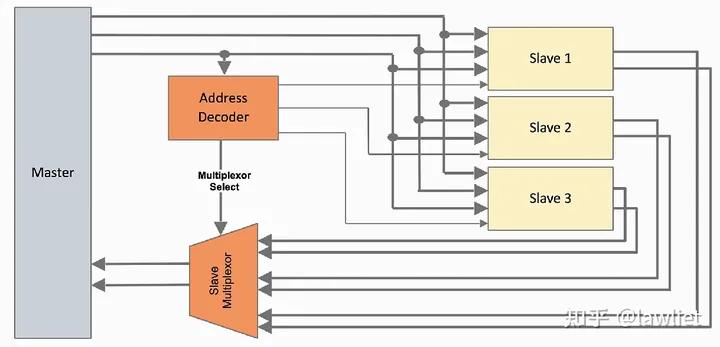

除了Master和Slave,总线中一般还包括哪些组件呢?比如有多个Slave的时候,那么自然要确定你的命令是发给哪个Slave的,这个时候我们就需要地址译码器。而当Slave返回数据的时候,Master需要知道是哪个Slave回的数据,因此还需要MUX选择器。

如果我们有多个Master的时候,就需要仲裁器来选择到底是哪个Master可以发起某次通信,上述的这一套仲裁译码等机制,可以组合在一起,构成片上互联(Interconnect)。所谓的互联,可以理解为把所有模块的通信集成在一起。基于互联系统可以完成Master对Slave的访问而不用在乎互联的内部实现细节(对于IP设计者而言)。

1.3、什么是AMBA总线

AMBA全称Advanced Microcontroller Bus Architecture。即高级微控制总线架构。首先高级是针对那个年代而言的,其实也没有多高级。然后是Microcontroller,微控制器,可以知道它最初是用在微控制器上,实际上就是ARM自己的处理器上。然后Bus Architecture,即总线架构。

-

AMBA协议是一个公开标准的片上芯片互联协议。(AMBA没有版权费,大家都可以使用,协议都是公开的)

-

提供接口标准使IP可以服用(IP reuse,加速设计和集成)

-

移动领域和物联网领域使用最广泛的片上总线,没有之一(桌面领域我不清楚)

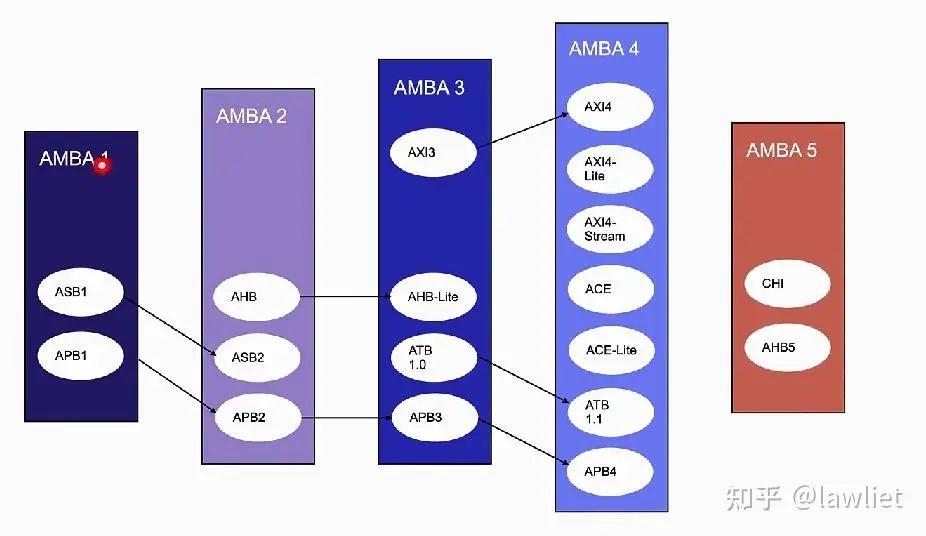

然后我们看一下AMBA的发展历史,对于大家来说,学习APB、AHB和AXI就行。我相信如果大家已经学习到ACE和CHI了,也不用看我这篇文章了。而最最重要的就是AXI。

二、AXI总线的学习路线

大家有了总线的基本概念以后,便可以开始学习AXI总线,以下是我推荐的AXI总线的学习路线。

2.1、第一阶段:带着问题去看源文档

学习AXI总线之前,首先我们要知道为什么会出现AXI总线,即它设计之初是为了解决什么问题的,没有AXI总线会怎么样?

AXI总线是ARM公司在其第三代AMBA中推出的,称之为AXI3.0,有时候也可以叫做AXI1.0。其设计的目的是针对高性能、高时钟频率的系统设计,用于在这些场景替代AHB协议的。针对这一特点,我们可以思考一下,为什么AXI的性能就高了?为什么AXI可以跑到较高的时钟频率?

带着这一问题去看协议,就可以明白AXI提高性能最主要的因素是因为,AXI是读写通道分离的,其作为全双工的协议,自然比AHB这样的半双工协议快,此外AXI是基于握手机制的,并且通道之间的握手没有1T cycle delay的要求。因此这么多复杂的东西不需要一个时钟周期就全部算完,可以插入寄存器逻辑,自然可以提高主频。

类似的点还有很多,我帮大家总结了一下,大家可以先带着这些问题去思考,然后去看AXI协议,知道这些信号设计的目的是什么,即使协议看不太明白,也不至于不清楚为什么要有这个东西。这种感觉就像之前学数学课,即使你看不太明白推导,但也不至于完全不清楚为什么要有这个东西。

-

如何提升主频以及保证数据安全?->AXI的握手机制

-

数据不是顺序回来的怎么办、想多发几个命令出去怎么办?->AXI的Out of Order、Outstanding、ID机制

-

现代多核处理器中的数据一致性如何保证?->AXI的原子访问机制和Response相关信号

-

非对齐访问如何实现?->AXI支持非对齐访问

-

现代处理器中往往有Cache和Buffer,AXI怎么支持?->AXI的Cache信号

-

现代处理器往往有特权访问、安全访问等机制,AXI如何支持?->AXI的PROT信号

大家带着这些问题,然后去看文档,边看边思考。理解AXI为什么要设计这些信号,先不用在意实现细节,具体哪些比特代表啥,先知道有这么一回事就行。并且边看边补充一些计算机组成原理和操作系统相关的知识,这是第一阶段。

2.2、第二阶段:自己动手设计简单的AXI IP模块

在完成第一阶段以后,基本都会对AXI协议有个初步的了解,但毕竟纸上得来终觉浅,绝知此事要躬行。完成AXI协议的了解以后,应该自己动手去设计具有AXI接口的Master和Slave。

不一定要特别复杂。这里建议可以从最简单的AXI-lite开始,设计一个AXI-lite的从机,然后可以通过AXI-lite给它配置相应的寄存器。配置寄存器这一部分可以在TB里面完成。

然后可以设计一个相对复杂点的AXI-full的Slave,比如AXI2RAM模块,该模块可以支持突发乃至Outstanding,甚至可以支持乱序,完成该模块以后工作中再遇到AXI-Slave设计,至少心里不会虚,并且面试基本可以应付大部分问题了。

最后可以再设计一个AXI Master,从主机和从机两个不同的维度深刻理解AXI协议的通信机制,这个主机同样的也可以支持Outstanding乃至乱序。这里建议设计一个AXI DMA,非常的锻炼人。

上述的这些模块设计可以去网上如github找些开源的AXI IP,参考别人的设计理念,然后再自己动手做,毕竟能一次自己做出来,基本上是不可能的。

2.3、第三阶段:学习AXI接口验证以及AXI互联IP

首先说AXI接口验证,其实工作中大家写完了AXI的IP,并不知道是否符合AXI的通信要求,很多公司可能会用VIP,能给各种AXI的激励,然后大家根据自己IP的结果判断设计的是否合理。大家可以想一想这个VIP到底是怎么设计的,如果让你来设计,你会怎么做。

然后是AXI互联IP,前面已经说过什么是互联了,由于总线互联非常复杂并且非常重要。实际上大多数公司会采用买总线互联IP的方式。大家可以自己动手设计一个简单的互联IP,让自己设计的Master和Slave挂在上面,然后看能否建立通信,如果没问题的话,可以进一步的学习如何使用第三方IP,比如典型的NIC400。